总线技术

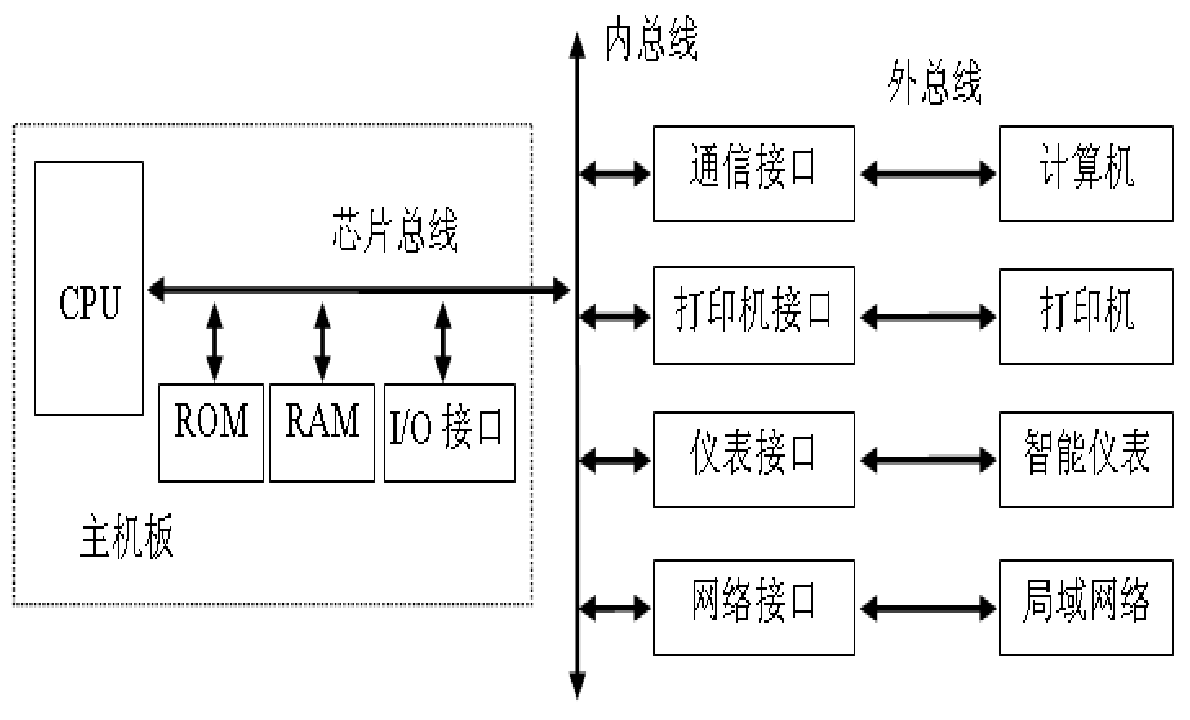

分类

- 芯片总线:

芯片级互联,大规模集成电路芯片内部,或系统中各种不同的器件连接在一起的总线,局部总线:微处理器的引脚信号,片内总线:大规模集成电路芯片内部连接 - 内总线:

模板级互联,主机内部各功能单元间连接的总线 - 外总线:微机系统与其外设或微机系统之间连接的总线

总线的数据传输

主设备(Master):控制总线完成数据传输

从设备(Slave):被动实现数据交换

总线操作

总线请求和仲裁:使用总线的主模块提出请求,总线仲裁机制确定把总线分配给请求模块寻址:主模块发出要访问的从模块的地址信息及相关命令,启动从模块数据传输:原模块发送数据,经数据总线传送到目标模块- 结束:数据、地址、状态、命令信息均从总线上撤除,让出总线

总线仲裁

- 集中仲裁:系统具有中央仲裁器(控制器),负责主模块的总线请求和分配总线的使用

- 分布仲裁:各个主模块都有自己的仲裁器和唯一的总裁号,主模块请求总线时,发送其仲裁号到共享仲裁总线,其他仲裁器比较各个主设备的仲裁号决定

同步方式

- 同步时序

- 总线操作过程由共用的总线时钟信号控制

- 优点是简单快速、适合速度相当的器件互连总线,如果速度差异较大,则速度快的必须迁就速度慢的模块,总线的响应速度由速度最慢的模块确定,从而使系统的整体性能降低,我们可以再增加一个状态信号形成半同步时序。

- 半同步时序

- 仍共用一个总线时钟信号

- 在同步时序的基础上增加了一个

等待信号WAIT,如果被控模块的速度足够快,则等待信号一直处于无效状态,如果被控模块的速度较慢,不能在规定时间内完成读写操作,被控模块就令等待模块有效,主控模块检测到被控模块等待信号有效后就等待,直到被动模块完成读写操作使等待信号变为无效,完成一个总线周期。

- 异步时序

- 异步方式也称应答方式,总线操作需要握手联络信号控制

- 传输开始伴随有启动信号

- 传输结束有一个确认信号

- 优点:操作周期可变、可以混合慢速和快速器件

传输类型

- 读数据传送:数据由从设备到主设备

- 写数据传送:数据由主设备到从设备

- 猝发传送:给出起始地址,将固定块长的数据一个接一个地从相邻地址读出或写入

- 写后读:先写后读同一个地址单元用于校验

- 读修改写:先读后写同一个地址单元,适用于共享数据保护

- 广播:一个总设备对多个从设备的写入操作

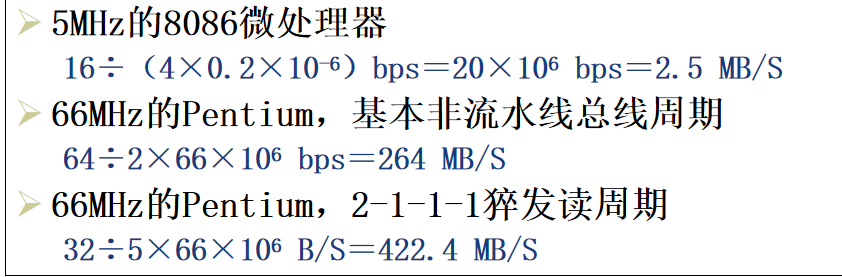

性能指标

- 总线宽度:总线同时传送的数据位数

- 总线频率:总线信号的时钟频率

- 总线带宽:单位时间传送的数据量每秒兆字节(MB/s)每秒兆位(Mb/s)或每秒位(bps)

总线信号和时序

总线按传输信号的性质可以分为三类

- 地址总线:主模块的地址输出,输入给要寻址的从模块

- 数据总线:

双向传输,在主、从模块间交换数据 - 控制总线:有输出也有输入信号,基本功能使控制存储器及I/O读写操作,还包括中断与DMA控制、总线仲裁、数据传输握手联络

总线信号

- 信号的功能:用英文单词表示

- 信号的流向:处理器的多数信号是输出到外部(地址总线)、数据总线是双向信号

- 有效方式:

- 低电平、高电平有效,上升沿、下降沿有效

- 高电平和低电平都有效:表示的功能不同

- 三态能力:高阻状态放弃对引脚的控制其他设备控制该引脚

总线时序

总线时序描述了总线信号随时间变化的规律以及总线信号间的相互关系

- 指令周期:一条指令从取指、译码到最终执行完成的过程

- 总线周期/机器周期:伴随有数据交换的总线操作

- T状态:处理器的基本工作节拍,对用

时钟周期

8086的引脚信号

地址/数据信号

- AD15~AD0:

- 地址/数据分时复用引脚,共16各引脚

- 单向输出地址总线,双向数据总线,三态输出

- A19/S6~A16/S3:

- 地址/状态分时复用引脚,4个三态输出信号

- 输出高4为地址、状态信号

- BHE*/S7:高字节允许/状态分时复用引脚,三态输出信号输出低有效表示传送高字节数据,状态信号

总线复用:同一引脚在不同时刻具有不同功能

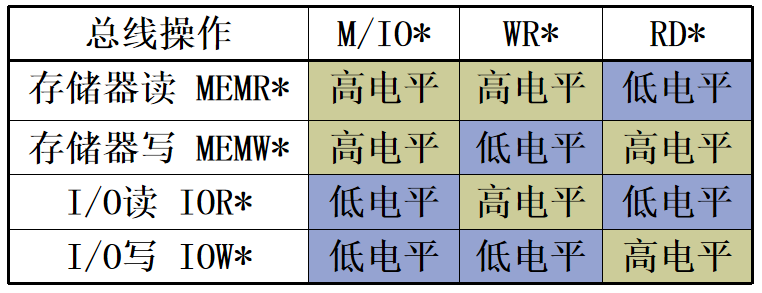

读写控制信号

基本读写引脚

- ALE:

- 地址锁存允许,三态、输出、高电平有效

- 有效时,表示复用引脚正在传送地址信号

- M/IO*

- 访问存储器或者I/O,三态、输出、高低电平均有效

- 高电平(M),表示处理器访问存储器

- 低电平时(IO*),表示处理器访问I/O端口

- WR*

- 写控制,三态、输出、低电平有效

- 有效时,表示处理器正将数据写到存储单元或I/O端口

- RD*

- 读控制,三态、输出、低电平有效

- 有效时,表示处理器正从存储单元或I/O端口读取数据

基本读写操作

- 存储器读

- 处理器从存储器读取代码或读取操作数

- 每条指令执行前都需从主存取指

- 以存储单元为源操作数的指令在执行时

- 存储器写

- 处理器向存储器写入操作数

- 以存储单元为目的操作数的指令在执行时

- I/O读

- 处理器从外设读取操作数

- 只有执行输入指令IN时才有

- I/O写

- 处理器向外设写出操作数

- 只有执行输出指令OUT时才有

同步操作引脚

处理器与外设必须实现读写操作同步,否则将出错。

READY :

- 输入信号,高电平有效表示可以进行数据读写

- 利用该信号无效请求处理器等待数据

- 处理器在进行读写前检测READY引脚

其他控制信号

除了地址总线、数据总线、基本读写控制信号处理器还有:

- 中断请求和响应信号

- 总线请求和响应信号

- 时钟信号、复位信号

- 电源Vcc

- 地线GND

中断请求和响应信号

- INTR

- 可屏蔽中断请求,高电平有效的输入信号

- 有效时表示中断请求设备向处理器申请可屏蔽中断

中断IF标志对该中断请求进行屏蔽,在进行cli关中断时,会置为IF

- INTA*

- 可屏蔽中断响应,低电平有效的输出信号

- 有效时,表示来自INTR引脚的中断请求已被处理器响应

- NMI

- 不可屏蔽中断请求,上升沿有效的输入信号

- 有效时,表示外界向CPU申请不可屏蔽中断

- 中断级别高于可屏蔽中断请求INTR

- 处理器无法在内部对其屏蔽,所以无需设计响应信号

总线请求和响应信号

- HOLD

- 总线请求,高电平有效的输入信号

- 有效时,表示其他总线主控设备正在向处理器申请总线

- HLDA

- 总线响应,高电平有效的输出信号

- 有效时,表示处理器已响应总线请求并将总线释放

- 总线释放:地址总线、数据总线及具有三态输出能力的控制总线呈现高阻状态

复位与时钟信号

- RESET

- 高电平有效

- 有效时,迫使CPU回到初始状态,无效时CPU开始工作

- CLK

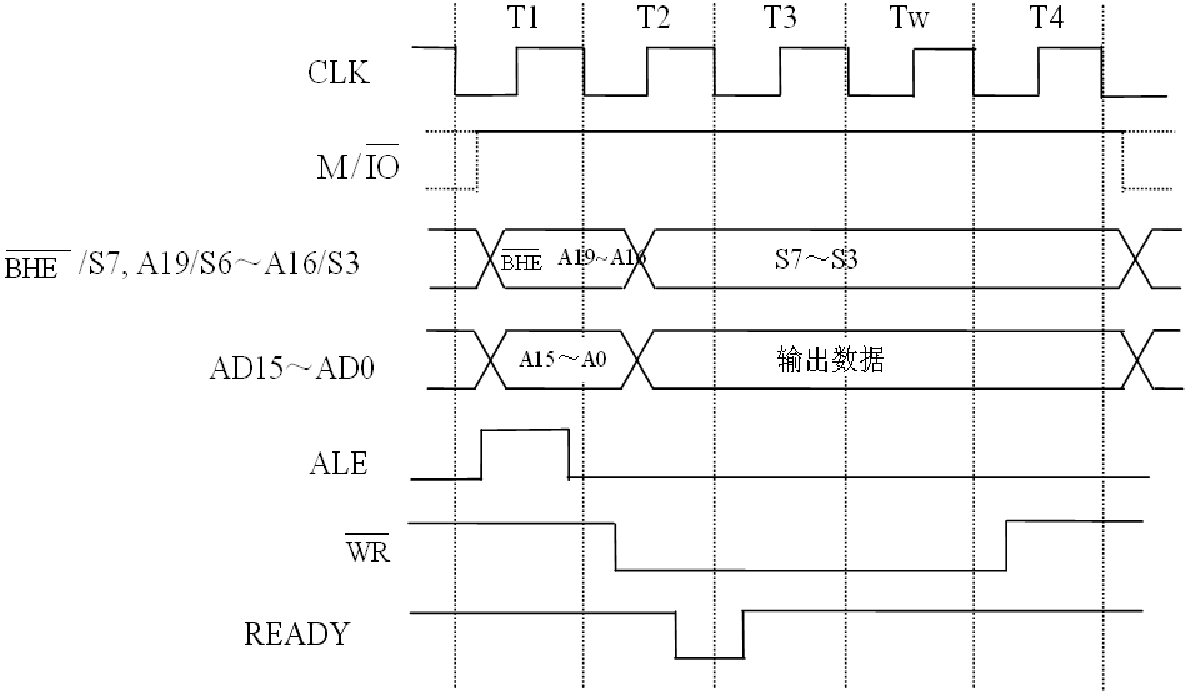

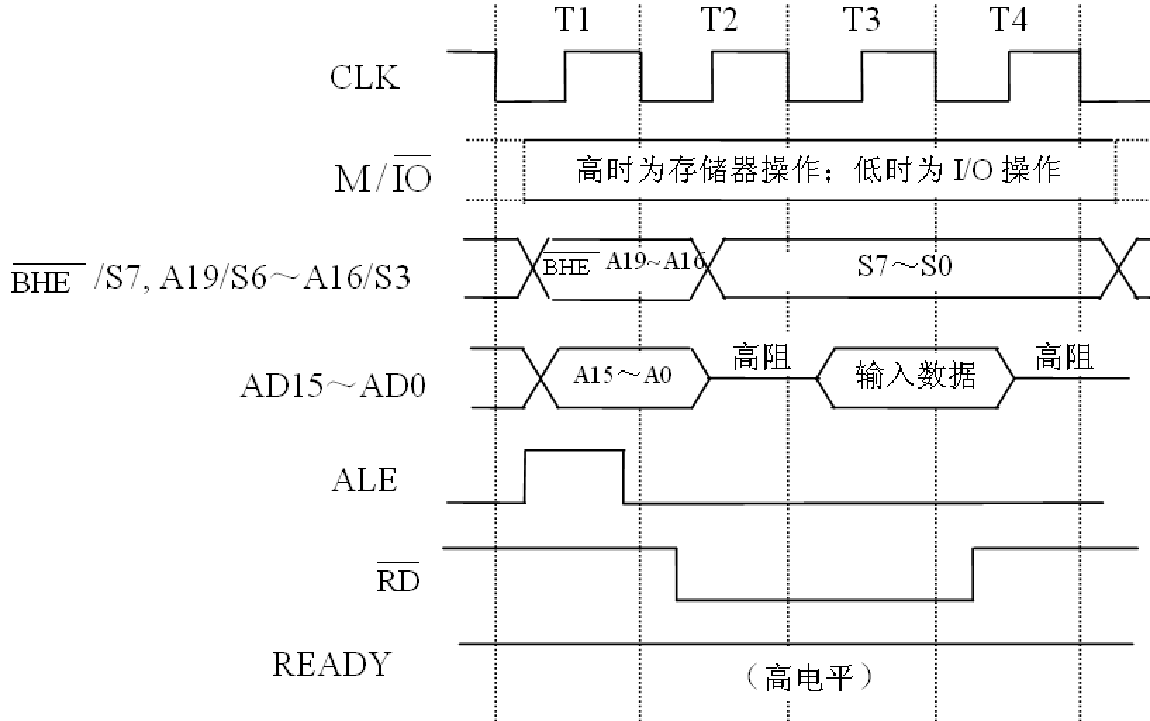

8086的总线时序

8086处理器的基本总线周期: 4个时钟周期,分别使用T1、T2、T3、T4描述

8086处理器的四个基本总线周期非常类似:齐总存储器读和IO读可以归为读总线周期、存储器写和IO写可以归为写总线周期

写总线周期

完成读存储器或IO端口的一次写操作

- \(T_1\)状态

- 输出20为存储器地址A19~A0

- M/IO*输出高电平,表示存储器操作,并一直保持到下一个总线周期

- ALE输出正脉冲,表示复用总线输出地址,利用其后沿来锁存地址数据

- \(T_2\)状态

- 输出控制信号WR*和数据\(D_{15} \quad - \quad D_0\),地址信号将被撤销

- \(T_3\)状态

- 检测数据传送是否能够完成

- 如果能够完成,则将

READY信号置高有效,反之则置为无效 - 在\(T_2\)后沿(也即\(T_3\)时钟前沿)对

READY引脚信号进行检测,如果有效进入下一个\(T_4\)状态,如果无效进入一个\(T_w\)等待状态

- \(T_4\):完成数据传送,准备过度到下一个总线周期

- \(T_w\)

- 在实际形况下,处理器的运行速度远远快于存储器和IO端口,当处理器不能在基本总线周期完成数据交换时,需要控制

READY信号为低无效 - 处理器在T3前沿检测到控制READY信号为低无效,不进入\(T_4\)状态,插入等待状态\(T_w\)

- 一个\(T_w\)状态的长度是一个时钟周期

- 在\(T_w\)的前沿,继续对

READY信号进行检测,如果READY信号无效则继续插入\(T_w\),有效就转入\(T_4\)

- 在实际形况下,处理器的运行速度远远快于存储器和IO端口,当处理器不能在基本总线周期完成数据交换时,需要控制