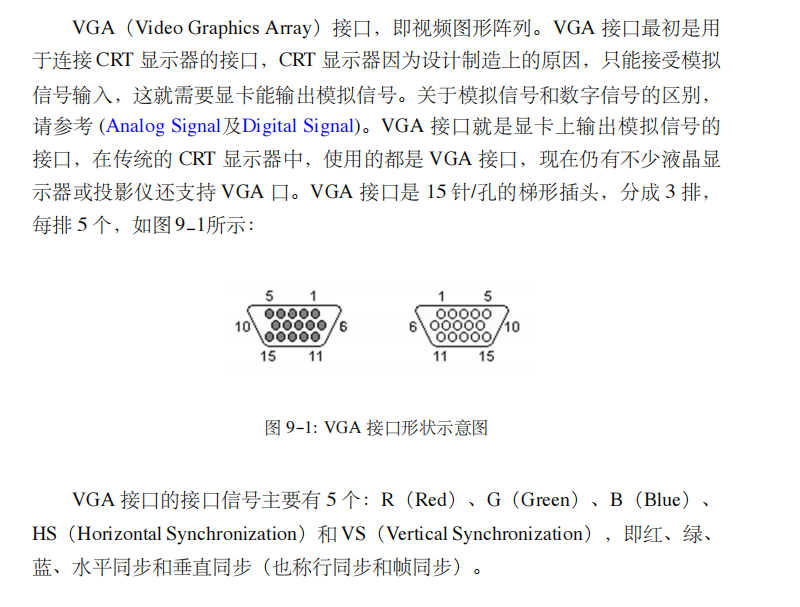

VGA简介

行消隐与列消隐

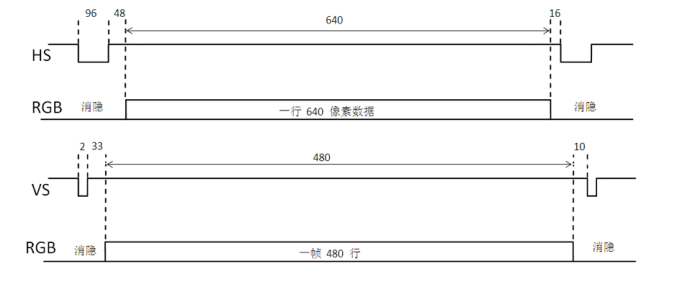

以640480的像素点为例。

所以简单而言,

一行需要640+96+48+16=800个时钟沿,

一列需要480+2+33+10=525个时钟沿,

扫描一遍需要800525=420k个时钟沿,

以60hz为例,需要420k*60=25.2M个时钟沿。

DE 10开发板信号

开发板和 ADV7123 芯片之间的接口引脚包括3组8bit的颜色信号

VGA_R[7:0], VGA_G[7:0], VGA_B[7:0],行同步信号 VGA_HS,帧同步信号

VGA_VS,VGA 时钟信号 VGA_CLK,VGA 同步(低有效)VGA_SYNC_N,

和 VGA 消隐信号(低有效)VGA_BLANK_N。

module exp9(

input CLOCK_50,

input [9:0] SW,

output VGA_BLANK_N,

output [7:0] VGA_B,

output VGA_CLK,

output [7:0] VGA_G,

output VGA_HS,

output [7:0] VGA_R,

output VGA_SYNC_N,

output VGA_VS

);

parameter h_frontporch = 96;

parameter h_active = 144;

parameter h_backporch = 784;

parameter h_total = 800;

parameter v_frontporch = 2;

parameter v_active = 35;

parameter v_backporch = 515;

parameter v_total = 525;

reg [9:0] x_cnt;

reg [9:0] y_cnt;

wire h_valid;

wire v_valid;

reg clock;//25m频率的信号

reg clock_1s;//1s频率的信号,用来作为动态图片移动的时钟

reg [23:0] vga_data[0:2]; // 上 层 模 块 提 供 的 VGA颜色数据

wire [9:0] h_addr; // 提 供 给 上 层 模 块 的 当 前 扫 描 像 素 点 坐 标

wire [9:0] v_addr;

wire hsync; // 行 同 步 和 列 同 步 信 号

wire vsync;

wire valid; //消隐信号

wire [7:0]vga_r1;

wire [7:0]vga_g1;

wire [7:0]vga_b1;

wire [7:0]vga_r2;

wire [7:0]vga_g2;

wire [7:0]vga_b2;

wire [7:0]vga_r3;

wire [7:0]vga_g3;

wire [7:0]vga_b3;

integer count_1s;

integer h_move;

integer v_move;

integer direction_h;

integer direction_v;

parameter step=10;

initial

begin

clock=0;

count_1s=0;

clock_1s=0;

h_move=0;

v_move=0;

direction_h=1;

direction_v=1;

vga_data[0] = 24'h0000ff;

vga_data[1] = 24'hff0000;

vga_data[2] = 24'h00ff00;

end

always@(posedge CLOCK_50)

clock=~clock;

always@(posedge CLOCK_50)

begin

if(count_1s==25000000)

begin

clock_1s=~clock_1s;

count_1s=0;

end

else

count_1s=count_1s+1;

end

always @(posedge SW[0] or posedge clock) // 行像 素 计数

begin

if (SW[0] == 1'b1)

x_cnt <= 1;

else

begin

if (x_cnt == h_total)

x_cnt <= 1;

else

x_cnt <= x_cnt + 10'd1;

end

end

always @(posedge SW[0] or posedge clock) // 列像 素 计数

begin

if (SW[0] == 1'b1)

y_cnt <= 1;

else

begin

if (y_cnt == v_total & x_cnt == h_total)

y_cnt <= 1;

else if (x_cnt == h_total)

y_cnt <= y_cnt + 10'd1;

end

end

// 生 成 同 步 信 号

assign hsync = (x_cnt > h_frontporch);

assign vsync = (y_cnt > v_frontporch);

// 生 成 消 隐 信 号

assign h_valid = (x_cnt > h_active) & (x_cnt <= h_backporch);

assign v_valid = (y_cnt > v_active) & (y_cnt <= v_backporch);

assign valid = h_valid & v_valid;

// 计 算 当 前 有 效 像 素 坐 标

assign h_addr = h_valid ? (x_cnt - 10'd145) : {10{1'b0}};

assign v_addr = v_valid ? (y_cnt - 10'd36) : {10{1'b0}};

// 设 置 输 出 的 颜 色 值

//产生静态条纹

assign VGA_HS=hsync;

assign VGA_VS=vsync;

assign VGA_CLK=clock;

assign VGA_BLANK_N=valid;

assign VGA_R = vga_data[v_addr/160][23:16];

assign VGA_G = vga_data[v_addr/160][15:8];

assign VGA_B = vga_data[v_addr/160][7:0];

可以根据横纵坐标改变VGA_R,VGA_G,VGA_B即可。

如果需要载入图片,需要将RGB值形成存储器,再进行读取操作等。