uart fifo

FIFO设计

first in first out,先进先出 fifo是基于RAM进行设计的 双端口RAM设计(16*8) 如果大的RAM可以调用IP RAM的关键参数:深度和宽度 module dual_ram #( parameter ADDR_WIDTH = 4, parameter RAM_WIDTH = ......

常用通讯协议(UART、RS232、RS485、IIC、SPI)简单介绍

常用通讯协议随笔 这里主要对工作学习中常见常用的通信协议进行一个整理,在需要的时候可以进行回顾,内容主要根据创客学院,所做的学习笔记加上一些比较好理解的话语,内容如有错误还请各大佬批评指正。 通讯基础 并行通讯:数据线有8条,就代表总线传输数据时一次可传输8位数据; 串行通讯:数据线只有一条,需要一 ......

STM32CubeMX教程9 USART/UART 异步通信

1、准备材料 开发板(正点原子stm32f407探索者开发板V2.4) ST-LINK/V2驱动 STM32CubeMX软件(Version 6.10.0) keil µVision5 IDE(MDK-Arm) CH340G Windows系统驱动程序(CH341SER.EXE) XCOM V2.6 ......

【全志T113】修改console uart端口

一共需要改以下几个地方 1.device/config/chips/t113/configs/mq_r/board.dts (1)修改uart端口设备树,改成你想要的端口,注意,必须是mux表上uart3对应的端口 (2) 2.device/config/chips/t113/configs/mq_ ......

18 Verilog语法_FIFO设计

软件版本:无 操作系统:WIN10 64bit 硬件平台:适用所有系列FPGA 登录"米联客"FPGA社区-www.uisrc.com视频课程、答疑解惑! 1概述 本小节主要讲解Verilog语法的FIFO设计,需要掌握FIFO的基本原理,掌握同步FIFO和异步FIFO的结构。 2同步FIFO FI ......

UART

1、UART简介 通用异步收发传输器(Universal Asynchronous Receiver/Transmitter,UART)是一种异步收发传输器,其在数据发送时将并行数据转换成串行数据来传输,在数据接收时将接收到的串行数据转换成并行数据,可以实现全双工传输和接收。它包括了RS232、RS ......

6 浅谈XILINX FIFO的基本使用

软件版本:VIVADO2021.1 操作系统:WIN10 64bit 硬件平台:适用XILINX A7/K7/Z7/ZU/KU系列FPGA 登录米联客(MiLianKe)FPGA社区-www.uisrc.com观看免费视频课程、在线答疑解惑! 1 概述 首先来大概了解下什么是FIFO ,FIFO( ......

11 UART串口接收驱动设计

软件版本:VIVADO2021.1 操作系统:WIN10 64bit 硬件平台:适用XILINX A7/K7/Z7/ZU/KU系列FPGA 登录米联客(MiLianKe)FPGA社区-www.uisrc.com观看免费视频课程、在线答疑解惑! 1 概述 UART串口通信是应用非常广泛的一种串行异步通 ......

10 UART串口发送驱动设计

软件版本:VIVADO2021.1 操作系统:WIN10 64bit 硬件平台:适用XILINX A7/K7/Z7/ZU/KU系列FPGA 登录米联客(MiLianKe)FPGA社区-www.uisrc.com观看免费视频课程、在线答疑解惑! 1 概述 UART串口通信是应用非常广泛的一种串行异步通 ......

(转载)为什么UART串口通信要16倍过采样数据

增强抗干扰是原因之一 标准UART可以选16倍采样,也可以选64倍采样,个人觉得应该是方便分频设计. 标准UART的RXD前端有一个"1到0跳变检测器",当其连续接受到8个RXD上的地电平时,该检测器就认为RXD线出现了起始位,进入接受数据状态.在接受状态,接受控制器对数据位7,8,9三个脉冲采样, ......

ICEE-SPI-debug最好用 SPI 和 JTAG 或更优的(高达104MHz的)SPI通信保障飞速的debug响应;不再像UART的115200 BaudRate ~

S25FL032P : 32-Mbit CMOS 3.0 Volt Flash Memory with 104-MHz SPI (Serial Peripheral Interface) Multi I/O Bus SPANSION Zentel SDRAM; https://www.zeroday ......

S32K146-CAN fifo接收

之前项目中,一直用的MB(message buffer)结构和中断方式来接收总线CAN 报文。总线负载率和MCU负载不高的情况下,能够正常接收报文。 总线报文复杂的时候,可以利用CAN-FIFO和硬件过滤来提高MCU接收报文能力和性能。 先理解三个概念: 1)筛选ID;2)掩码;3)FIFO接收 筛 ......

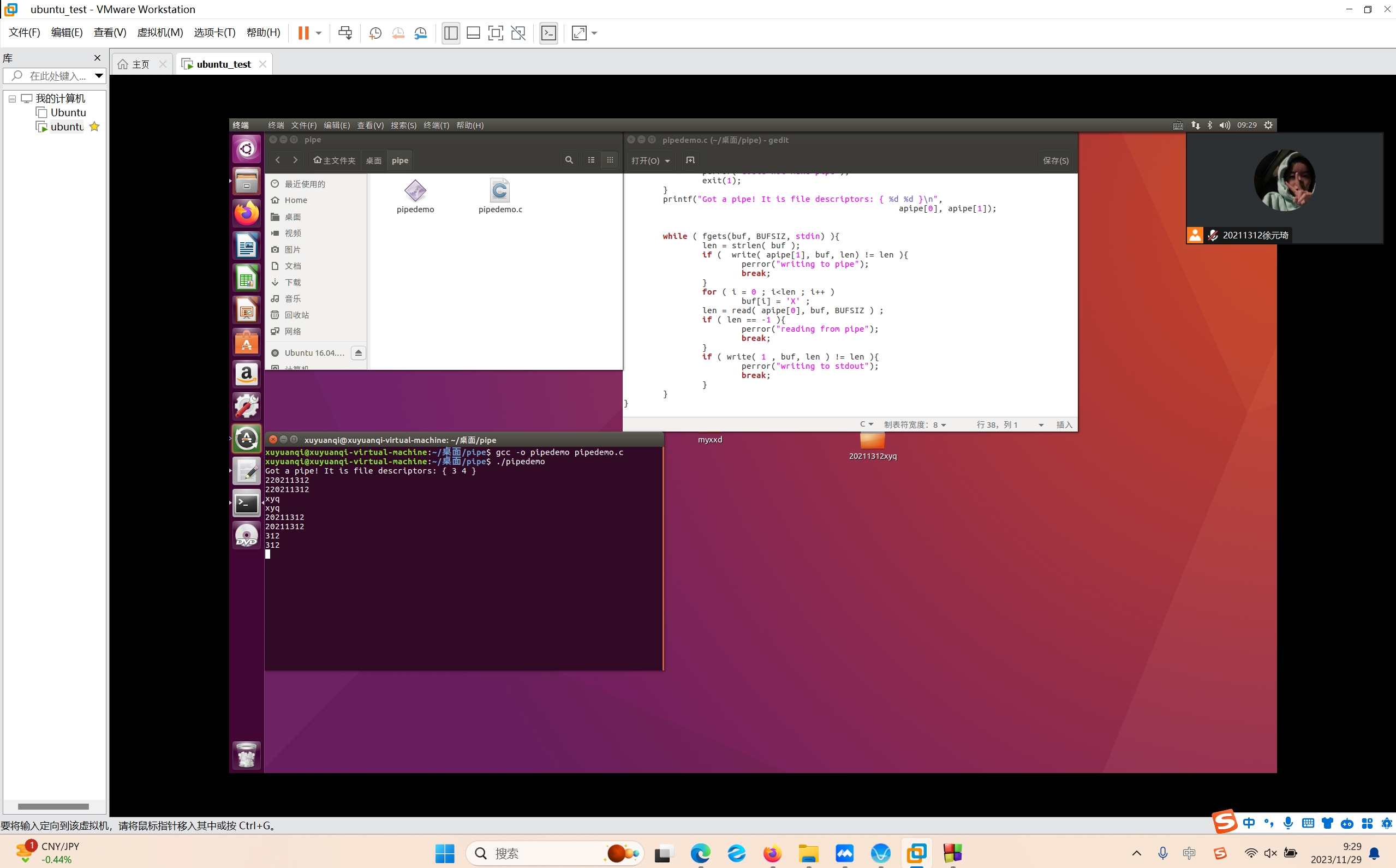

进程间通信-信号-pipe-fifo

1.运行结果 这三段代码实现了 FIFO(命名管道)的基本操作,允许进程之间进行通信。以下是对每个程序的简要说明: fifo_creator.c: 这个程序创建了一个 FIFO 文件,它使用 mkfifo 函数在指定路径下创建了一个名为 /tmp/myfifo 的 FIFO。 • mkfifo("/ ......

Maix II Dock 的USB OTG 及USB UART 测试

1、通过USB OTG接口实现ADB的终端交互 ①、使用type C 数据线连接电脑和Maix II Dock板卡的USB OTG 接口 ②、电脑弹窗并识别Maix II Dock板卡为一个“U盘”,如果提示U盘驱动有问题,请忽略。 ③、进入U盘可以看到对应的配置文件及一个app执行文件(/root ......

同步FIFO设计

FIFO有一个读口和一个写口,读写时钟一致是同步FIFO,时钟不一致就是异步FIFO IP设计中通常使用的是同步FIFO 异步FIFO通常使用在跨时钟域设计中 RAM(Random Access Memory)的设计 FIFO中的数据可以存储在寄存器中或者SRAM中,FIFO的容量比较小的时候,使用 ......

进程间通信-信号-pipe-fifo

进程间通信-信号-pipe-fifo 编译fifo文件夹的程序 运行fifo文件夹的程序 代码说明 1.consumer.c 文件包含一个用来从 FIFO(命名管道)读取数据的 C 程序。以下是它的主要组件和系统调用的分解: main() 函数: 初始化文件描述符(pipe_fd)、返回状态(res ......

第7天 FIFO与鼠标控制

获取按键编码 当中断程序处理完毕之后需要相8259A发送一个处理完毕的信号,这样8259A才知道中断已经处理完毕,可以接收下一个中断信号了,不然的话,我们的键盘中断一直阻塞在哪里没办法进行处理下一个按键操作。 io_out8(PIC0_OCW2, 0x61);就是为了满足这个操作的。键盘的中断是IR ......

进程间通信-信号-pipe-fifo

编译运行 Fifo Consumer Producer 一起运行 Testmf pipe文件夹 Pipe Listarg 理解 ()Pipe 概念: 管道是一种在两个进程之间进行通信的机制。个进程的输出可以通过管道传递给另一个进程的输入创建: 在C语言中,可以使用pipe系统调用创建管道。管道有两端 ......

进程间通信-信号-pipe-fifo(课上测试)

一.运行结果 二.代码说明 consumer.c 该程序是一个使用FIFO(命名管道)进行进程间通信的示例。首先定义了FIFO的名称和缓冲区的大小。然后在主函数中,打开了一个以只读方式打开的FIFO,并读取FIFO中的数据直到读取完毕,最后关闭FIFO。 相关系统调用说明:1. open:打开FIF ......

消息传递:管道和FIFO

一、简介 管道是没有名字的,管道创建的资源由内核管理,单个程序中不同进程通过管道描述符fd进行通信,对于程序和程序之间是无法通信的。 FIFO是有名字的(也称为 有名管道),每一个FIFO都有一个文件与之关联,但仅限于同一主机程序与程序之间通信,无法通过在NFS上创建FIFO通信。 二、管道 所有管 ......

环形缓冲区FIFO

最近学习一个LwRB开源环形缓冲区FIFO设计,即先入先出缓冲区。LwRB 是一个开源、通用环形缓冲区库。 1、只有单个任务写和单个任务读时,线程是安全的 2、只有单个中断写和单个中断读时,中断是安全的 3、支持内存间的 DMA 操作,实现缓冲区和应用程序内存之间零拷贝 4、对于读数据,提供 pee ......

进程间通信-信号-pipe-fifo(

( input clk, input rst, input read_en, input write_en, input write_data, output ......

USB(2.0 / Type-C) to MPSSE(JTAG / SPI / IIC) / UART / FIFO: FTDI 的FT4232H配成SPI+JTAG+Two Ways UART使用实例

Ti60 Demo板FT4232H 串口使用 易灵思FPGA技术交流 2022-04-15 08:43 Ti60 F225 demo板使用的是FT4232H,有4个通道A,B,C和D。其中A通道用于SPI接口,可以是AS也可以是PS。通道B用于JTAG,通道C连接了UART,通道D连接了FX3。 A ......

Electrical(Hardware) Protocols: FIFO / JTAG / SPI / IIC / IIS / UART / SWD / ICSP / CANBus/ModBus

Electrical(Hardware) Protocols: JTAG(Joint Test Action Group), JTAG is actually a protocol over SPI. 5 pins/connections(GND, TMS, TCK, TDI, TDO), Outp ......

USB(2.0 / Type-C) to MPSSE(JTAG / SPI / IIC) / UART / FIFO: FTDI 的桥接芯片选型

首次使用 FTDI 的 USB bridging chips 是在 Amazon 工作期间,需要通过 PC电脑上 Linux 开发环境 的 Kermit 软件, 经由FTDI的USB to UART串口线 对 Amazon Kindle 进行 Hardware/OS/Framework/Softwa ......

队列(Queue):先进先出(FIFO)的数据结构

队列是一种基本的数据结构,用于在计算机科学和编程中管理数据的存储和访问。队列遵循先进先出(First In, First Out,FIFO)原则,即最早入队的元素首先出队。这种数据结构模拟了物理世界中的队列,如排队等待服务的人。 在本篇博客中,我们将详细介绍队列的概念、用途、实现以及如何在编程中使用 ......

FIFO

1 module Write_Data #( 2 parameter DEEP_WIDTH = 4 , 3 parameter FIFO_DEEP = 5'd16 , 4 parameter GAP_WIDTH = 3 5 )( 6 output wfull , //几乎满信号 7 output r ......