RCC clock control register

| RCC_CR | RCC clock control register | RCC 时钟控制寄存器 |

| RCC_PLLCFGR | RCC PLL configuration register | PLL 配置寄存器 |

| RCC_CFGR | RCC clock configuration register | 时钟配置寄存器 |

| RCC_CIR | RCC clock interrupt register | RCC 时钟中断寄存器 |

| RCC_AHB1RSTR | RCC AHB1 peripheral reset register | AHB1 外设复位寄存器 |

| RCC_AHB2RSTR | RCC AHB2 peripheral reset register | AHB2 外设复位寄存器 |

| RCC_APB1RSTR | RCC APB1 peripheral reset register | APB1 外设复位寄存器 |

| RCC_APB2RSTR | RCC APB2 peripheral reset register | APB2 外设复位寄存器 |

| RCC_AHB1ENR | RCC AHB1 peripheral clock enable register | AHB1 外设时钟使能寄存器 |

| RCC_AHB2ENR | RCC AHB2 peripheral clock enable register | AHB2 外设时钟使能寄存器 |

| RCC_APB1ENR | RCC APB1 peripheral clock enable register | APB1 外设时钟使能寄存器 |

| RCC_APB2ENR | RCC APB2 peripheral clock enable register | APB2 外设时钟使能寄存器 |

| RCC_AHB1LPENR | RCC AHB1 peripheral clock enable in low power mode register | AHB1外设低功耗时钟使能寄存器 |

| RCC_AHB2LPENR | RCC AHB2 peripheral clock enable in low power mode register | AHB2外设低功耗时钟使能寄存器 |

| RCC_APB1LPENR | RCC APB1 peripheral clock enable in low power mode register | APB1外设低功耗时钟使能寄存器 |

| RCC_APB2LPENR | RCC APB2 peripheral clock enabled in low power mode register | APB2外设低功耗时钟使能寄存器 |

| RCC_BDCR | RCC Backup domain control register | RCC 备份域控制寄存器 |

| RCC_CSR | RCC clock control & status register | RCC 时钟控制和状态寄存器 |

| RCC_SSCGR | RCC spread spectrum clock generation register | RCC 扩频时钟生成寄存器 |

| RCC_PLLI2SCFGR | RCC PLLI2S configuration register | RCC PLLI2S 配置寄存器 |

| RCC_DCKCFGR | RCC Dedicated Clocks Configuration Register | RCC 专用时钟配置寄存器 |

| RCC 时钟控制寄存器 (RCC_CR) RCC clock control register |

| 位 27 PLLI2SRDY:PLLI2S 时钟就绪标志 (PLLI2S clock ready flag |

| 位 26 PLLI2SON:PLLI2S 使能 (PLLI2S enable |

| 位 25 PLLRDY:主 PLL (PLL) 时钟就绪标志 (Main PLL (PLL) clock ready flag |

| 位 24 PLLON:主 PLL (PLL) 使能 (Main PLL (PLL) enable |

| 位 19 CSSON:时钟安全系统使能 (Clock security system enable |

| 位 18 HSEBYP:HSE 时钟旁路 (HSE clock bypass |

| 位 17 HSERDY:HSE 时钟就绪标志 (HSE clock ready flag |

| 位 16 HSEON:HSE 时钟使能 (HSE clock enable |

| 位 15:8 HSICAL[7:0]:内部高速时钟校准 (Internal high-speed clock calibration |

| 位 7:3 HSITRIM[4:0]:内部高速时钟微调 (Internal high-speed clock trimming |

| 位 1 HSIRDY:内部高速时钟就绪标志 (Internal high-speed clock ready flag) |

| 位 0 HSION:内部高速时钟使能 (Internal high-speed clock enable) |

| PLL 配置寄存器 RCC_PLLCFGR |

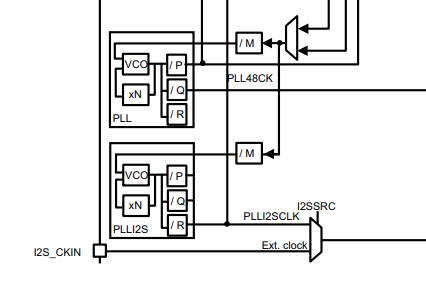

| 位 27:24 PLLQ:主 PLL (PLL) 分频系数 |

| 位 22 PLLSRC:主 PLL(PLL) 和音频 PLL (PLLI2S) 输入时钟源 |

| 位 17:16 PLLP:适用于主系统时钟的主 PLL (PLL) 分频系数 (Main PLL (PLL) division factor for main system clock) |

| 位 14:6 PLLN:适用于 VCO 的主 PLL (PLL) 倍频系数 (Main PLL (PLL) multiplication factor for VCO) |

| 位 5:0 PLLM:主 PLL (PLL) 和音频 PLL (PLLI2S) 输入时钟的分频系数 (Division factor for the main PLL (PLL) and audio PLL (PLLI2S) input clock |

| RCC 时钟配置寄存器 RCC_CFGR |

|

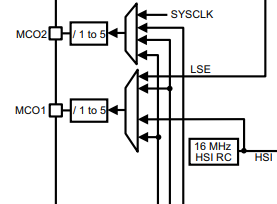

位 31:30 MCO2[1:0]:微控制器时钟输出 2 (Microcontroller clock output 2

|

| 位 27:29 MCO2PRE:MCO2 预分频器 (MCO2 prescaler) |

| 位 24:26 MCO1PRE:MCO1 预分频器 (MCO1 prescaler) |

|

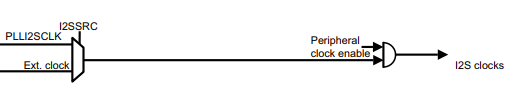

位 23 I2SSRC:I2S 时钟选择 (I2S clock selection)

|

| 位 22:21 MCO1:微控制器时钟输出 1 (Microcontroller clock output 1 |

|

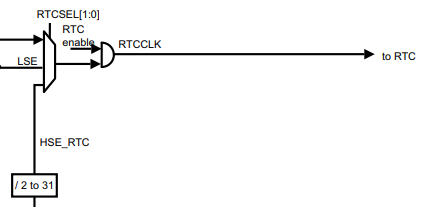

位 20:16 RTCPRE:适用于 RTC 时钟的 HSE 分频系数

|

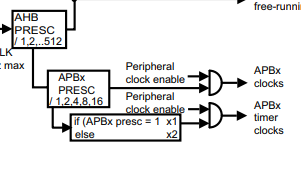

| 位 15:13 PPRE2:APB 高速预分频器 (APB2) (APB high-speed prescaler (APB2)) |

|

位 12:10 PPRE1:APB 低速预分频器 (APB1) (APB Low speed prescaler (APB1))

|

|

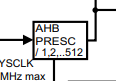

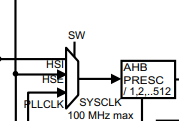

位 7:4 HPRE:AHB 预分频器 (AHB prescaler)

|

| 位 3:2 SWS:系统时钟切换状态 (System clock switch status) |

|

位 1:0 SW:系统时钟切换 (System clock switch)

|

| RCC 时钟中断寄存器 RCC_CIR |

| 位 23 CSSC:时钟安全系统中断清零 (Clock security system interrupt clear |

| 位 21 PLLI2SRDYC:PLLI2S 就绪中断清零 (PLLI2S ready interrupt clear) |

| 位 20 PLLRDYC:主 PLL(PLL) 就绪中断清零 (Main PLL(PLL) ready interrupt clear |

| 位 19 HSERDYC:HSE 就绪中断清零 (HSE ready interrupt clear |

| 位 18 HSIRDYC:HSI 就绪中断清零 (HSI ready interrupt clear |

| 位 17 LSERDYC:LSE 就绪中断清零 (LSE ready interrupt clear) |

| 位 16 LSIRDYC:LSI 就绪中断清零 (LSI ready interrupt clear |

| 位 13 PLLI2SRDYIE:PLLI2S 就绪中断使能 (PLLI2S ready interrupt enable) |

| 位 12 PLLRDYIE:主 PLL (PLL) 就绪中断使能 (Main PLL (PLL) ready interrupt enable) |

| 位 11 HSERDYIE:HSE 就绪中断使能 (HSE ready interrupt enable) |

| 位 10 HSIRDYIE:HSI 就绪中断使能 (HSI ready interrupt enable) |

| 位 9 LSERDYIE:LSE 就绪中断使能 (LSE ready interrupt enable) |

| 位 8 LSIRDYIE:LSI 就绪中断使能 (LSI ready interrupt enable |

| 位 7 CSSF:时钟安全系统中断标志 (Clock security system interrupt flag) |

| 位 5 PLLI2SRDYF:PLLI2S 就绪中断标志 (PLLI2S ready interrupt flag) |

| 位 4 PLLRDYF:主 PLL (PLL) 就绪中断标志 (Main PLL (PLL) ready interrupt flag) |

| 位 3 HSERDYF:HSE 就绪中断标志 (HSE ready interrupt flag |

| 位 2 HSIRDYF:HSI 就绪中断标志 (HSI ready interrupt flag) |

| 位 1 LSERDYF:LSE 就绪中断标志 (LSE ready interrupt flag) |

| 位 0 LSIRDYF:LSI 就绪中断标志 (LSI ready interrupt flag) |

|

RCC AHB1 peripheral clock enable register (RCC_AHB1ENR) AHB1外设时钟使能 |

| Bit 22 DMA2EN: DMA2 clock enable |

| Bit 21 DMA1EN: DMA1 clock enable |

| Bit 12 CRCEN: CRC clock enable |

| Bit 7 GPIOHEN: IO port H clock enable |

| Bit 4 GPIOEEN: IO port E clock enable |

| Bit 3 GPIODEN: IO port D clock enable |

| Bit 2 GPIOCEN: IO port C clock enable |

| Bit 1 GPIOBEN: IO port B clock enable |

| Bit 0 GPIOAEN: IO port A clock enable |

|

RCC AHB2 peripheral clock enable register (RCC_AHB2ENR) AHB2外设时钟使能 |

| Bit 7 OTGFSEN: USB OTG FS clock enable |

|

RCC APB1 peripheral clock enable register (RCC_APB1ENR) APB1外设时钟使能 |

| Bit 28 PWREN: Power interface clock enable |

| Bit 23 I2C3EN: I2C3 clock enable |

| Bit 22 I2C2EN: I2C2 clock enable |

| Bit 21 I2C1EN: I2C1 clock enable |

| Bit 17 USART2EN: USART2 clock enable |

| Bit 15 SPI3EN: SPI3 clock enable |

| Bit 14 SPI2EN: SPI2 clock enable |

| Bit 11 WWDGEN: Window watchdog clock enable |

| Bit 3 TIM5EN: TIM5 clock enable |

| Bit 2 TIM4EN: TIM4 clock enable |

| Bit 1 TIM3EN: TIM3 clock enable |

| Bit 0 TIM2EN: TIM2 clock enable |

|

RCC APB2 peripheral clock enable register APB2外设时钟使能 |

| Bit 20 SPI5EN:SPI5 clock enable |

| Bit 18 TIM11EN: TIM11 clock enable |

| Bit 17 TIM10EN: TIM10 clock enable |

| Bit 16 TIM9EN: TIM9 clock enable |

| Bit 14 SYSCFGEN: System configuration controller clock enable |

| Bit 13 SPI4EN: SPI4 clock enable |

| Bit 12 SPI1EN: SPI1 clock enable |

| Bit 11 SDIOEN: SDIO clock enable |

| Bit 8 ADC1EN: ADC1 clock enable |

| Bit 5 USART6EN: USART6 clock enable |

| Bit 4 USART1EN: USART1 clock enable |

| Bit 0 TIM1EN: TIM1 clock enable |

|

RCC Backup domain control register (RCC_BDCR) 备份域控制寄存器 |

| Bit 16 BDRST: Backup domain software reset 备份域软件复位 |

| Bit 15 RTCEN: RTC clock enable RTC 时钟使能 |

| Bits 9:8 RTCSEL[1:0]: RTC clock source selection RTC 时钟源选择 |

| Bit 3 LSEMOD: External low-speed oscillator bypass :外部低速振荡器旁路模式选择 |

| Bit 2 LSEBYP: External low-speed oscillator bypass 外部低速振荡器旁路 |

| Bit 1 LSERDY: External low-speed oscillator ready 外部低速振荡器就绪 |

| Bit 0 LSEON: External low-speed oscillator enable 外部低速振荡器使能 |

|

RCC clock control & status register (RCC_CSR) RCC 时钟控制和状态寄存器 |

| Bit 31 LPWRRSTF: Low-power reset flag 低功耗复位标志 |

| Bit 30 WWDGRSTF: Window watchdog reset flag 窗口看门狗复位标志 |

| Bit 29 IWDGRSTF: Independent watchdog reset flag 独立看门狗复位标志 |

| Bit 28 SFTRSTF: Software reset flag 软件复位标志 |

| Bit 27 PORRSTF: POR/PDR reset flag POR/PDR 复位标志 |

| Bit 26 PINRSTF: PIN reset flag 引脚复位标志 |

| Bit 25 BORRSTF: BOR reset flag BOR 复位标志 |

| Bit 24 RMVF: Remove reset flag 清除复位标志 |

| Bit 1 LSIRDY: Internal low-speed oscillator ready 内部低速振荡器就绪 |

| Bit 0 LSION: Internal low-speed oscillator enable 内部低速振荡器使能 |

|

RCC spread spectrum clock generation register (RCC_SSCGR) RCC 扩频时钟生成寄存器 |

| Bit 31 SSCGEN: Spread spectrum modulation enable 扩频调制使能 |

| Bit 30 SPREADSEL: Spread Select 扩频选择 |

| Bits 27:13 INCSTEP: Incrementation step 增量步长 |

| Bits 12:0 MODPER: Modulation period 调制周期 |

|

RCC PLLI2S configuration register (RCC_PLLI2SCFGR) RCC PLLI2S 配置寄存器 |

| Bits 30:28 PLLI2SR: PLLI2S division factor for I2S clocks 适用于 I2S 时钟的 PLLI2S 分频系数 |

| Bits 14:6 PLLI2SN: PLLI2S multiplication factor for VCO 用于 VCO 的 PLLI2S 倍频系数 |

| Bits 5:0 PLLI2SM: Division factor for the audio PLL (PLLI2S) input clock |

|

RCC Dedicated Clocks Configuration Register (RCC_DCKCFGR) RCC 专用时钟配置寄存器 |

|

Bit 24 TIMPRE: Timers clocks prescalers selection 定时器时钟预分频器选择 用于控制连接到 APB1 和 APB2 域的所有定时器的时钟频率 |