软件版本:VIVADO2021.1

操作系统:WIN10 64bit

硬件平台:适用XILINX A7/K7/Z7/ZU/KU系列FPGA

登录米联客(MiLianKe)FPGA社区-www.uisrc.com观看免费视频课程、在线答疑解惑!

1 概述

使用VIVADO基于图形化创新编程FPGA的方式可以大大提高FPGA编程效率,但是前提是把代码打包成图形化的IP形式。

前面一节课我们只是完成了简单IP的封装,如果对于有非常多的信号的总线接口,那么利用总线接口封装可以让我们连线的时候以总线形式互联。

当一组或者一类信号接口信号很多,如果单根连线的方式,会非常麻烦,因此把一组或者一类接口封装为总线接口,只需要对总线进行互联,对于图形化设计,提高效率,也简化的设计。

本文实验中对视频时序接口RGB接口的关键信号进行总线封装。并且使用的是VIVADO IP封装库中自带的总线video timing,对于不是VIVADO自带的总线接口,我们也可以自定义,这个本章节不讲解,如果读者感兴趣,可以在 "米联客DDR缓存方案AXI-FDMA"专题中学习,该章节有对复杂的用户自定义接口的自定义总线FDMA接口进行封装。

2 VTC IP封装总线接口

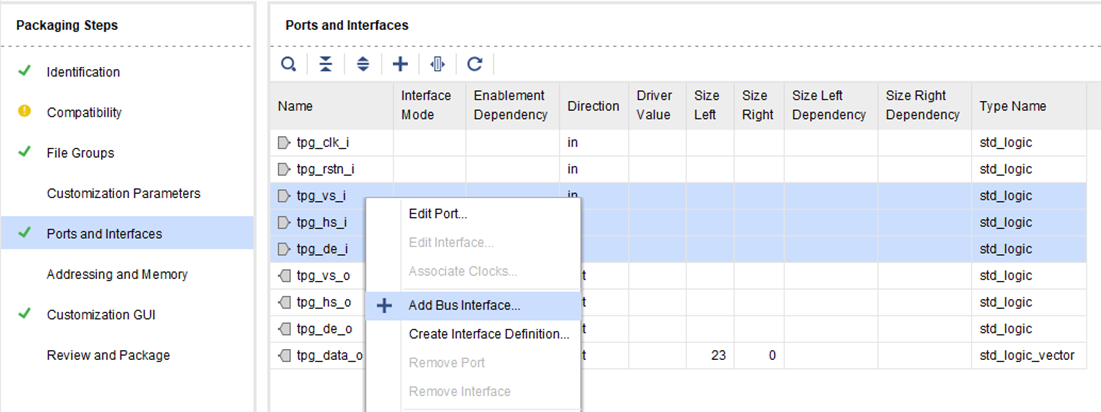

本文不再赘述和前一篇封装IP相同的内容部分,如果有不清楚请阅读前文"VIVADO自定义IP简单封装方法",本文重点讲如何把分离的接口封装为总线IP。单击图下的"+"号,或者选中需要封装总线的信号右击,选择Add Bus Interface(对于VIVADO已经有的总线接口选择这个,没有的需要选择Create Interface Definition, 米联客自定义IP FDMA专题中,FDMA总线接口的封装就会用到, 不再本章节讨论范围)

2.1 Add Interface-General页面

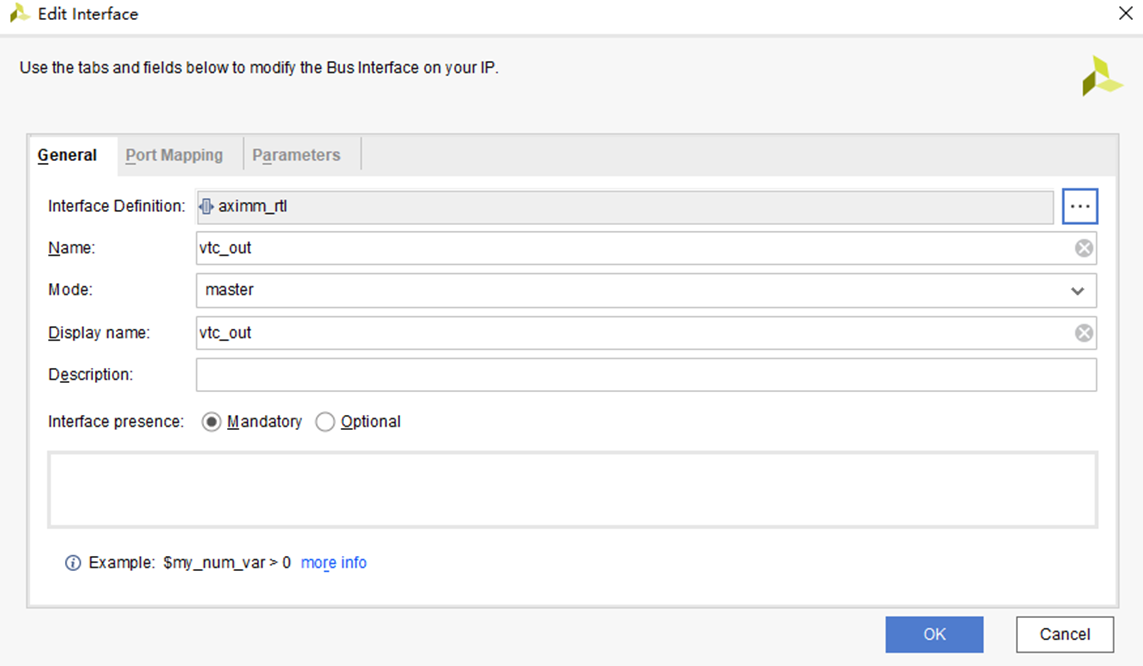

新弹出的界面修改如下几个参数

Name: 改为vtc_out

Display Name:改为vtc_out

Mode:保持master(这个很关键,两个互联的接口,必须一个是master一个是slave)

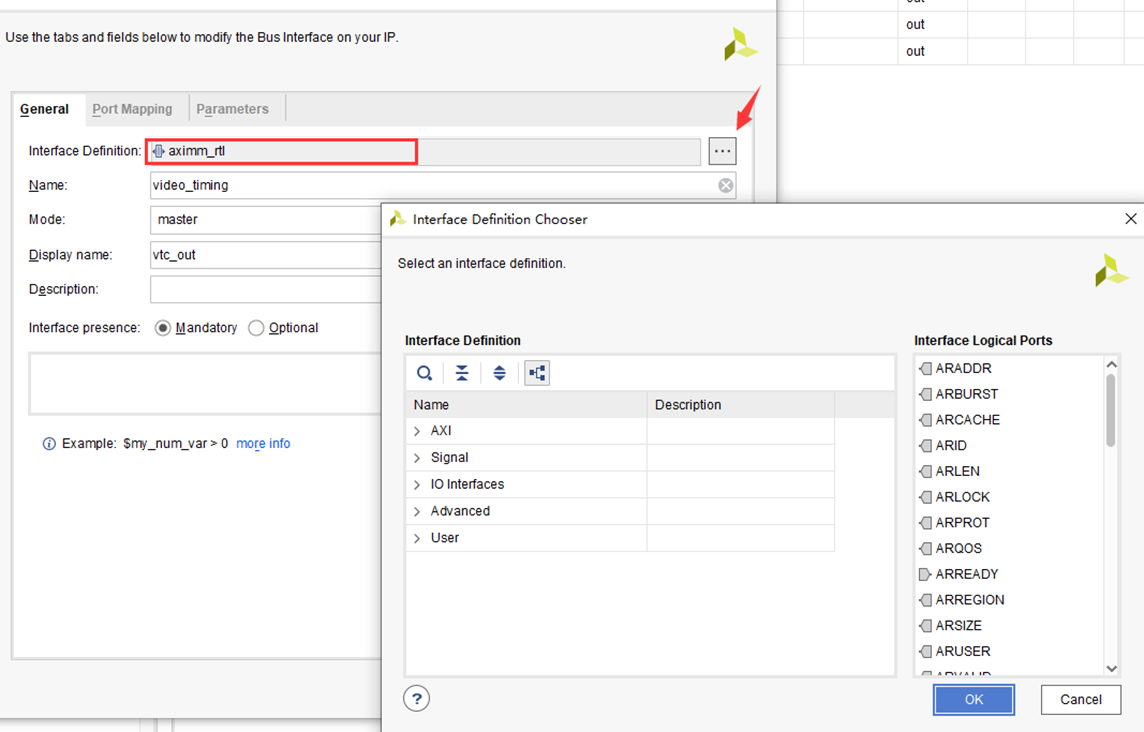

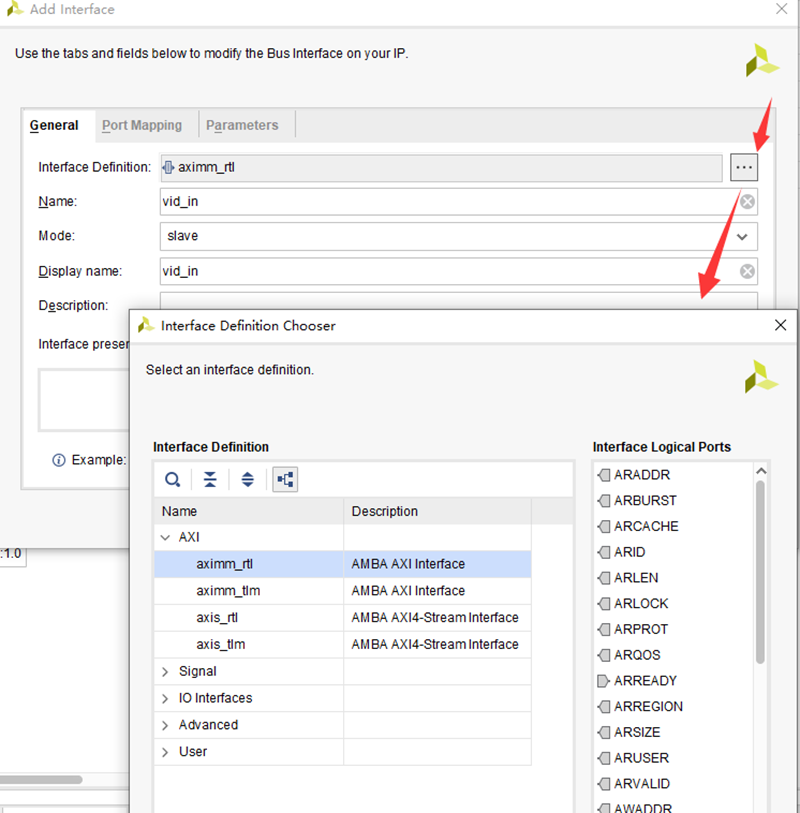

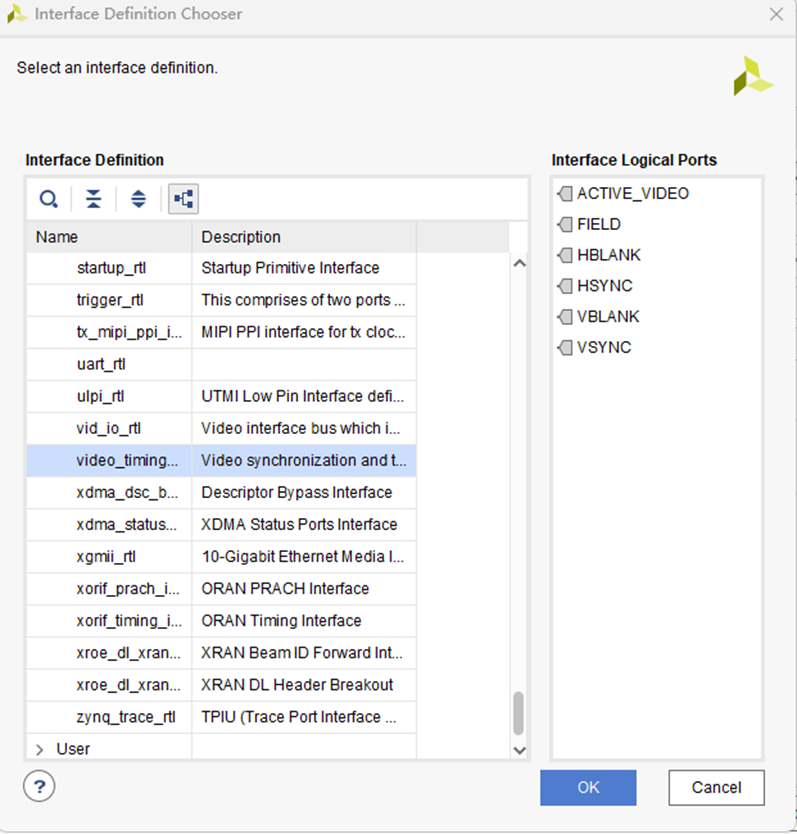

然后修改总线接口的定义,可以看到支持包括AXI、Signal 、IO Interfaces 、Advanced 、User 多种已经软件自带的接口。

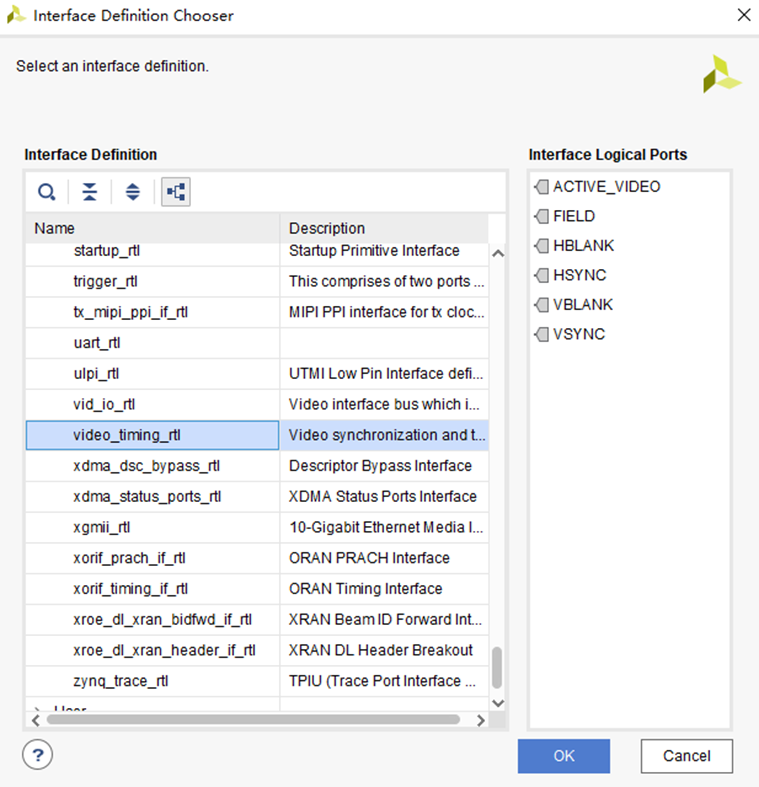

可以看到Advanced中video_timing_rtl包含了VSYNC 、HSYNC、DE 三个信号,和我们自己编写的VTC IP的O_vtc_vs 、O_vtc_hs 、O_vtc_de进行匹配,这样后续软件就能自动识别互联了

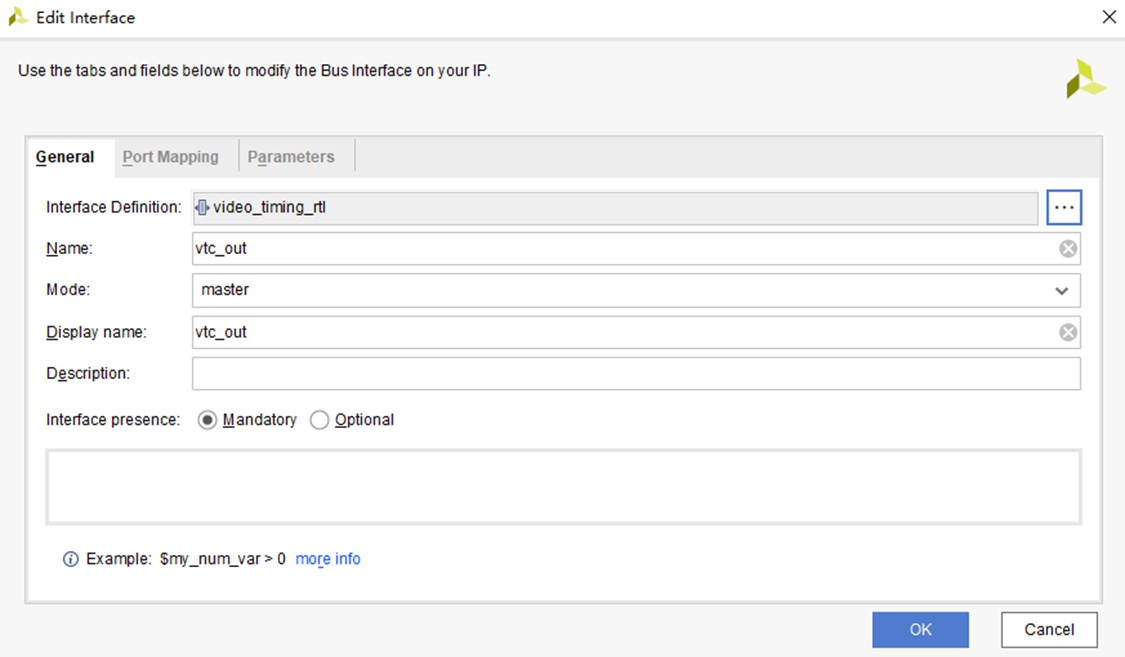

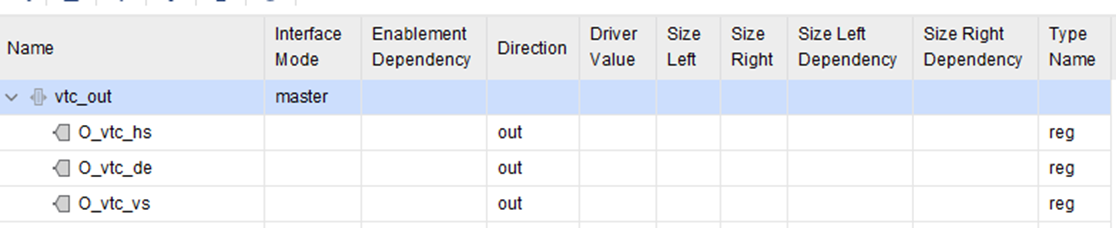

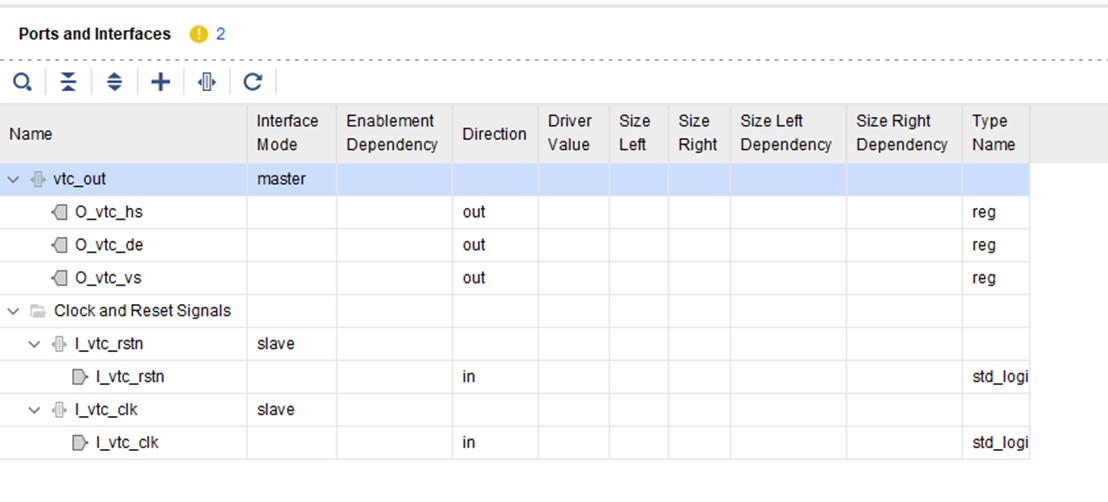

单击OK后如下

2.2 Add Interface-Port Mapping页面

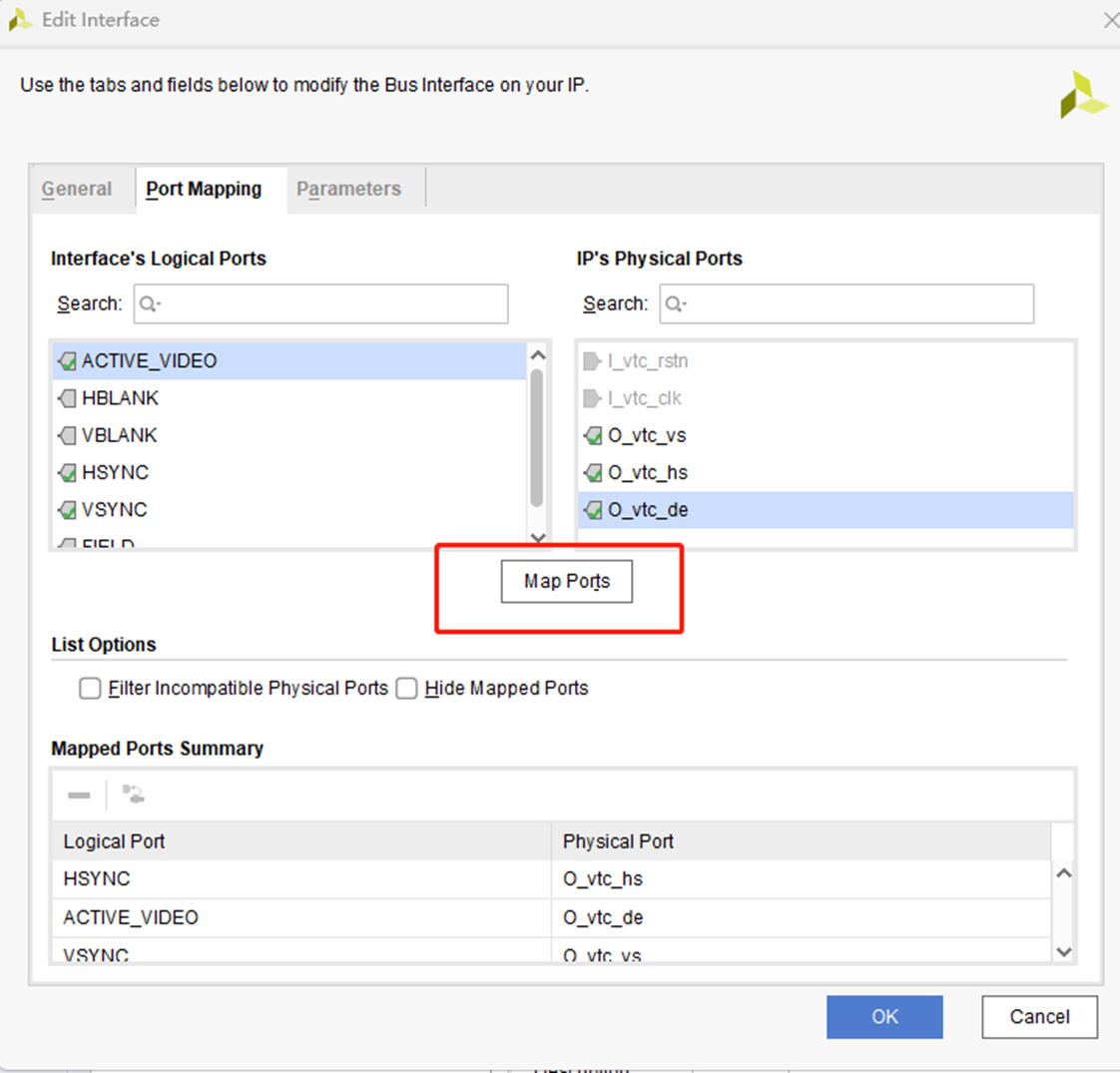

实际上左边大写的信号是系统默认设置的总线信号规则,而右边的是用户自己的信号,通过单击选中需要匹配的信号,然后单击Map Ports完成信号匹配

依次完全所有的信号设置

现在总线接口设置成功了

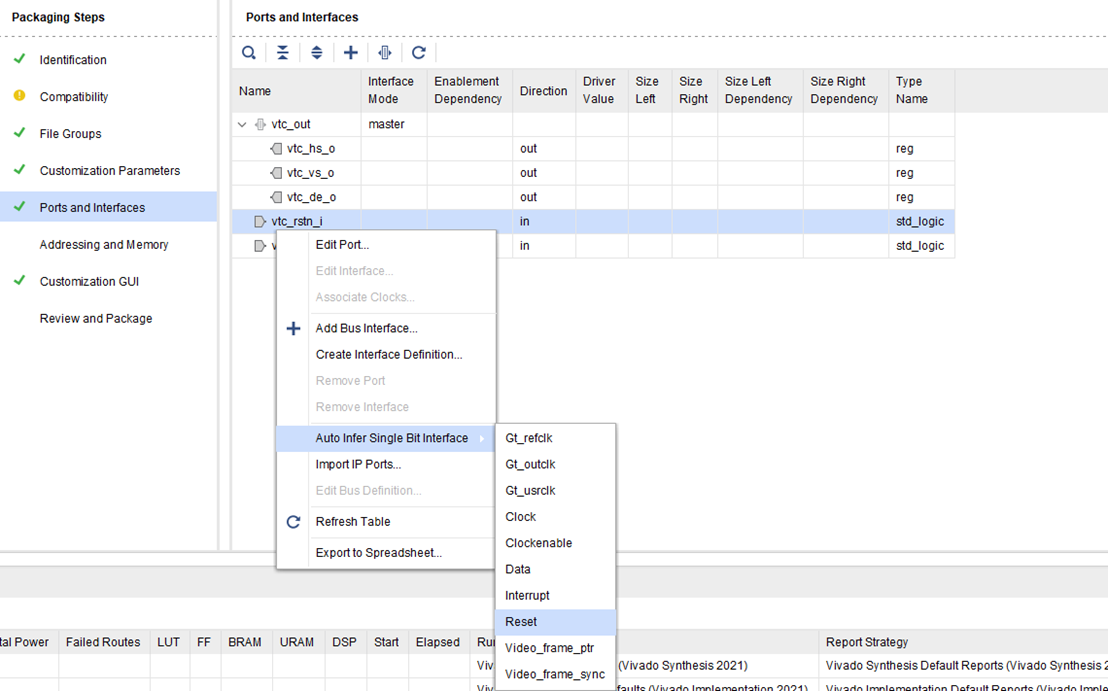

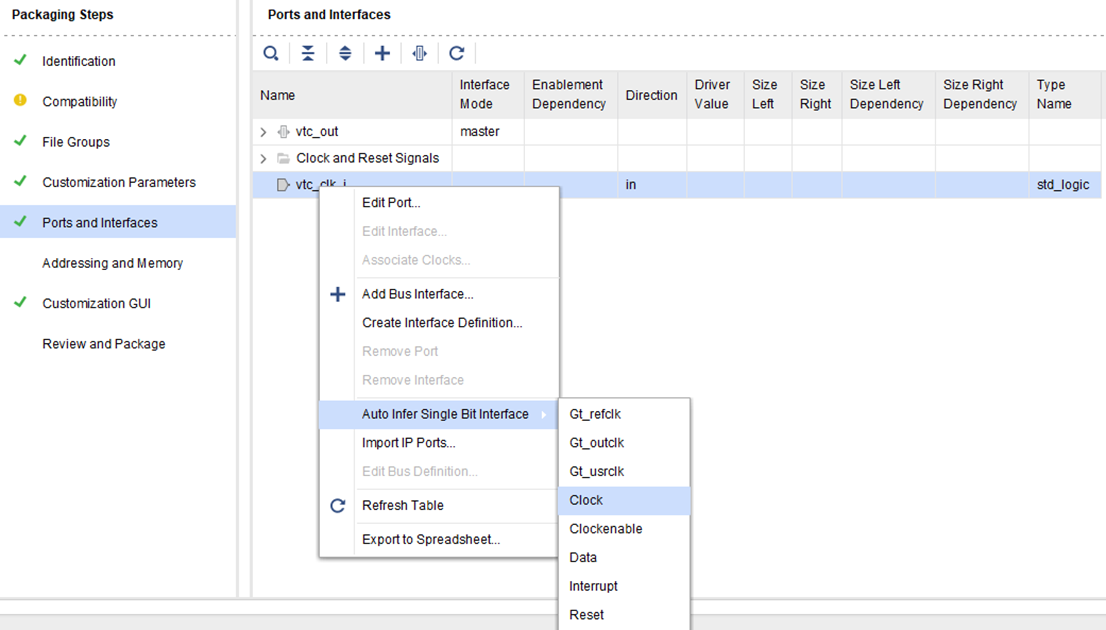

2.3 复位和时钟

最终完成后如下:

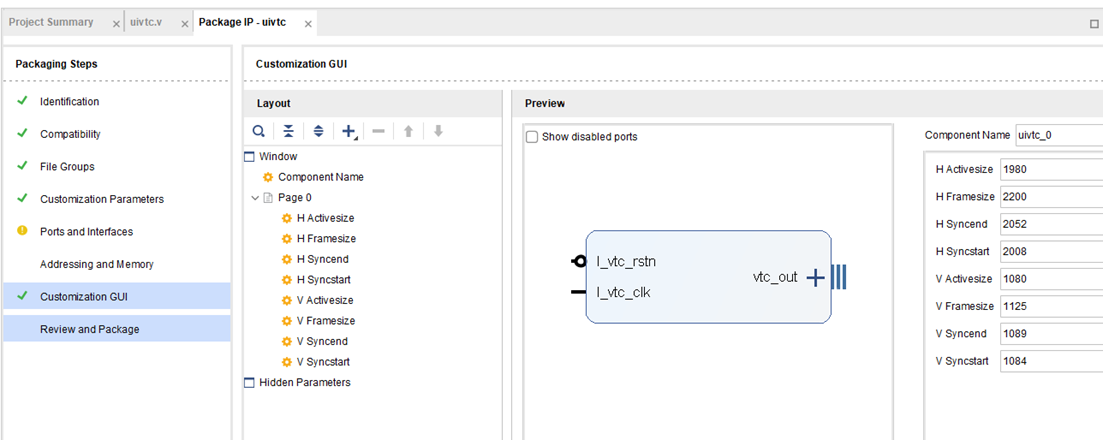

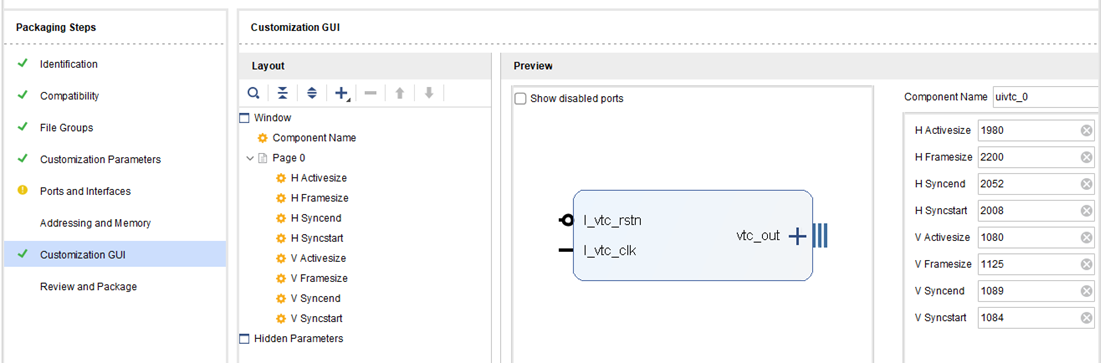

2.4 Customization GUI的调整

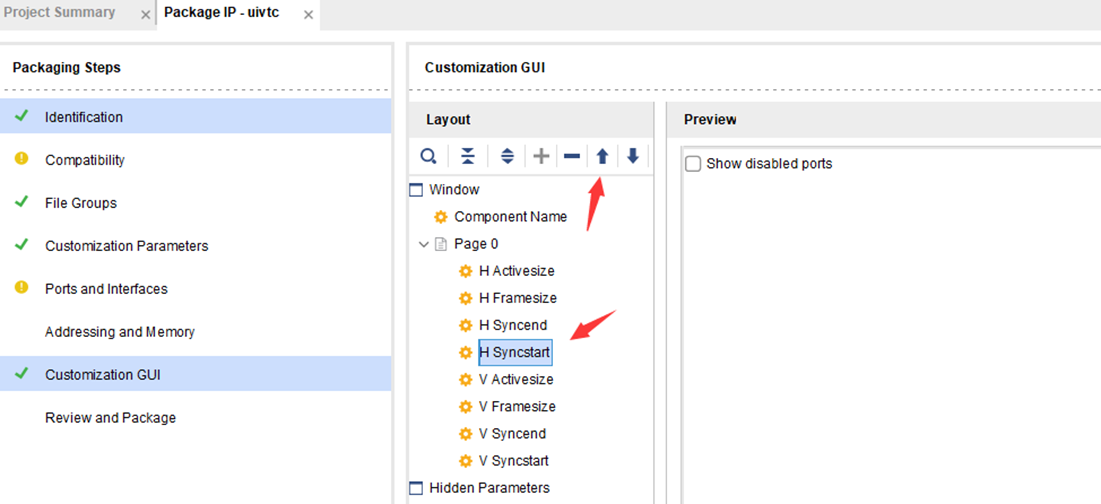

参数默认排列如下,可以调整后更加符合使用习惯

比如把H_Syncstart参数上调,单击向上箭头

我们这里把V_Syncstart也做下调整

2.5 完成封装

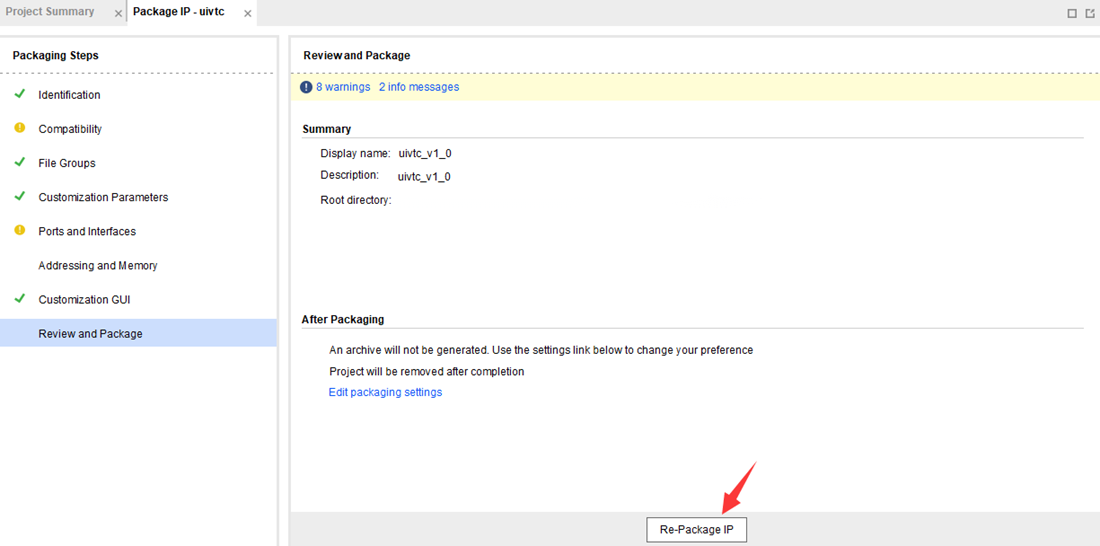

单击Re-Package IP 完成封装

3 TPG IP封装总线接口

本文不再赘述和前一篇封装IP相同的内容部分,如果有不清楚请阅读前文"VIVADO自定义IP简单封装方法",

TPG IP有2个总线接口需要创建

1是和VTC IP相连的视频时序接口

2是输出的视频时序包含了数据部分

3.1 vid_in总线封装

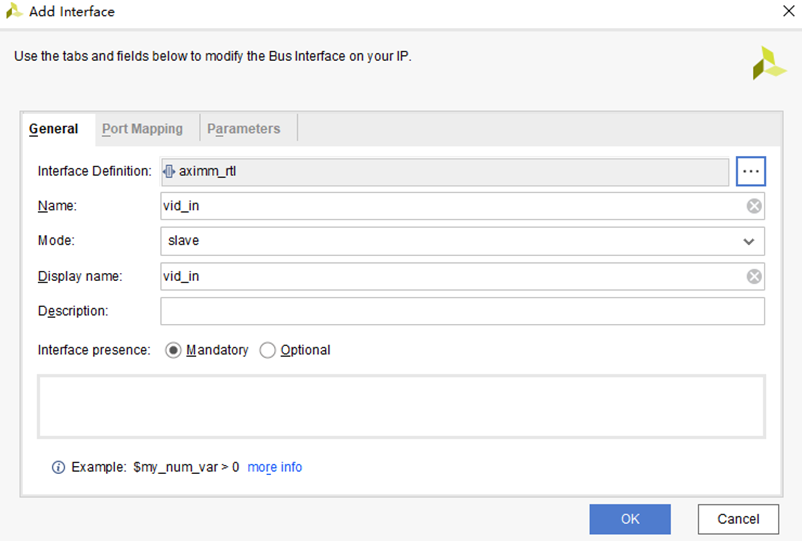

3.1.1 Add Interface-General页面

新弹出的界面修改如下几个参数

Name: 改为vid_in

Display Name:改为vid_in

Mode:改为slave(这个很关键,两个互联的接口,必须一个是master一个是slave)

然后修改总线接口的定义,可以看到支持包括AXI、Signal 、IO Interfaces 、Advanced 、User 多种已经软件自带的接口。

可以看到Advanced中video_timing_rtl包含了VSYNC 、HSYNC、DE 三个信号,和我们自己编写的VID IP的I_vid_vs 、I_vid_hs 、I_vid_de进行匹配,这样后续软件就能自动识别互联了

单击OK后如下

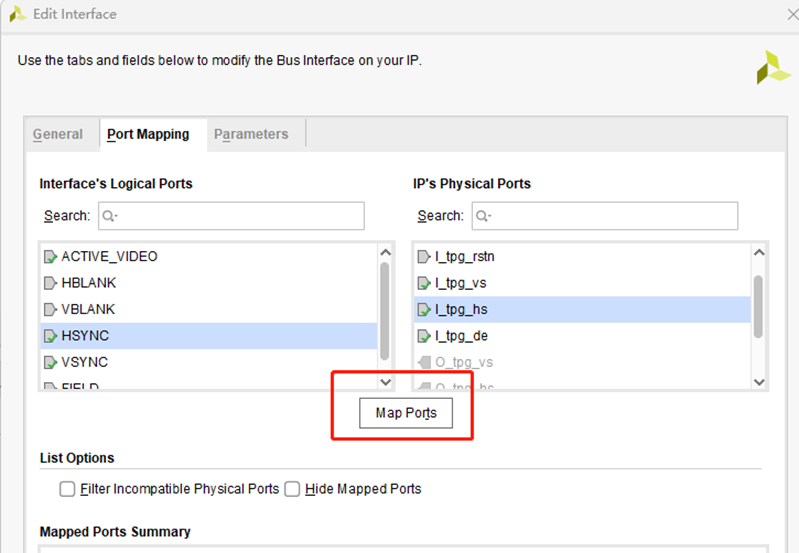

3.1.2 Add Interface-Port Mapping页面

实际上左边大写的信号是系统默认设置的总线信号规则,而右边的是用户自己的信号,通过单击选中需要匹配的信号,然后单击Map Ports完成信号匹配

依次完全所有的信号设置

现在总线接口vid in设置成功了

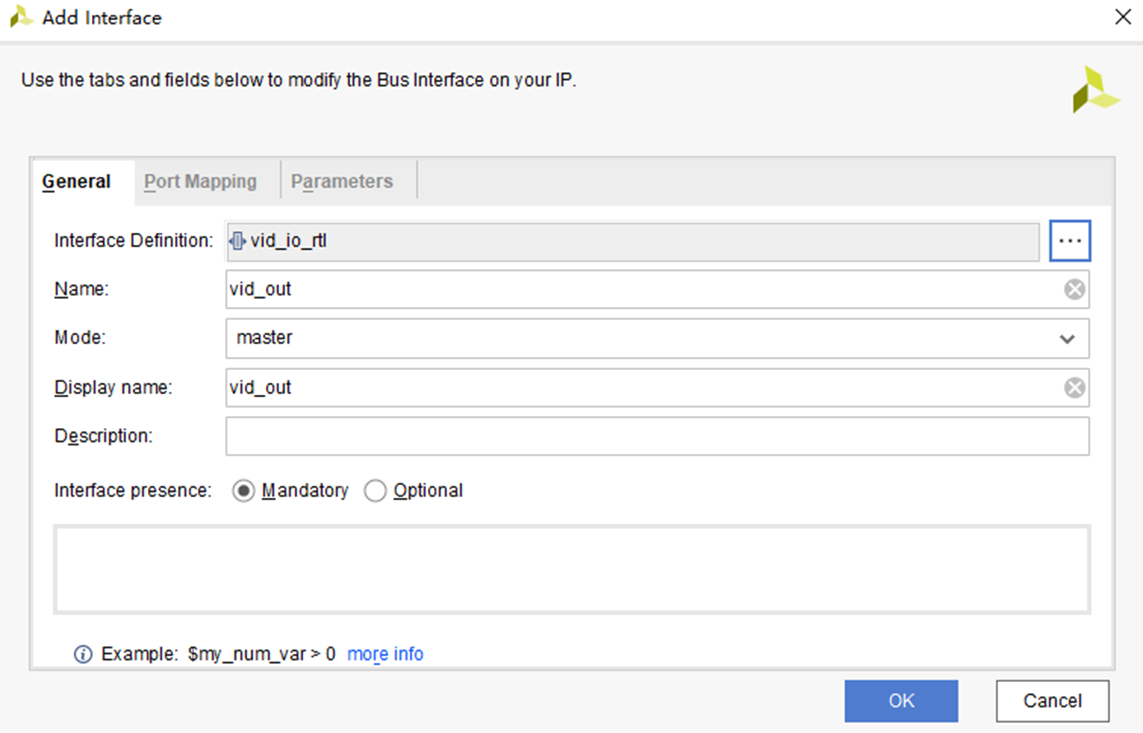

3.2 vid_out总线封装

方法一样,更多详细的过程不再重复,主要看下关键的部分

Name: 改为vid_out

Display Name:改为vid_out

Mode:改为master(这个很关键,两个互联的接口,必须一个是master一个是slave)

Interface Definition:改为vid_io_rtl

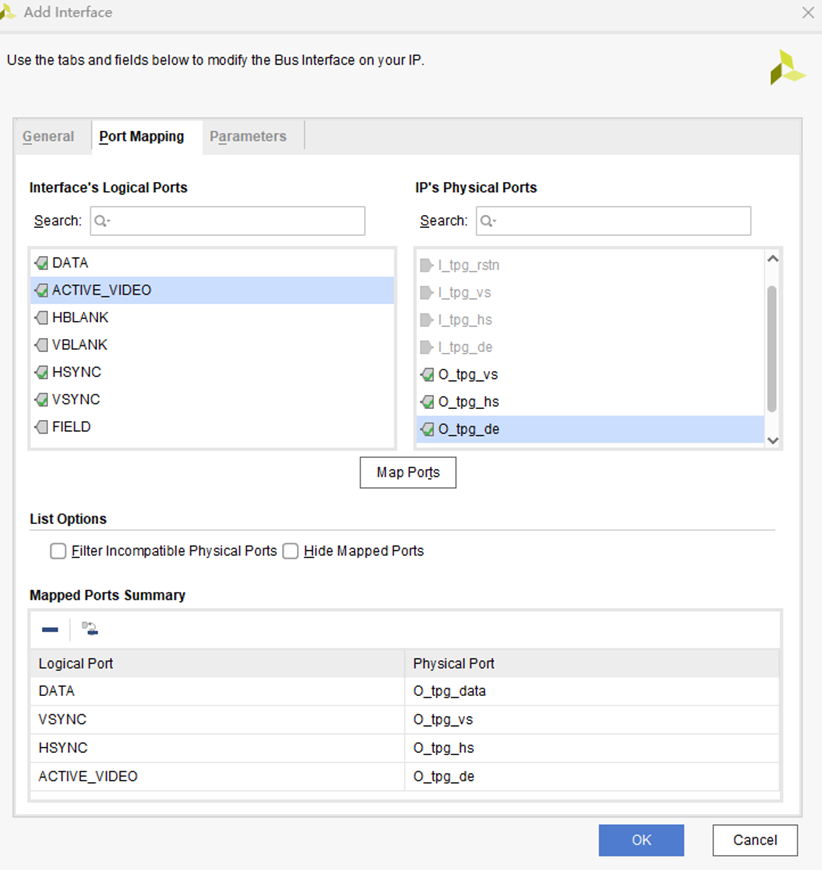

信号MAP如下

3.3 复位和时钟

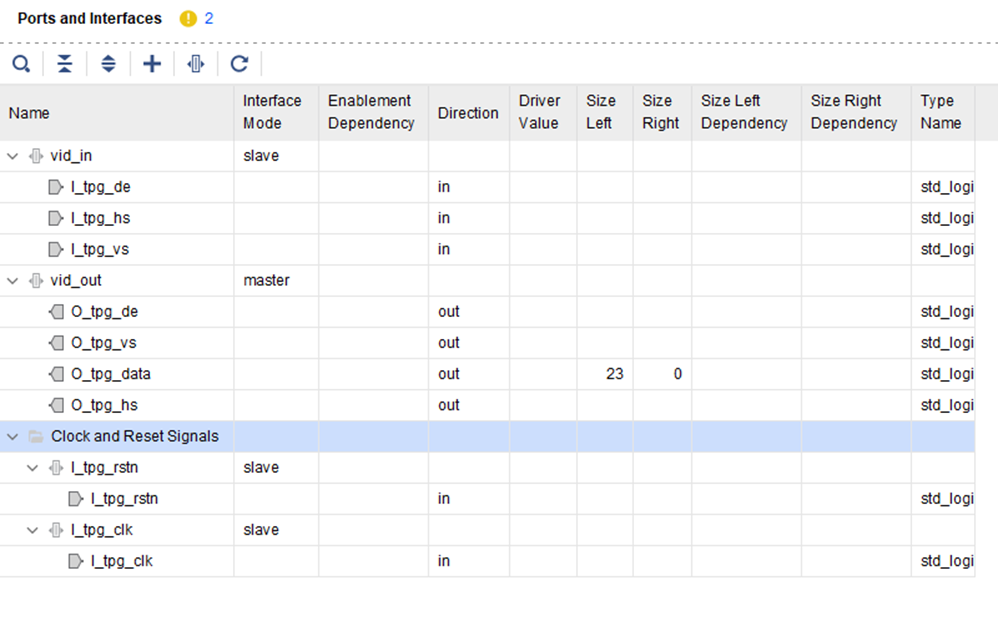

最终完成后如下:

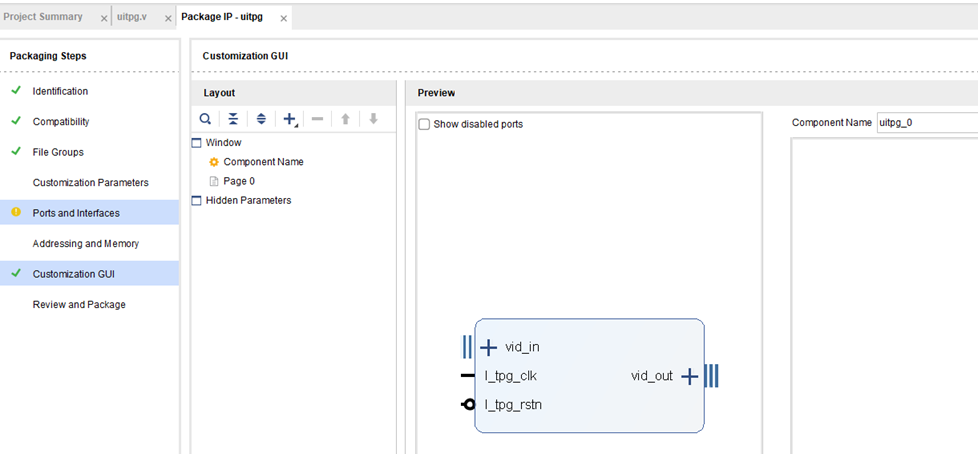

3.4 Customization GUI的调整

可以看到,我们没有需要调整的参数,默认就这样

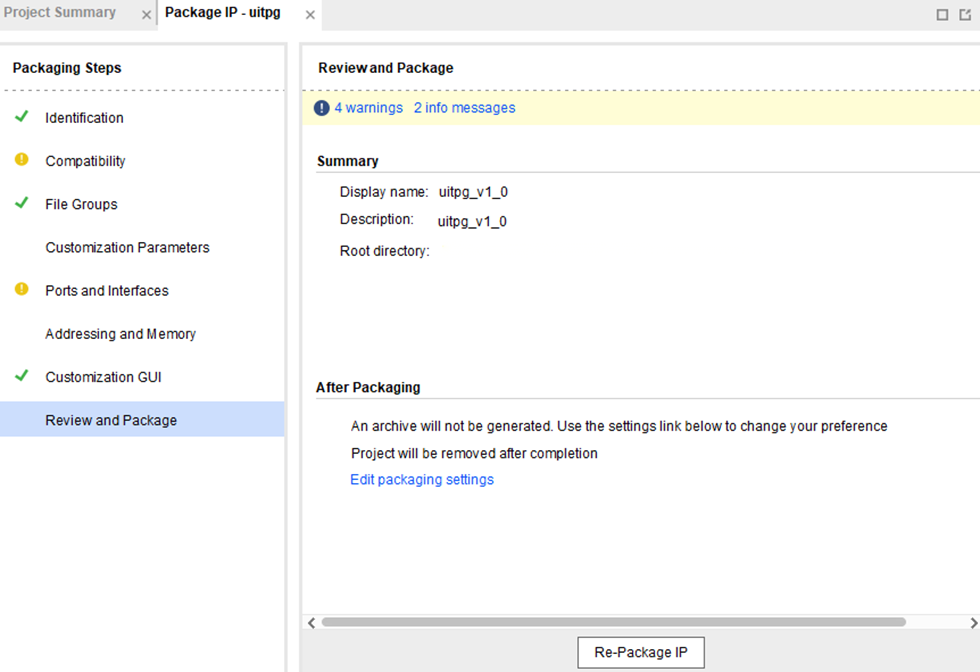

3.5 完成封装

单击Re-Package IP 完成封装

4 HDMI IP封装总线接口

本文不再赘述和前一篇封装IP相同的内容部分,如果有不清楚请阅读前文"VIVADO自定义IP简单封装方法"。

HDMI IP 中有一个下拉列表的设置,是本节内容的重点。

4.1 vid_in总线封装

HDMI有一个视频时序输入接口,因此需要定义一个slave形式的视频时序总线接口,这个和前面VTC的vid_in设置一样,不再重复。

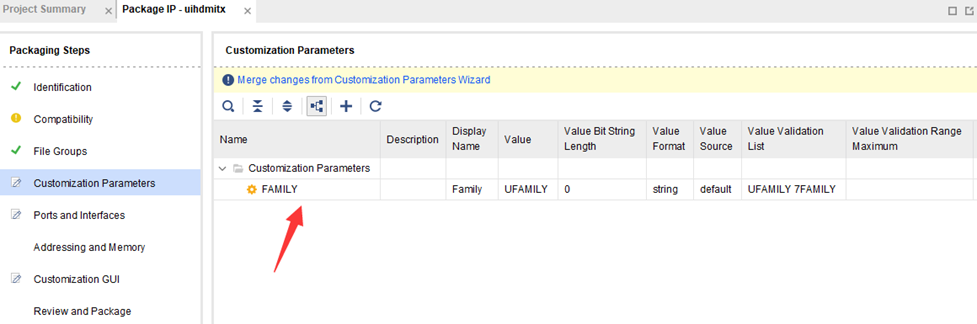

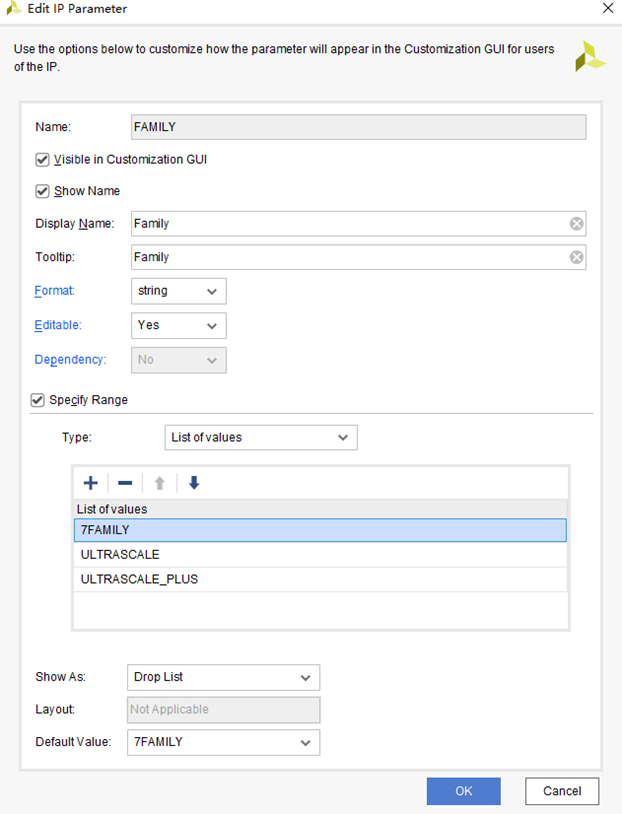

4.2 下拉列表设置

由于XILINX的serdes2和serdes3不一样,所以需要一个下拉列表可以选中

设置FAMILY类型包括:

ULTRASCALE, ULTRASCALE_PLUS和7FAMILY

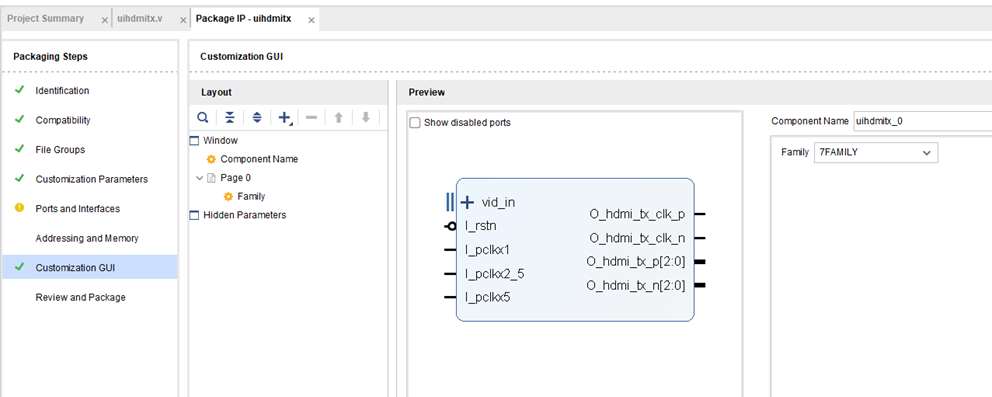

封装完成后的界面

用同样的方法封装其他的IP,比如AD7606的IP ,ADV7611驱动的IP ,LVDS触摸屏的IP等等,这里不再重复。

下一节课实验使用本节课完成的IP,大家之前用传图方法实现的HDMI测试图形输出