一个低噪声放大器(LNA)的核心指标就是噪声系数和增益以及稳定性,在整个有用频率范围内不会振荡,且这种放大器的典型工作状态是A类,其特征是偏置点大约处于所使用器件的最大电流和电压能力的中心。

特别是在接收机应用中,前置放大器的噪声系数需要尽可能低,在整个系统的噪声特性上,接收机前端的第一级起决定性作用。对于一个放大器,通常不可能同时获得最小噪声和最大增益,所以必须进行某种程度的折中。因为以上原因往往放大器的第一级不需要做阻抗匹配,只需要获得尽可能小的噪声即可。

低噪声放大器都是按照噪声最佳匹配进行设计的,噪声最佳匹配点并非最大增益点,因此增益G要下降。噪声最佳匹配情况下的增益称为相关增益。通常,相关增益比最大增益大概低2~4dB。

(1)噪声系数NF

放大器的噪声系数NF定义如下:

噪声系数的物理含义是:信号通过放大器之后,由于放大器产生噪声,使信噪比变坏,信噪比下降的倍数就是噪声系数。

多级级联放大器的噪声系数公式:

可以看出第一级噪声系数对整个系统的噪声特性贡献最大。

(2)灵敏度

从上式中可以看出,一旦系统带宽和信噪比确定了,对系统的灵敏度起决定性作用的就只有NF了。

1、设计目标

①工作频率2.4~2.5 GHz ISM频段

②噪声系数NF<0.7dB

③增益Gain>15dB

④输入驻波VSWRin<1.5,输出驻波VSWRout<1.5

2、设计步骤

总览:

(1)下载并安装晶体管的库文件以及所需的S2P文件

(2)直流扫描分析

(3)偏置电路设计

(4)稳定性分析

(5)噪声系数圆和输入匹配

(6)最大增益的输出匹配

(7)匹配整体参数优化

(8)版图的设计

(9)原理图——版图联合仿真(co-simulation)

(10)非线性分析

(1)下载并安装晶体管的库文件

下载该晶体管的ADS模型(atf54143_010407.zap),然后进入ADS主界面,执行菜单命令【File→Unarchive Workspace or Project】,释放此文件(系统自动新建一个工程文件)

释放后得到原理图文件和symbol

(2)直流分析DC Tracing

设计LNA的第一步是确定晶体管的直流工作点

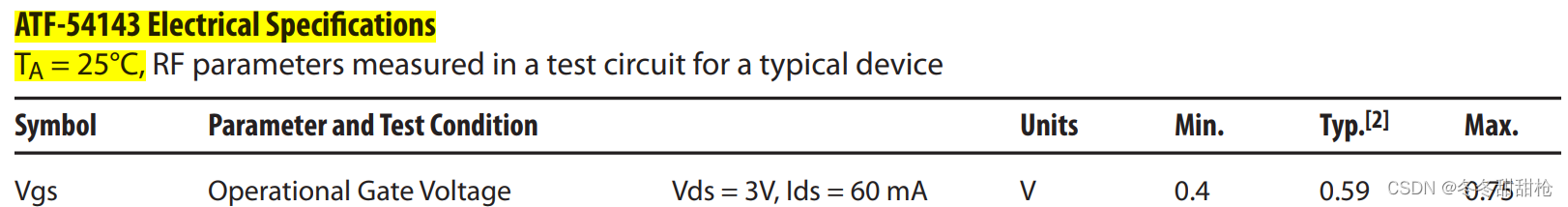

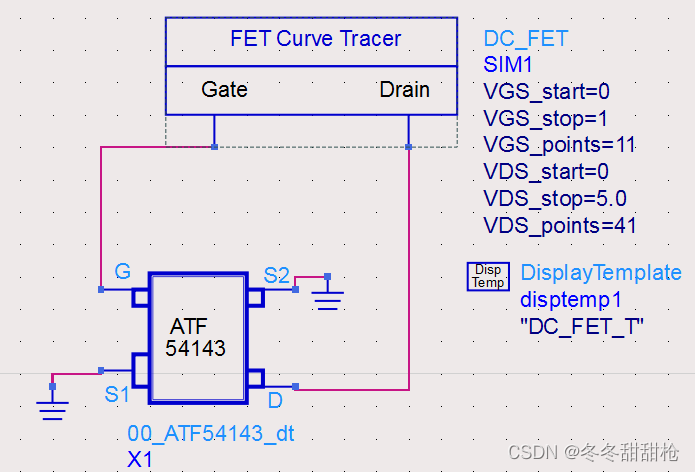

根据datasheet大致设置静态工作点的参数扫描范围:Vgs:0~1V,Vds:0~5V

插入DC_FET_T模版,把atf54143的symbol拖动到原理图中

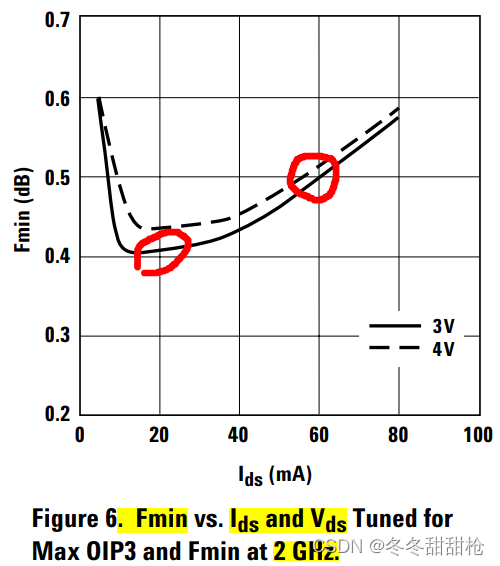

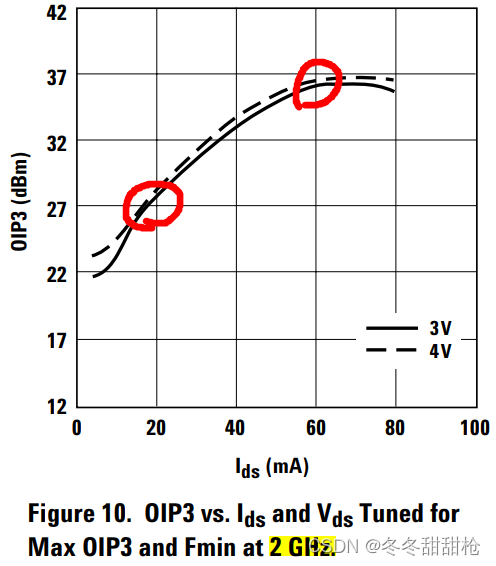

后续查看datasheet,可以看到噪声、增益、OIP3与Vds和Igs的关系,从而确定晶体管工作点

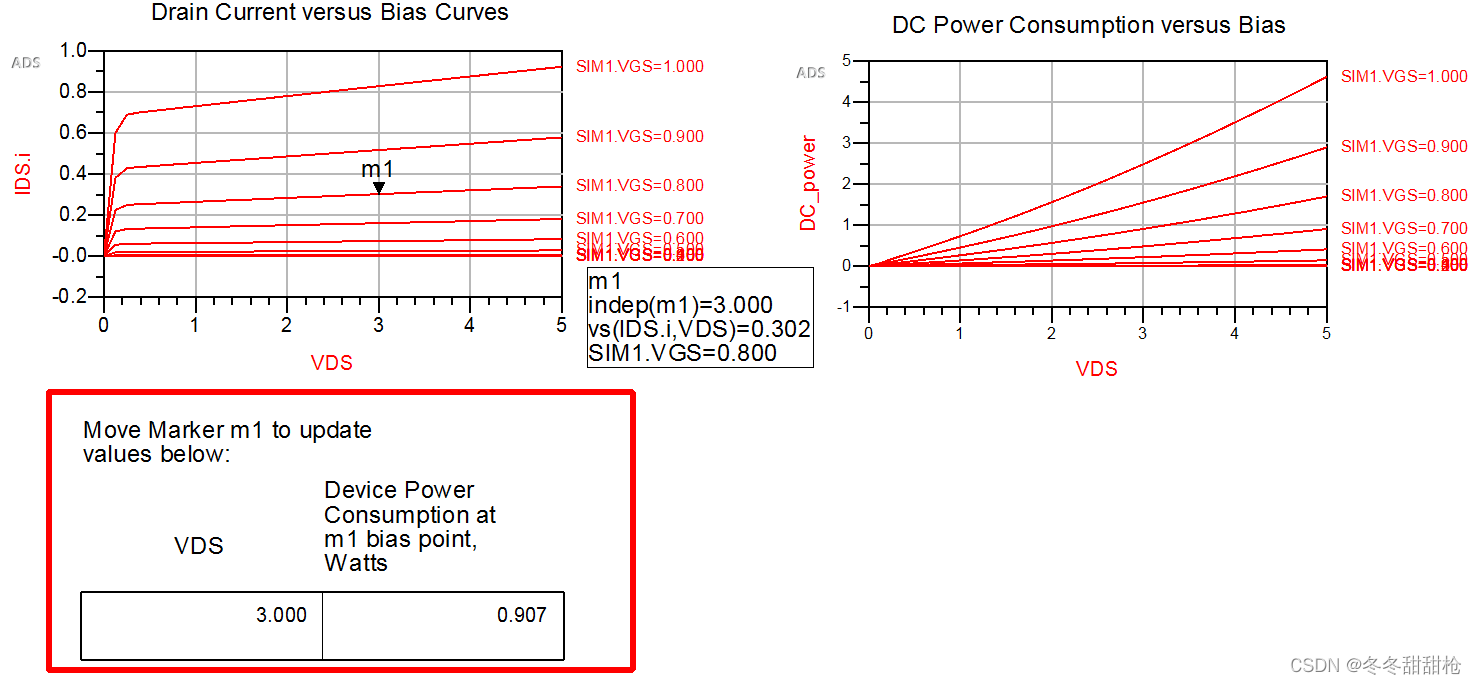

可以看到,在2GHz的时候,当Vds=3V且Ids=60mA时,Fmin仅仅比Ids=20mA时高了0.1dB,但是OIP3却高出了很多。综合考虑,ATF54143直流工作点就设为Vds=3V、Ids=60mA。

由于后面报错:The default dataset for this display does not match the dataset produced by the simulation. Would you like to change the default dataset from,所以在进行直流分析后将该Cell删除。

(3)偏置电路的设计

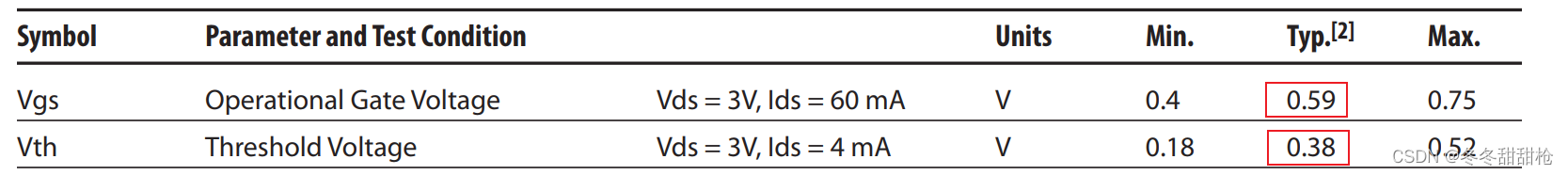

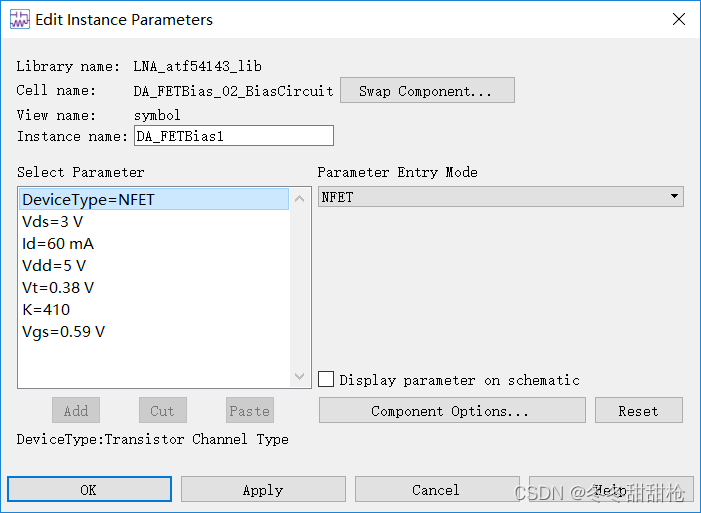

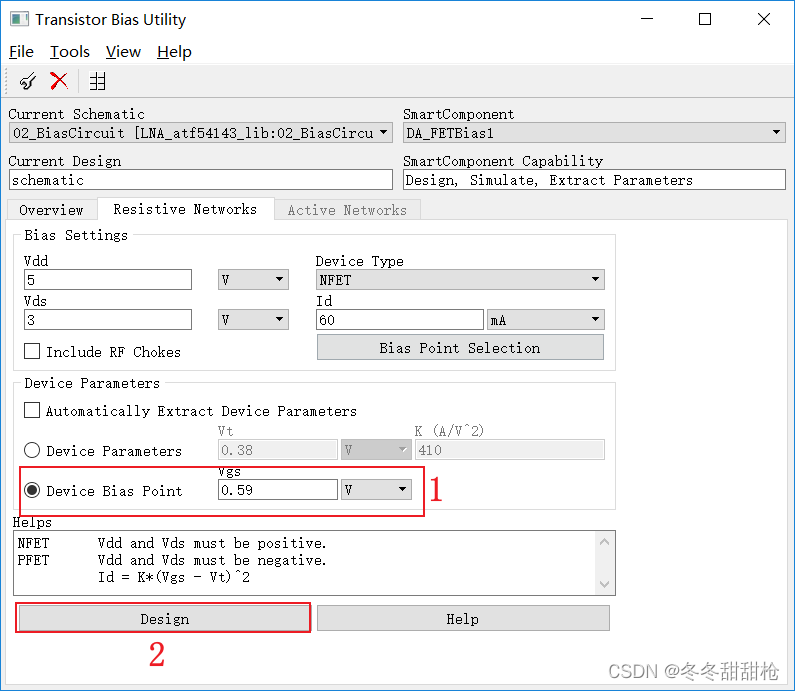

第一阶段:在工具栏的控件下拉菜单中选择"Transistor Bias",双击"DA_FETBias1",进行参数设置

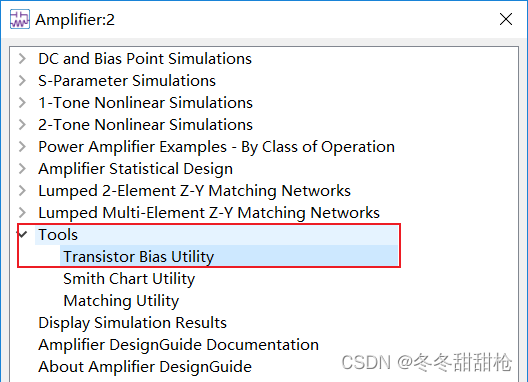

自动设计偏置电路【Design Guide→Amplifier→Tools→Transistor Bias Utility】

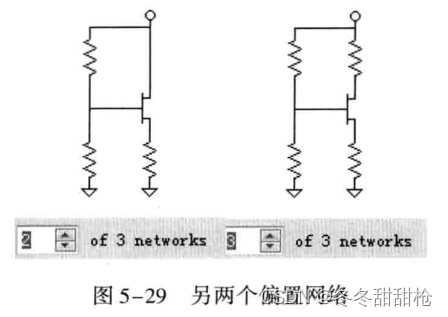

在“Bias Network Selection”对话框里面有3个偏置网络可以选择,在另外两个偏置网络里面,晶体管的源极是有电阻的,但通常在LNA的设计中,S极只接反馈电感(微带线),所以选用第一个偏置网络。

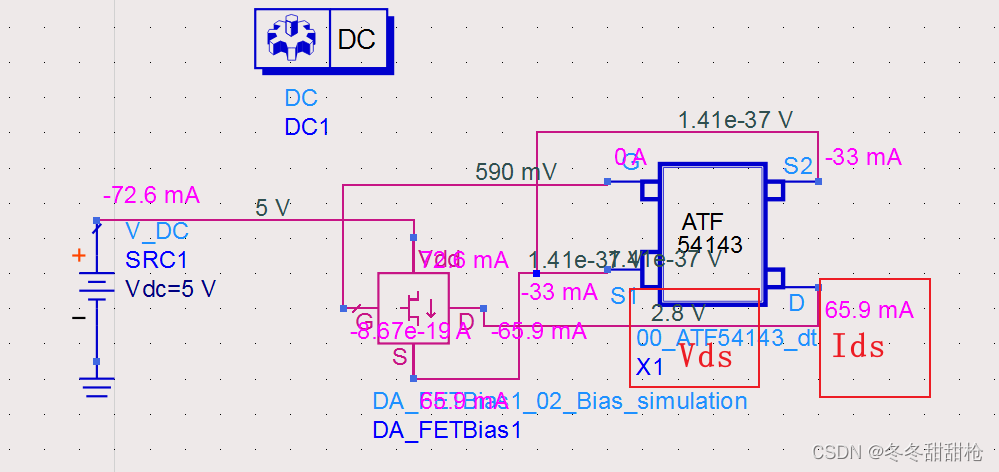

自动生成的偏置电路:

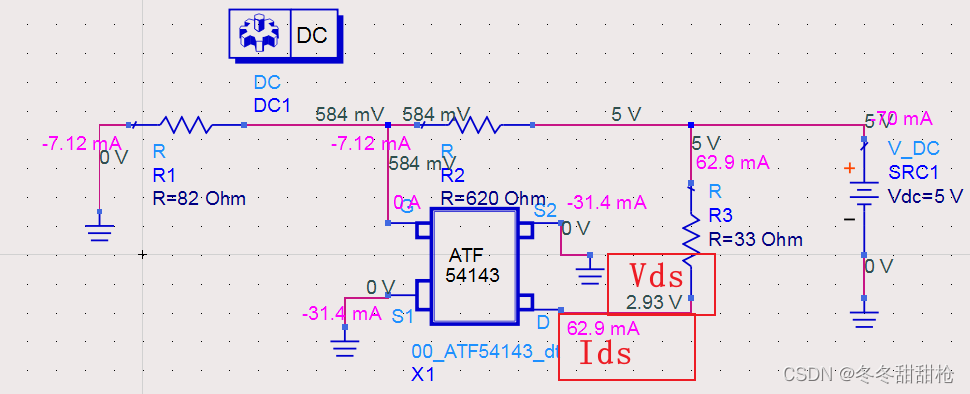

加DC控件进行仿真,【Simulate→DC Annotation→Annotation voltage/Annotation Pin Current】显示各节点电压和电流值

由于电阻值R1、R2和R4不是常规标称值,后面会用相近的常规标称值电阻代替。

第二阶段:用常规标称电阻值重建原理图

(4)稳定性分析

第一阶段:

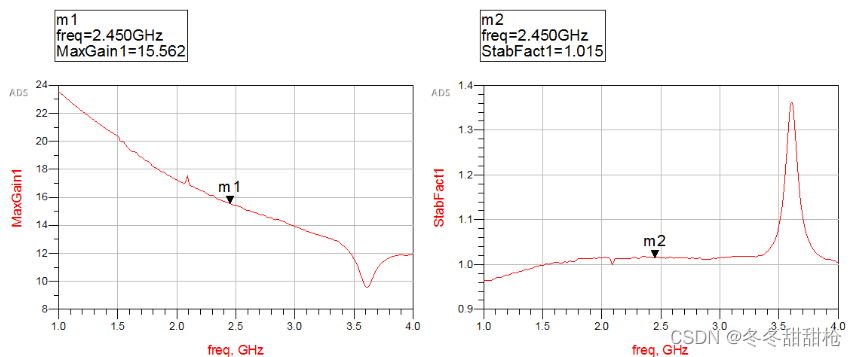

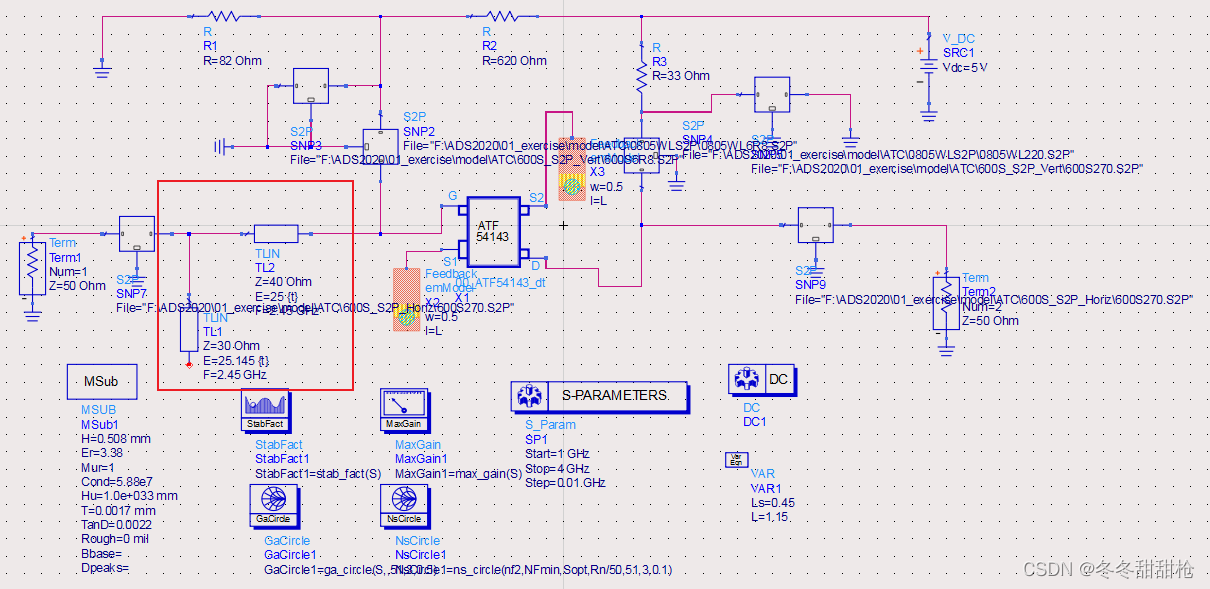

从晶体管放大器理论可知,只有绝对稳定系数K>1,放大器电路才会稳定,直接仿真K<1,不稳定。使系统稳定的最常用的办法就是加负反馈,本例在PHEMT的两个源极加小电感作为负反馈。

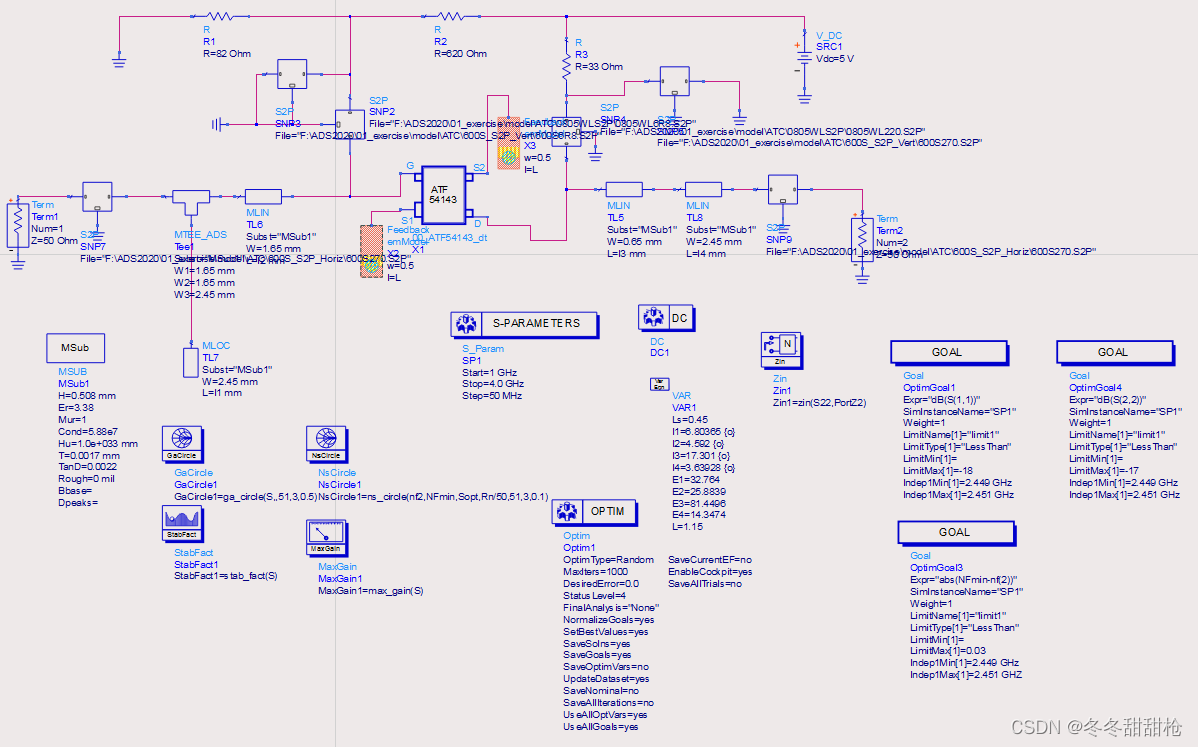

第二阶段: 下面就把理想的DC_Feed元器件改成实际真实的器件,选用ATC公司的电容和电感。在原理图中,晶体管栅极扼流电路采用ATC0806WL6R8的串联电感和ATC600S270的旁路电容,隔直电容用ATC600S270。注:vert旁路电容,horiz隔直电容

第三阶段:把晶体管源极的两个接地电感换成短路微带线。一方面是因为这两个电感值太小(0.45nH),实际的分立电感很难做到;另一方面是因为从调节这两个电感值就可以发现,这两个电感值很小的改变,就会对整个电路的稳定性产生很大的影响。由于分立电感本身的误差和寄生参数等影响太大,所以用微带线来代替。

用微带线就需要知道微带线的长度和宽度:

式中,l是微带线的长度(单位inch);L是电感值(单位nH),Zo就是PCB上微带线的特征阻抗。同时这里采用RO4003射频板,=3.38

首先设定微带线宽度为0.5mm,利用Start Linecale工具算出特征阻抗为79Ohm,在利用上述公式算出长度为0.92mm(1in=25.4mm)

因为考虑了接地过孔等因素,所以相对更精确。再次调节变量L的值,得到一个更满意的稳定性系数。这里设置L=1.15。

(5)噪声系数圆和输入匹配

在这之前要了解nf,nf(1),nf(2),NFmin的区别

1、一般对于两端口器件来说,NFmin是器件能达到的最小噪声系数,nf(2)是实际的噪声系数。

2、nf就是nf(1)和nf(2),就像S参数的S一样,nf(1)就是1端口的噪声,通常我们仿真时是1端口是放大器的输入,2端口是输出,那么nf(2)就是真正的噪声。如果2端口输入,1端口输出,nf(1)就是我们要的噪声。

3、同样的,当仿真4端口器件时,就会出现nf(3)以及nf(4)。

总结:噪声系数(nf)的数量和S参数类似,跟端口数量有关系。

第一阶段:

仿真噪声系数(NFmin)需要在S参数仿真控件里把计算噪声的功能打开

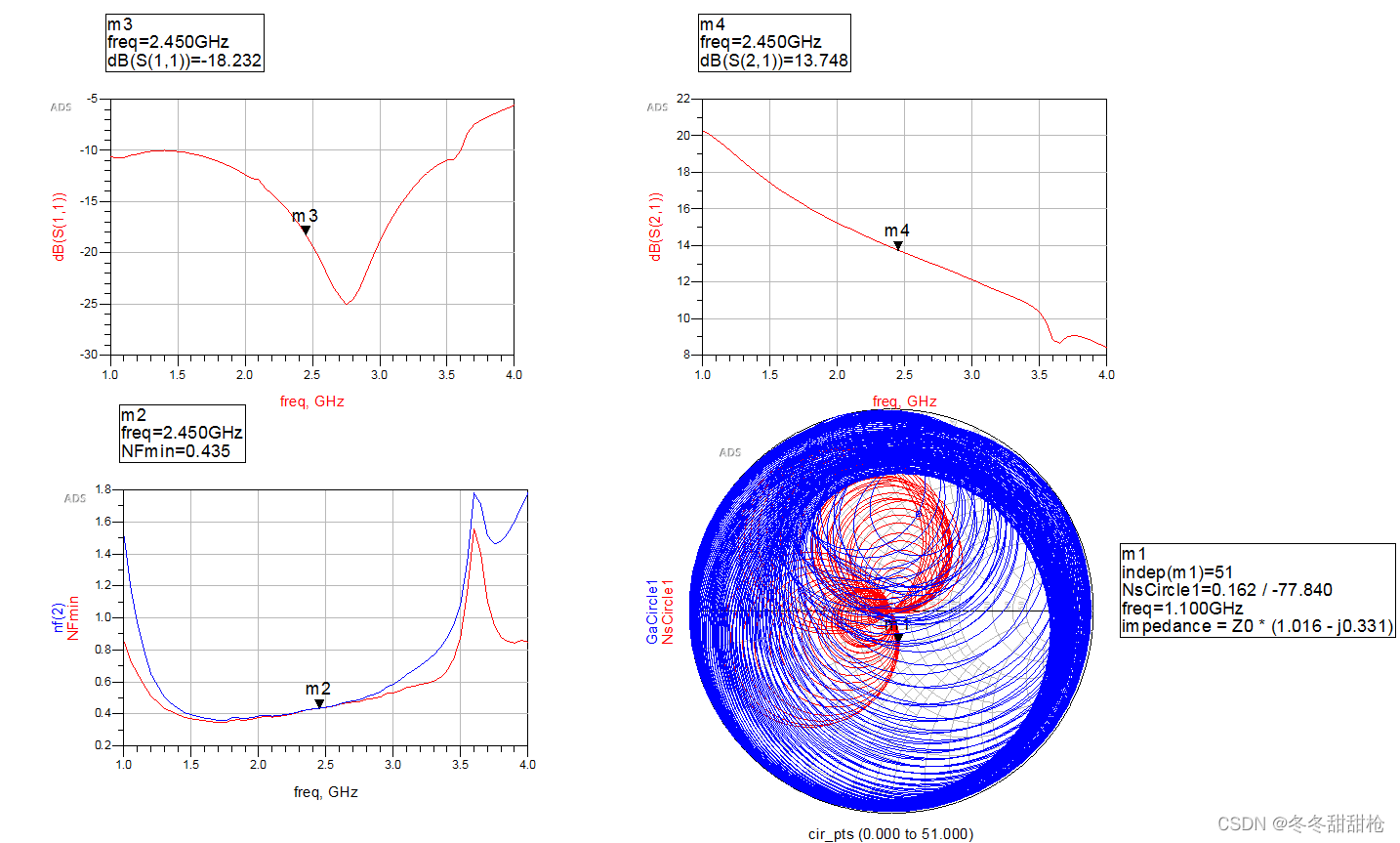

从NFmin的图上可以看出,2.45GHz时最小的噪声系数为0.442dB。接下来就是要设计一个适当的输入匹配网络来达到这个最小噪声。

第二阶段:

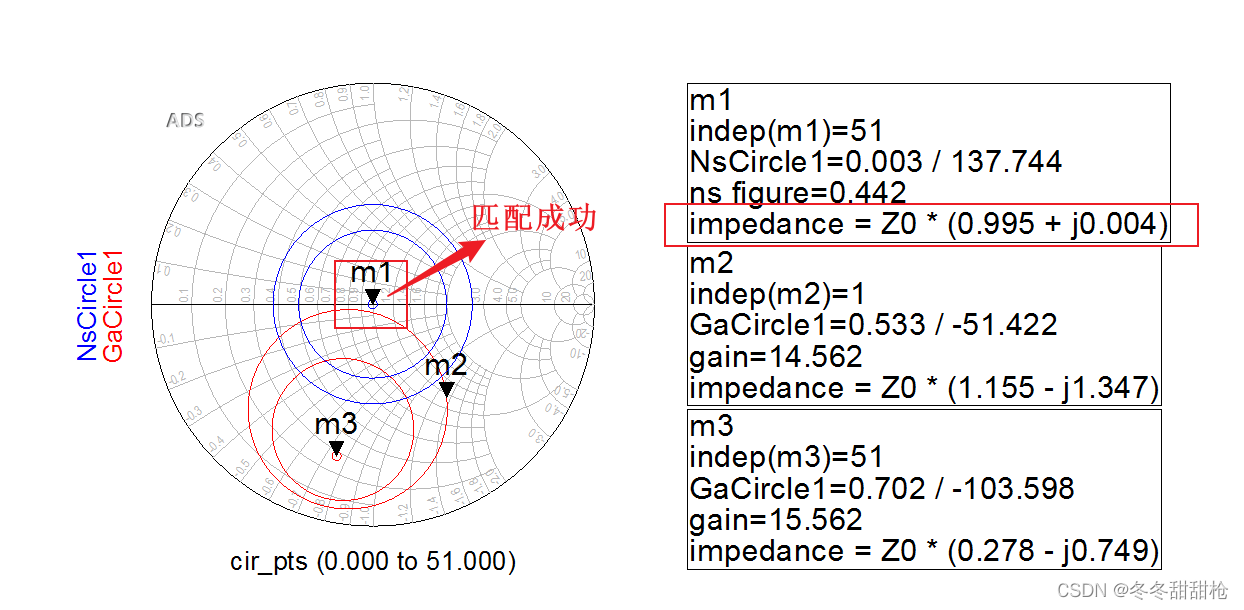

设置S-Parament仿真控件为单频点仿真,频点为2.45GHz

加入“NsCircle”和“GaCircle”控件,“NsCircle1=ns_circle(,NFmin,Sopt,Rn/50,51,3,0.1)”,返回该频率的NFmin、NFmin +0.1dB、NFmin+0.2dB的3个等噪声圆,“GaCircle1=ga_circle(S,,51,3,0.5)”,返回该频率的maxgain、Maxgain-0.5dB、Maxgain-1dB的3个等增益圆。

上图中,m1是LNA有最大增益时的输入端阻抗,此时可获得增益约为15.6dB;m2为LNA有最小噪声系数时的输入端阻抗,此时可获得最小噪声指数为0.442dB。但是这两点并不重合,即设计时必须在增益和噪声指数之间作一个权衡和综合考虑。

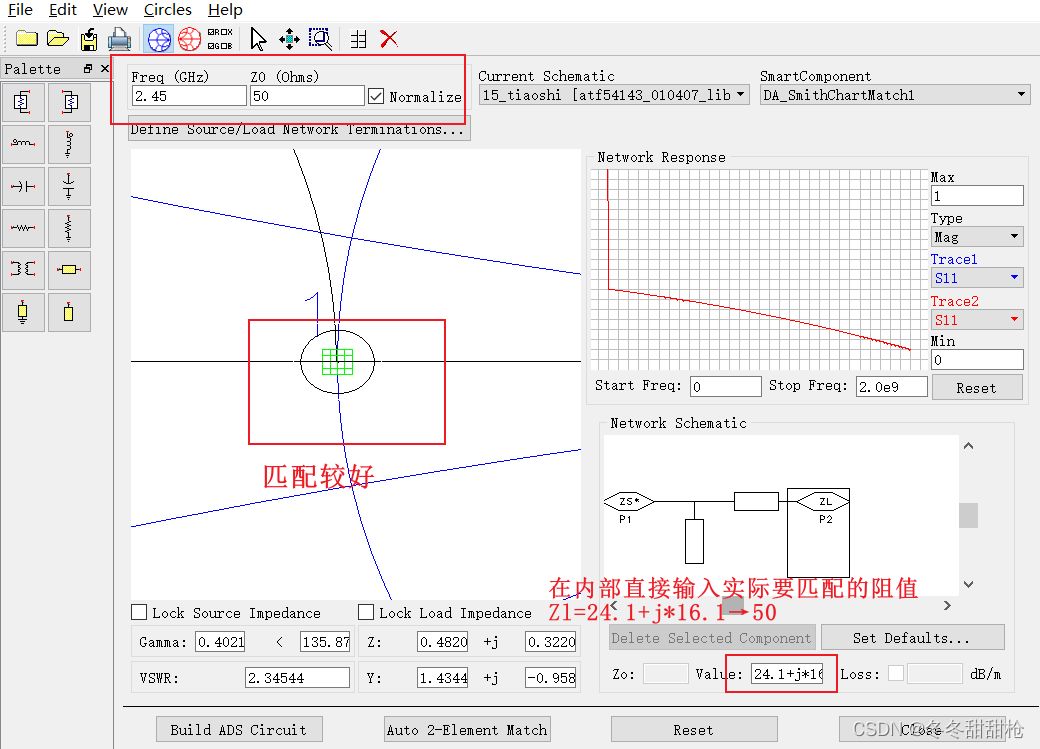

对于低噪声放大器,尤其是第一级放大器,优先考虑噪声系数,所以输入端阻抗就定为m2点的最小噪声系数阻抗Z0*(0.484-j*0.321),其中Z0为50Ohm,输入端阻抗就为24.2-j*16.1Ohm。m2处的增益大约为14.6dB(参考m2旁边的m3点)。为了达到最小噪声系数,在晶体管的输入端需要一个,而整个电路的输入阻抗为Z0=50Ohm,所以需要输入匹配网络把

(m2处阻抗的共轭,即24.2+j*16.1Ohm)变换到输入阻抗50Ohm

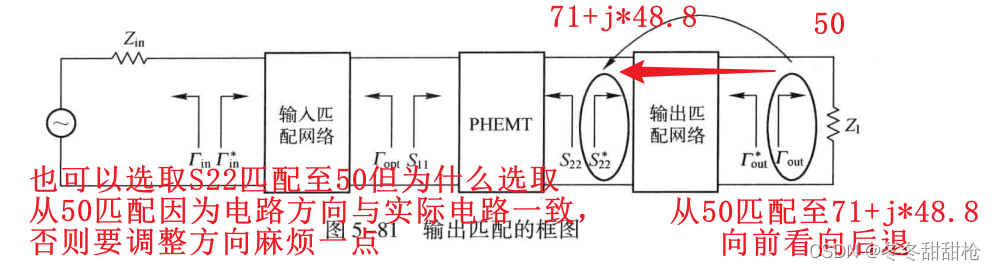

注:往前看往后退是加元件(匹配),而往前看往前退是减元件(错误匹配)

同时注意方向问题:

为从端口处看向网络的输入阻抗类似S11,此处的impedance是从网络看向端口的阻抗,即

单频点检验匹配情况,如下图可见m1已经完全匹配至50Ohm(原理图发生改变,m1点同上面的m2点)

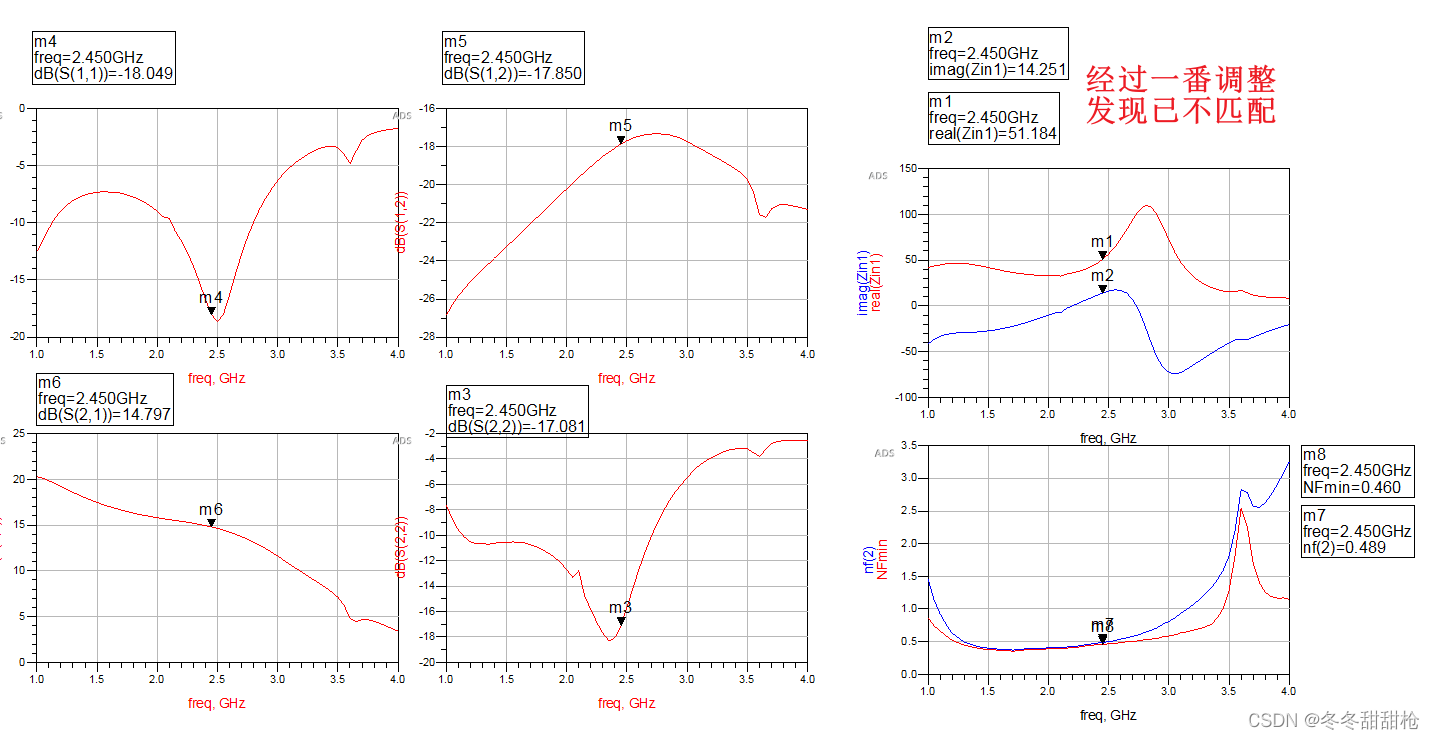

可见整个电路的噪声系数nf(2)在2.45GHz处等于NFmin=0.442dB,说明在该点的噪声系数已经达到了最优化。

第三阶段:

在晶体管输入端的隔直电容会导致电路结构复杂,所以需要把隔直电容移到源端即把隔直电容移到输入匹配网络和源端Term之间,同时把匹配后的子电路复制到原理图中,之后再通过调谐两段传输线的长度以致达到一个较小的噪声系数和输入反射系数S11。

(6)最大增益的输出匹配

在一个低噪声放大器里面只有输入匹配电路对噪声系数有影响,输出匹配电路对噪声没有影响。所以,在输出匹配里面主要考虑增益。

第一阶段:

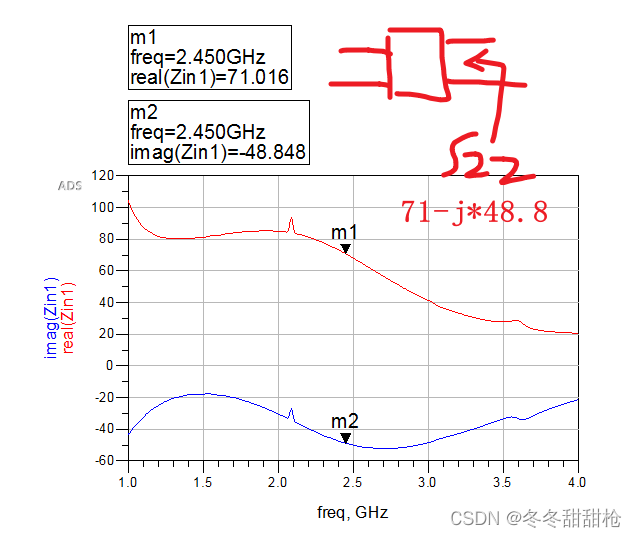

加入Zin控件并设置

第二阶段:

把匹配后的子电路复制到原理图中,同时把理想传输线转换为实际微带线,并进行变量优化使仿真结果达到满意值。

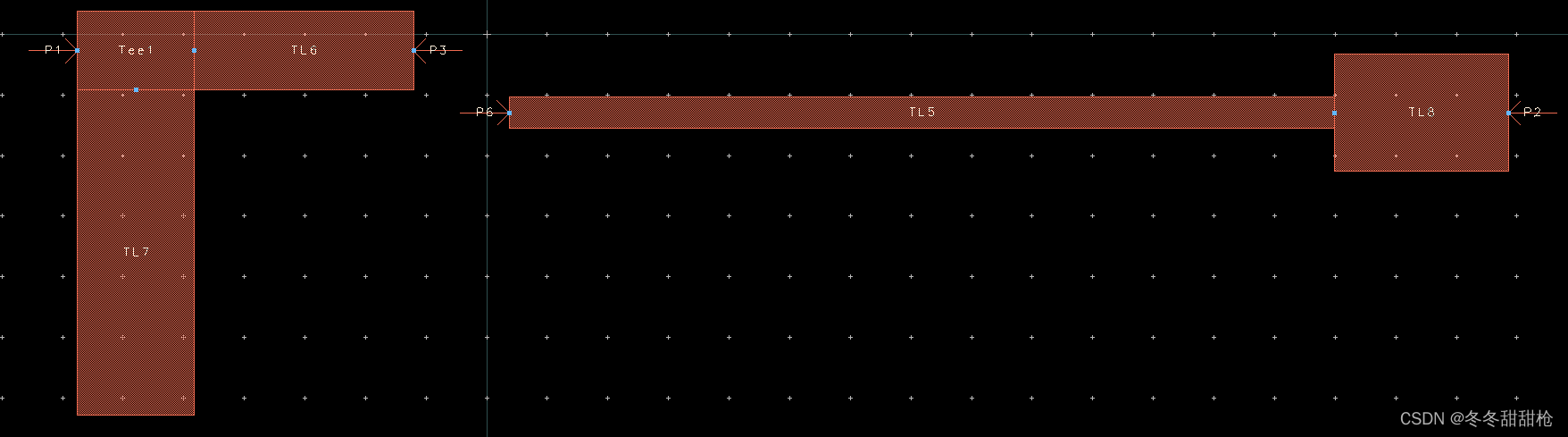

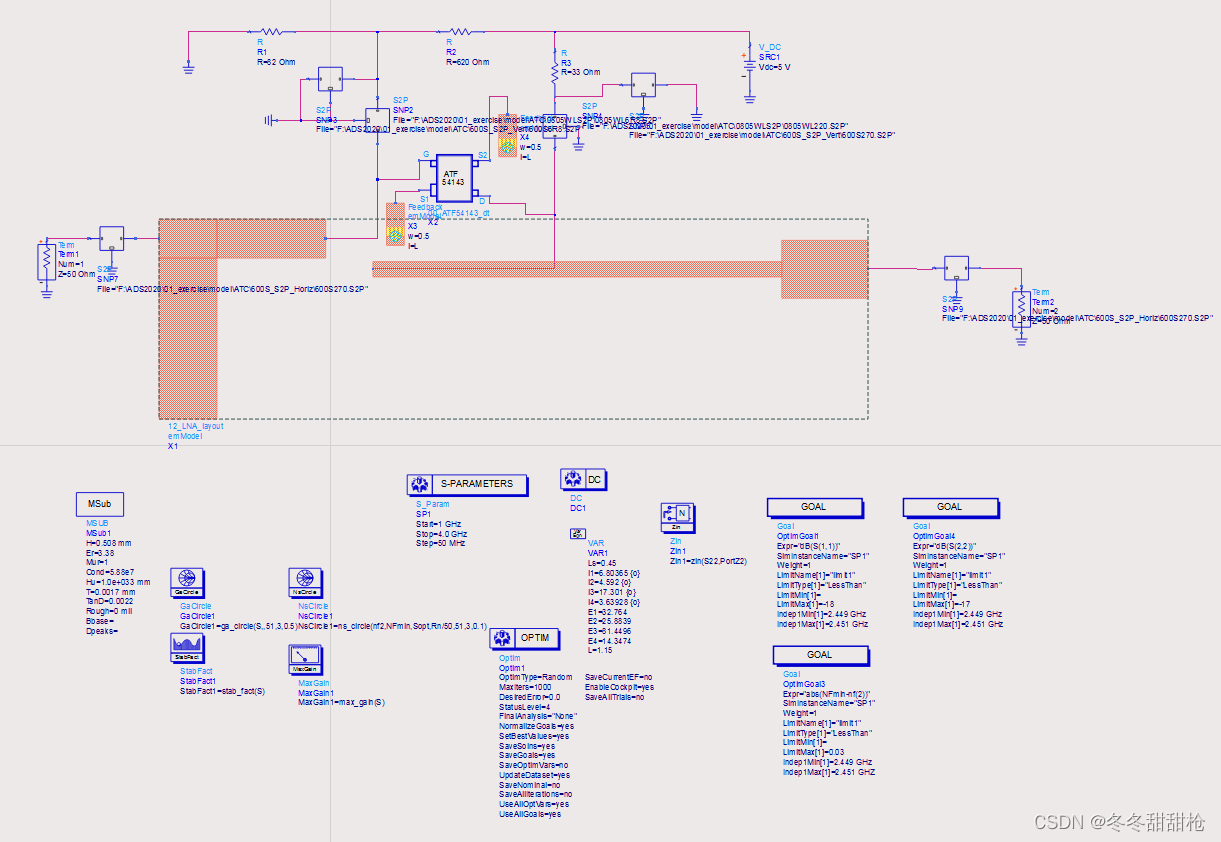

(7)原理图-版图联合仿真(co-simulation)

本文未按照参考书设计,只是把微带线转为实际版图进行联合仿真。

从仿真结果来看,S11和S22在设计频段都在-10dB以下,噪声参数为0.492dB,这与原理图电路仿真有一定的区别,原因主要:①layout在设计的时候,考虑到布线的需要,与原理图layout有一定的区别;②原理图电路在仿真时没有考虑到分立元器件及其走线的分布参数问题,也没有考虑接地的问题(原理图电路等于是理想接地),但没有本质的区别。通常情况下还要对版图进行进一步的修改,在整个LNA的实物做出来以后,也要进行详细的测试和调试工作才能把最终的低噪声放大器的电路确定下来。

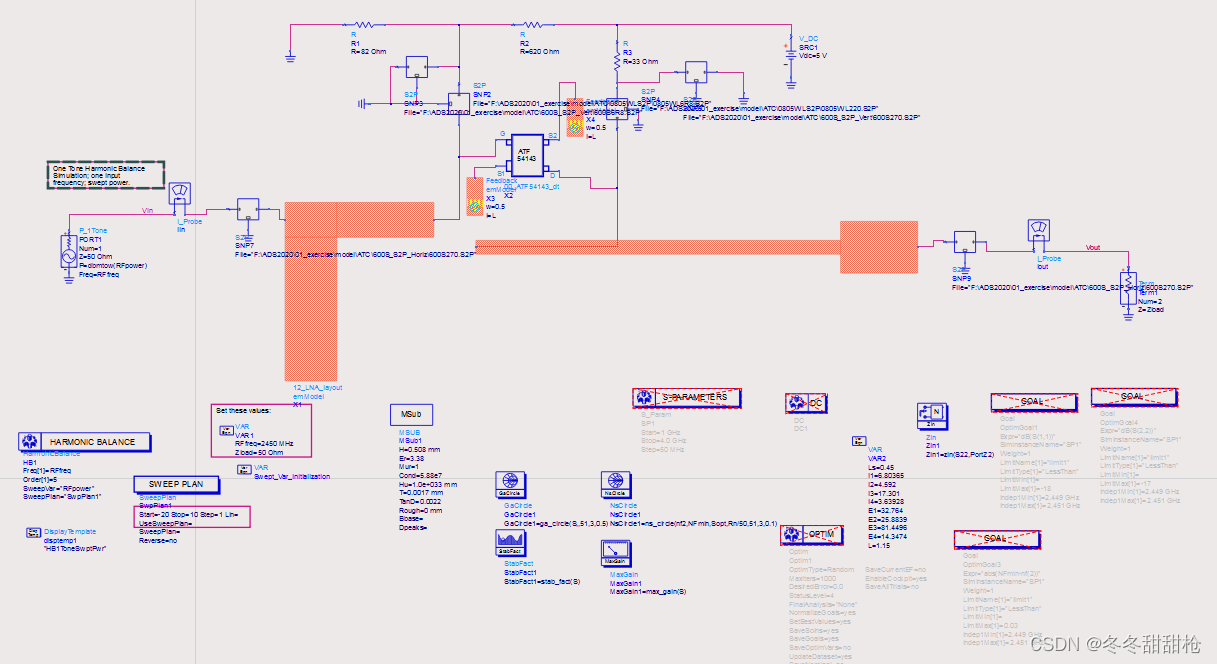

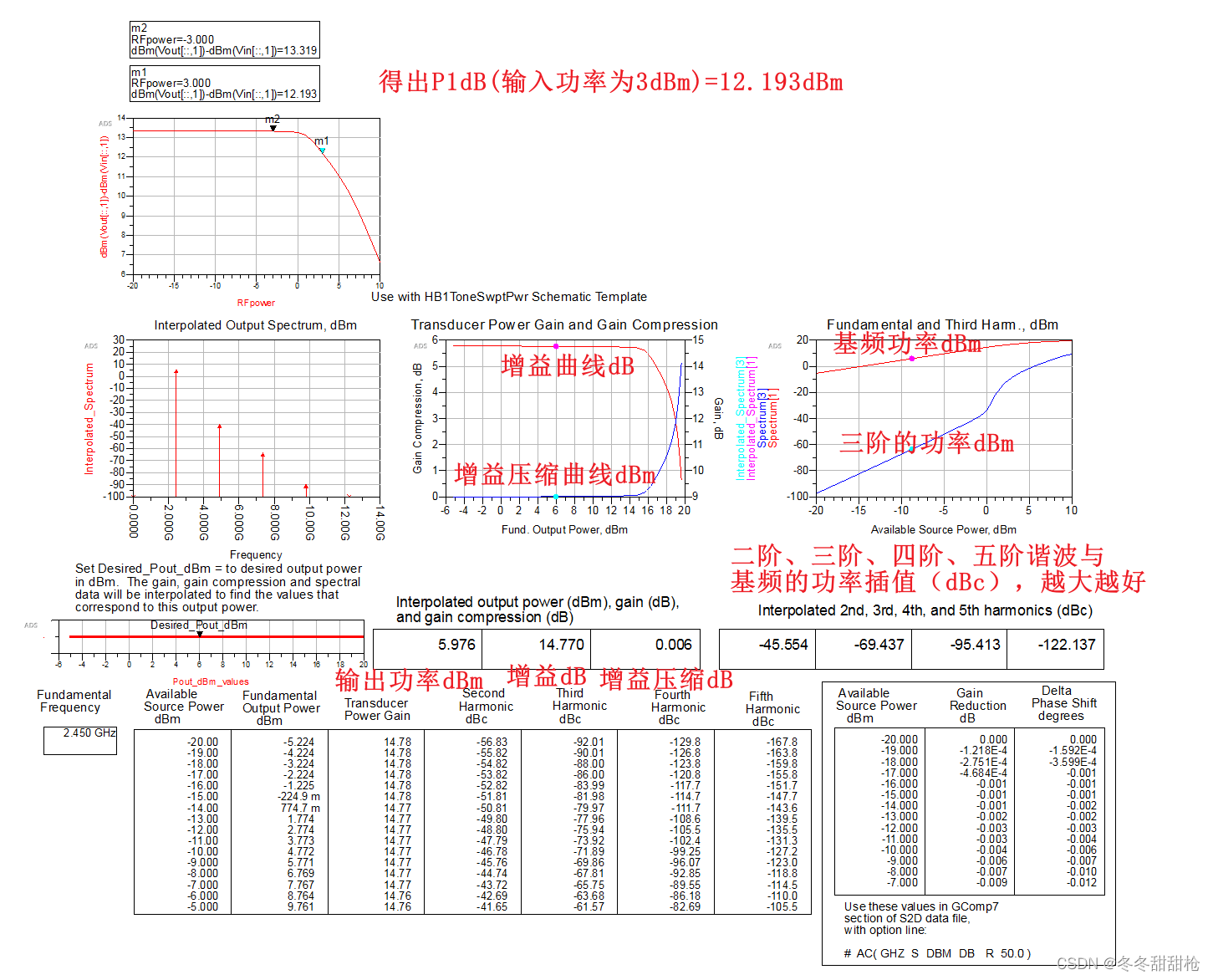

(8)非线性分析(大信号仿真分析:P1dB、IIP3等)

新建原理图,选用HB1ToneSwptPwr模版,并添加节点Vin和Vout,加入电流探针I_Probe,同时插入HARMONIC BLANCE控件,分析到5次谐波(Order=5)

从仿真结果可以得出,该放大器在输出功率为+6dBm以下时,其输出三阶分量抑制为-70dBc以下,随着输入功率增大,输出三阶分量会逐渐恶化,这与放大器使用的晶体管ATF54143作为一个低噪声小信号晶体管的特性是相符的。小信号低噪声晶体管一般在接收通道中作为前端使用,自身的三阶交调抑制是有限的,也不作为设计的一个首要指标。接收通道的低噪声放大器前加限幅器或者衰减器都是为了照顾低噪声放大器此项特性。如果仿真的是一个中功率放大器,则其三阶交调性能就是其一个重要性能。