相关文档:《《ARM Generic Interrupt Controller Architecture version 2.0》阅读笔记》。

Chapter 1 Introduction

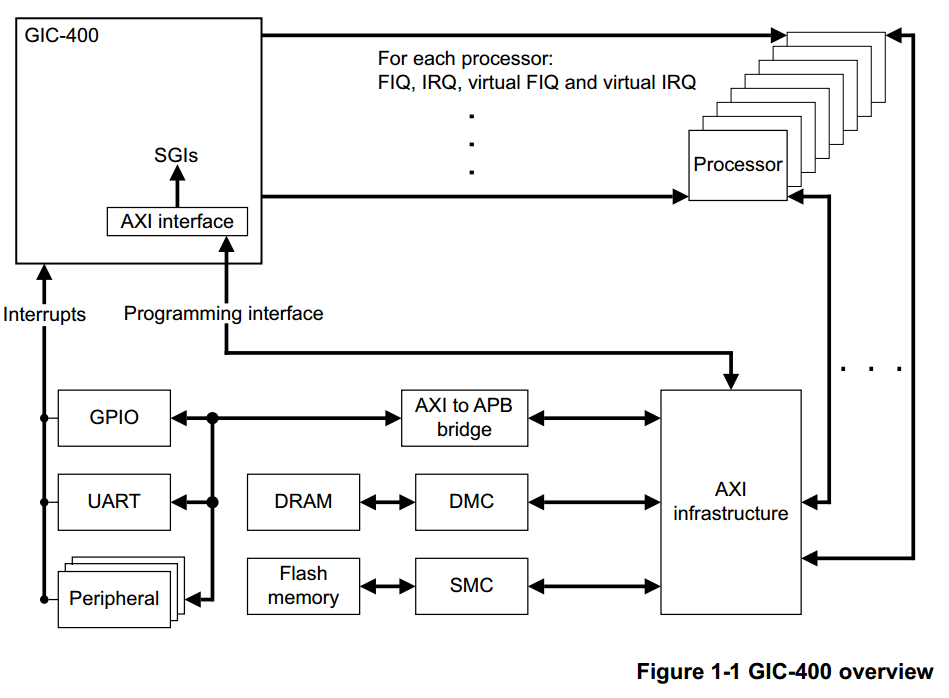

1.1 About the GIC-400

GIC400负责检测、管理、分发中断。

软件可以对GIC400相关中断进行如下配置:

- 使能或关闭。

- 将中断指定为Group 0或Group 1。

- 分配优先级。

- 在多核环境下,将中断发送到不同核。

- 配置为电平触发或边沿触发。

GIC400其他实现:

- 安全相关扩展:

- 使用Group 0作为安全中断,使用Group 1作为非安全中断。

- 使用FIQ中断请求发送安全中断到相关核。GIC400常使用IRQ中断请求来产生Group 1中断。

- 虚拟化扩展:提供相关硬件管理虚拟化中断。

GIC400的中断类型:

- 16个SGI

- 每核提供6个外部PPI

- 每核提供1个内部PPI

- 可配置数量的SPI,范围从0~480,以32为单位。比如0、32、64、480。

1.3 Interfaces

GIC400支持AMBA AXI4从设备接口,可以通过此对Distributor(包括产生SGI)、CPU interface和Virtual CPU interface进行编程。

1.4 Configurable options

GIC400可配置选项包括:

- NUM_CPUS:SOC中CPU数量,从1到8。此参数决定了CPU interface和virtual CPU interface数量。每个CPU配备一个CPU interface和virtual CPU interface。

- NUM_SPIS:SPI中断数量,从0到480,必须是32倍数。

- NUM_RID_BITS:Width of the AXI ID signals for reads.Value must be at least 1.

- NUM_WID_BITS:Width of the AXI ID signals for writes.Value must be at least 1.

Chapter 2 Functional Description

2.1 Functional overview of the GIC-400

GIC400由Distributor、每个处理器一个CPU interface和虚拟CPU interface组成。

GIC400功能模块:

- Clock and reset

- AXI4 interface

- Distributor

- CPU Interface(每CPU一份)

- Virtual interface control registers(每CPU一份)

- Virtual CPU interface(每CPU一份)

2.1.3 Distributor

GIC400 Distributor接收中断并将最高优先级pending中断送到每个CPU interface。

2.1.4 CPU interfaces

CPU interface将中断信号送到对应的处理器,接收响应和处理器的EOI访问。

CPU interface仅将足够高优先级的中断信号送到响应处理器。一个中断是否拥有足够高优先级取决于CPU interface配置和活跃中断的特定优先级。

2.1.5 Virtual CPU interfaces and virtual interface control registers

GIC400一些功能组件和软件组合形成了类似硬件Distributor的virtual Distributor。

Hypervisor和virtual interface control寄存器组成了一个virtual distributor:

- Hypervisor为物理中断创建了虚拟中断并分配优先级。

- 每组virtual CPU interface寄存器给virtual中断按优先级排序,并将最高优先级pending中断转发到对应virtual CPU interface。

2.2 Secure and Non-secure access to the GIC-400

2.3 Interrupt inputs to the GIC-400

| 中断类型 | 中断序号 | 中断数 | 解释 | 触发条件 |

|

SGI Software Generated Interrupt |

0-15 | 16 | 每个CPU interface可以产生16个 SGI中断到每一个目标处理器。 | 软件写寄存器 |

|

PPI Private Peripheral Interrupt |

16 | 一个指定到单一处理器的中断。 | 低电平触发 | |

|

SPI Shared Peripheral Interrupt |

32-511 | 480 | 可以指定送到一个或多个CPU。 | 上升沿触发或者高电平触发 |

|

LSPI Lockable SPI |

32-X | 31(可配置) | 默认为安全中断。 |

2.6 Interrupt handling and prioritization in the GIC-400

- GIC400支持安全状态下32优先级和非安全状态下16优先级。

- 如果多个相同优先级中断同时产生,仲裁依赖于中断类型:

- PPI、SPI

- SGI

- 写中断优先级寄存器不能对active中断立即生效。

2.7 Power management

Bypass

2.8 Behavior when the Distributor is disabled

如果GICD_CTLR.EnableGrp0或者GICD_CTLR.EnableGrp1之一被关闭,那么:

- 去使能组内边沿触发中断信号不能使中端设置为pending状态。

- 去使能组内SGI不能被设置为pending状态。

- 去使能组内电平触发中断输入信号被屏蔽。

如果GICD_CTLR.EnableGrp0和GICD_CTLR.EnableGrp1仅有一个被置为1,并且最高pending优先级中断在关闭的组内,那么Distributor不会转发任何中断到CPU interface。

- GICD_CTLR.EnableGrp0=0并且GICD_CTLR.EnableGrp1=1,最高pending优先级中断在Group 0。

- GICD_CTLR.EnableGrp0=1并且GICD_CTLR.EnableGrp1=0,最高pendign优先级中断在Group 1。

这就造成当Group 1中断优先级高于Group 0时,非安全软件通过设置GICD_CTLR.EnableGrp1=0,即可阻止安全软件处理中断服务。为了阻止这种情况发生ARM强烈建议:

- 所有Group 0中断优先级高于Group 1中断。

- 安全软件必须确保当GICD_CTLR.EnableGrp1=1时,必须设置GICD_CTLR.EnableGrp1=1;没有pending的Group 0中断。

Chapter 3 Programmers Model

3.2 GIC-400 register map

GIC400寄存器前缀:

- GICD_ Distributor

- GICC_ CPU interfaces

- GICH_ Virtual interface control blocks

- GICV_ Virtual CPU interfaces.

3.2.1 GIC-400 register access and banking

GIC400对寄存器根据安全和非安全划分如下几种:

- GICD_CTLR和GICC_CTLR属于security Banked,对安全和非安全提供独立的寄存器。

- GICD_IGROUPRn之类寄存器,仅提供安全访问。非安全无法访问。

- 非安全访问仅供安全访问的寄存器或者其一部分会导致RAZ/WI。

3.3 Distributor register summary

GICD_CTLR:是否将pending中断从Distributor送到CPU Interface的全局开关。

GICD_TYPER:定义了LSPI数、是否支持安全扩展、CPU Interface数、最大中断数。

GICD_IIDR:Distributor版本号。

GICD_IGROUPRn:每个中断一位,1表示中断属于Group0,0-表示中断属于Group1。

GICD_ISENABLERn:写1使能,写0无影响。读1表示使能,读0表示去使能。

GICD_ICENABLERn:写1去使能,写0无影响。读1表示是能,读0表示去使能。

GICD_ISPENDRn:写1使中断pending,写0无影响。读1表示中断至少在一个CPU pending,读0表示中断未在任何CPU pending。

GICD_ICPENDRn:写1清中断pendign,写0无影响。读1表示中断至少在一个CPU pending,读0表示中断未在任何CPU pending。

GICD_ISACTIVERn:写1使中断active,写0无影响。读1表示中断处于active,读0表示中断deactive。

GICD_ICACTIVERn:写1使中断deactive,写0无影响。读1表示中断处于active,读0表示中断deactive。

GICD_IPRIORITYRn:每个中断8位,配置中断优先级。

GICD_ITARGETSRn:GICD_ITARGETSR为每个中断提供8位目标CPU控制器。对应位为1表示送到对应CPU。

GICD_ICFGRn:每个中断两位,高位表示中断触发方式:0-level,1-edge。低位表示SPI/PPI处理模式:0:N-N模式,1:1-N模式。

GICD_NSACRne:安全软件允许某一个核上非安全软件产生并管理一个Group0中断。

GICD_SGIR:只写,控制SGI中断送达CPU方式。

GICD_CPENDSGIRn:一个SGI对应8位,写1清对应核的SGI pending,写0无影响。

GICD_SPENDSGIRn:写1设置对应核的SGI pending,写0无影响。

GICD_PPISR:只读,显示PPI的Active状态。

GICD_SPISRn:只读,显示SPI中断电平高低。0表示low,1表示high。

GICD_PIDRn:

GICD_CIDRn:

3.4 Distributor register descriptions

3.5 CPU interface register summary

GICC_CTLR:使能CPU对应的CPU interface

GICC_PMR:中断优先级过滤功能,只有优先级高于此寄存器值的中断才能产生信号到CPU。

GICC_BPR:

GICC_IAR:处理器通过读此寄存器获取中断ID,读也产生中断响应。对于SGI中断,还包括产生中断的CPU ID。

GICC_EOIR:表示处理器结束了中断处理。

GICC_RPR:表示大年CPU interface运行优先级。

GICC_HPPIR:获取pending状态最高优先级中断ID。

GICC_ABPR:

GICC_AIAR:Group1中断响应寄存器。

GICC_AEOIR:Group1中断结束写寄存器。

GICC_AHPPIR:Group1 pending状态最高优先级中断ID。

GICC_APR0:

GICC_NSAPR0:

GICC_IIDR:

GICC_DIR:

3.6 CPU interface register descriptions

3.7 GIC virtual interface control register summary

3.8 GIC virtual interface control register descriptions

3.9 GIC virtual CPU interface register summary

3.10 GIC virtual CPU interface register descriptions