控制寄存器(CR0~CR3)用于控制和确定处理器的操作模式以及当前执行任务的特性。

CR0中含有控制处理器操作模式和状态的系统控制标志;

CR1保留不用;

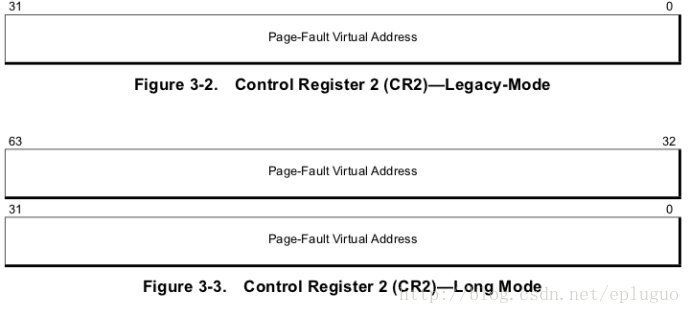

CR2含有导致页错误的线性地址;

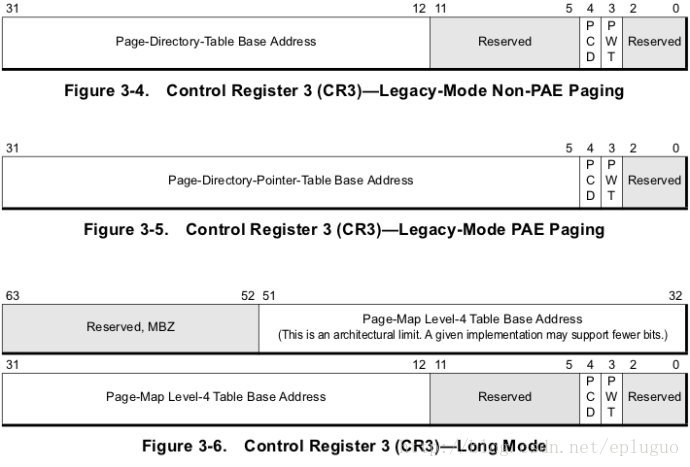

CR3中含有页目录表物理内存基地址,因此该寄存器也被称为页目录基地址寄存器PDBR(Page-Directory Base addressRegister)

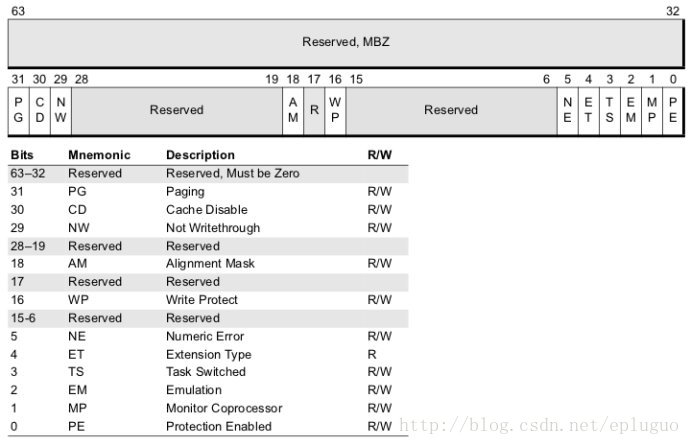

CR0

x86_32的CR0为32bit。X86_64下为64bit,其中低32bit与x86_32的CR0保持一致,高32bit没有定义,作保留使用,除了bit 4其他所有位都是可读可写的。

Protected-Mode Enable (PE) Bit. Bit0. PE=0,表示CPU处于实模式; PE=1表CPU处于保护模式,并使用分段机制。

Paging Enable (PG) Bit. Bit 31. 该位控制分页机制,PG=1,启动分页机制;PG=0,不使用分页机制。

Write Protect (WP) Bit. Bit 16. 该位为写保护控制位,WP=0时,不允许写,WP=1时,允许写

CR2

存放发生页错误时的虚拟地址,格式如下:

CR3

用来存放最高级页目录地址(物理地址),各级页表项中存放的也是物理地址。格式如下:

图3-4中不使用PAE技术,有两层页表。最高层为页目录有1024项,占用4KB。page_directory_table baseaddress为物理地址,指向4KB对齐的页目录地址。

图3-5中,使用PAE技术,三层页表寻址。最高层为页目录指针,4项,占用32B空间。所以 page_directory_table baseaddress为27位,指向32B对齐的页目录指针表。

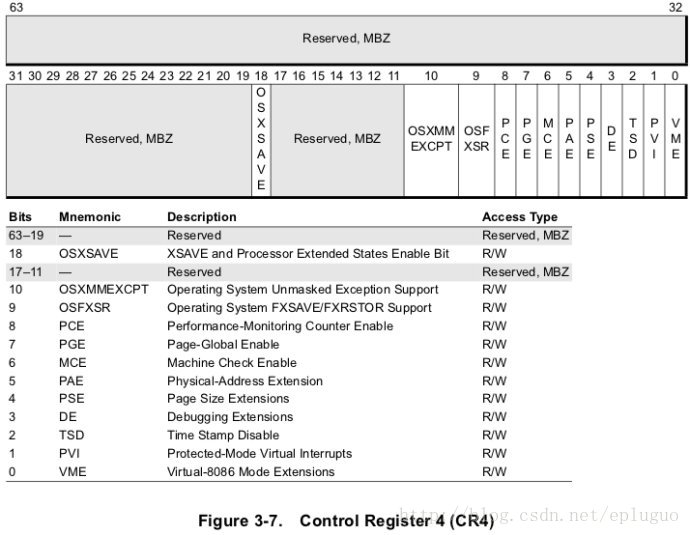

CR4

legacy mode(传统模式) 下低32位与x86_32的CR4一致