DesignWare Building Block

1. 基本介绍

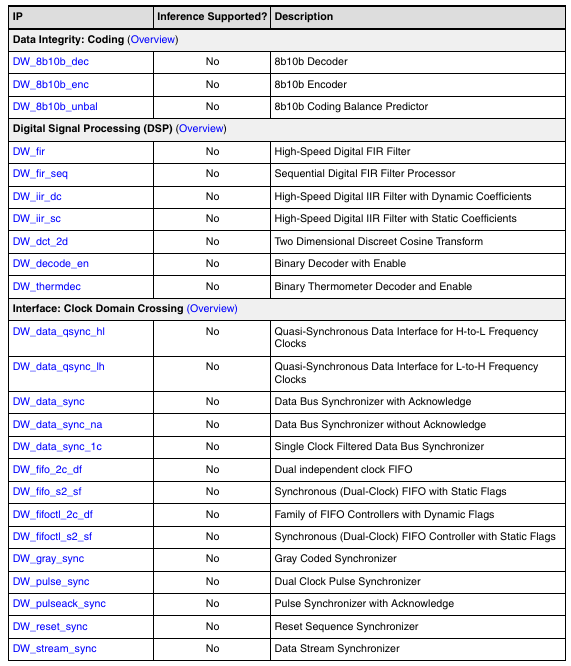

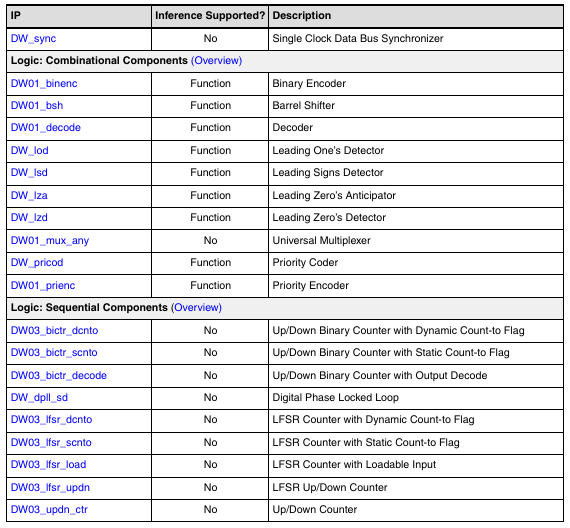

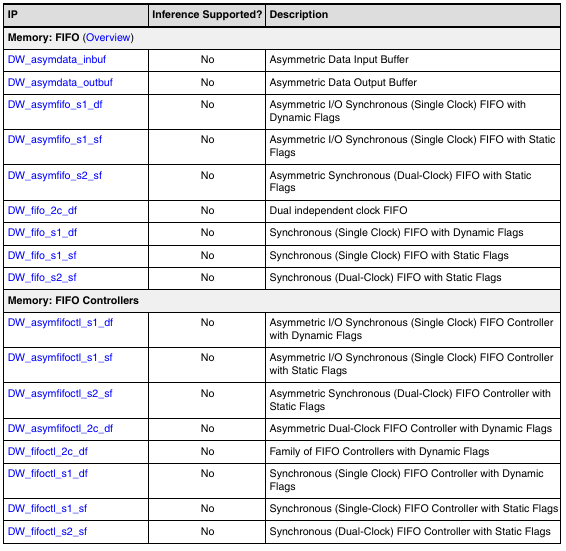

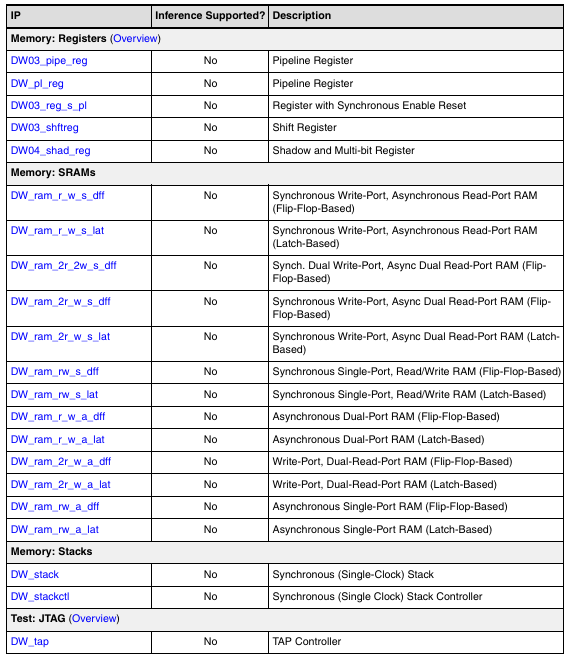

DesignWare Building Block IP (以下简称DWBB),也叫做Foundation Library,是一个紧密集成在Synopsys综合环境中的可重用智能功能块集合。使用DWBB可以在综合时实现透明且高水平的性能优化。DWBB中含有大量组件,可以实现设计重用并显著地提升生产力。该库中包含有基本库IP的高性能实现,以及许多更高级算数和时序功能块的实现。该库包含了:

- 基本库:与HDL编译器绑定的一组IP,实现了一些常用的算数和逻辑功能

- 逻辑:组合和时序IP

- 数学:算数和三角IP

- 数字信号处理:FIR和IIR滤波器

- 存储:寄存器,FIFO和FIFO控制器,同步和异步RAM,栈

- 接口:跨时钟域

- 专用:数据完整性,接口,JTAG IP等

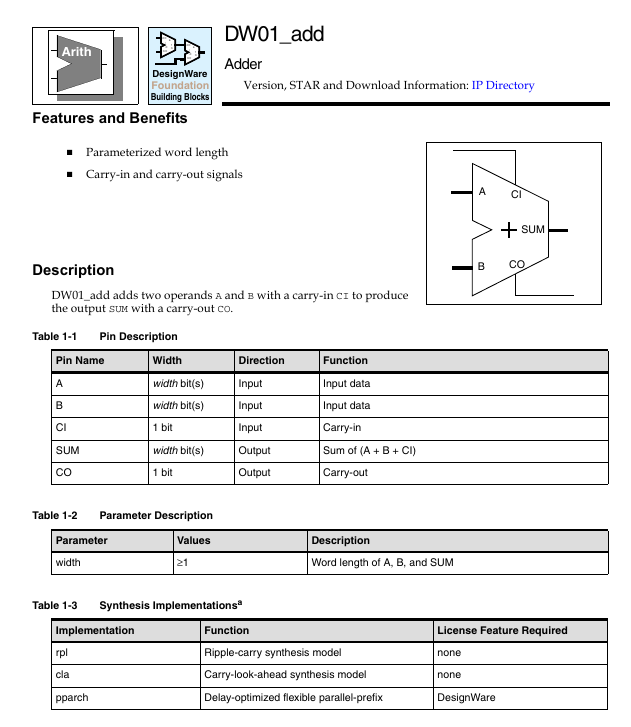

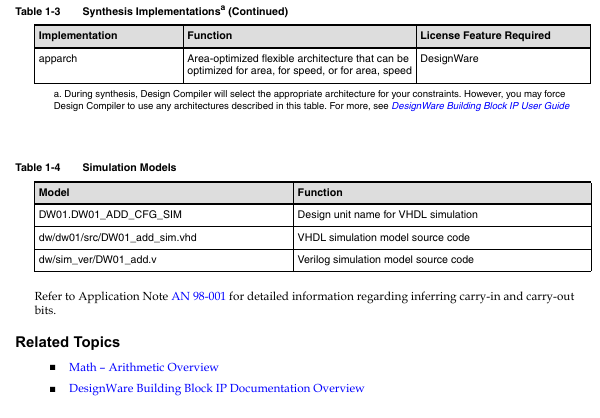

DWBB的详细内容见附件1 DWBB IP List。此外每个IP都有自己的详细文档,介绍了IP的功能,端口,参数,实现,仿真模型,使用例子等,例子见附件2 DW01_add Datasheet。

DWBB通过高度自动化的设计重用,使得Synopsys综合工具可以透明的执行各种高等级优化。

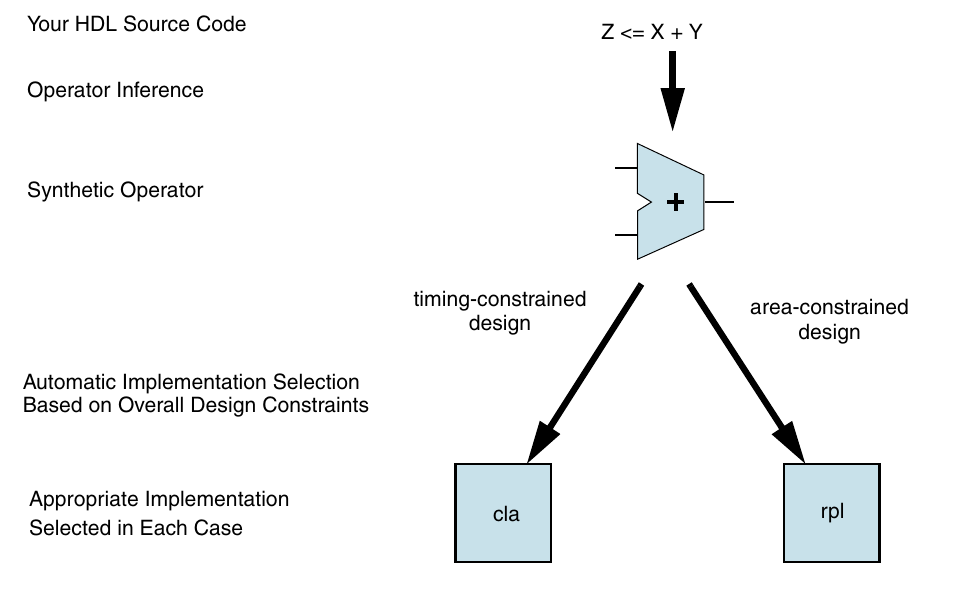

例如当你在设计中使用HDL加法符号“+”时,HDL编译器会推断出此处需要一个加法器资源,并在你的电路网表中插入一个代表加号的抽象表示。这个抽象表示被称为综合运算符,是通过高层次优化HDL编译器加入设计中的,这些优化包含了算数优化,资源复用和引脚排列。

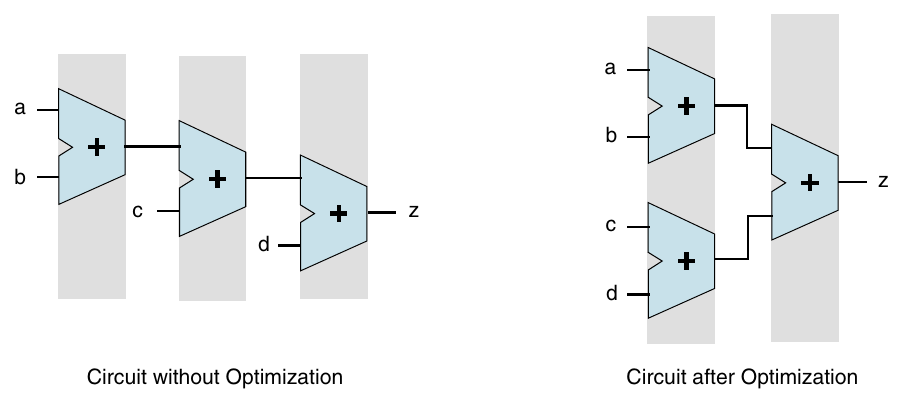

算数优化通过重新排列运算符的方式以代数法则来提升电路的面积和性能,例如,表达式a+b+c+d描述了三级串联的加法操作,算数优化可将这个表达式重新摆列成(a+b)+(c+d),从而使得只有两级串联加法,使得逻辑变得更快。

资源复用可以让在时间上不重叠的相似操作在同一个物理硬件上运行。引脚重排利用了一些操作(比如加法和乘法)不会受到交换输入端口的影响。

通过DWBB,一个给定的运算符可以通过多种硬件电路来进行实现,具体选择哪一种实现则由综合器来做决定。例如无符号加法可以通过行波进位加法器架构或者超前进位加法器架构来实现。你可以通过设置你对整体设计的优化约束,让综合工具来选择具体使用那种架构。

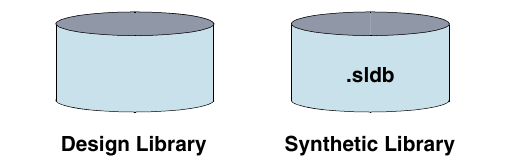

DWBB有两个部分,一个设计库和一个综合库。

-

设计库是一个包含了各种可参数化的IP架构的电路描述的UNIX文件夹

-

综合库是一个以.sldb为后缀名的二进制文件,用于将设计库中的电路链接到Synopsys综合工具

设计库中的电路描述以二进制格式存储在综合库中以便Synopsys工具的调用。这些电路和工艺依赖的电路以及硬宏单元不同,是参数化,可优化的全层次化设计。综合库中包含了可以让综合工具执行高层次优化的信息,包括实现的选择。

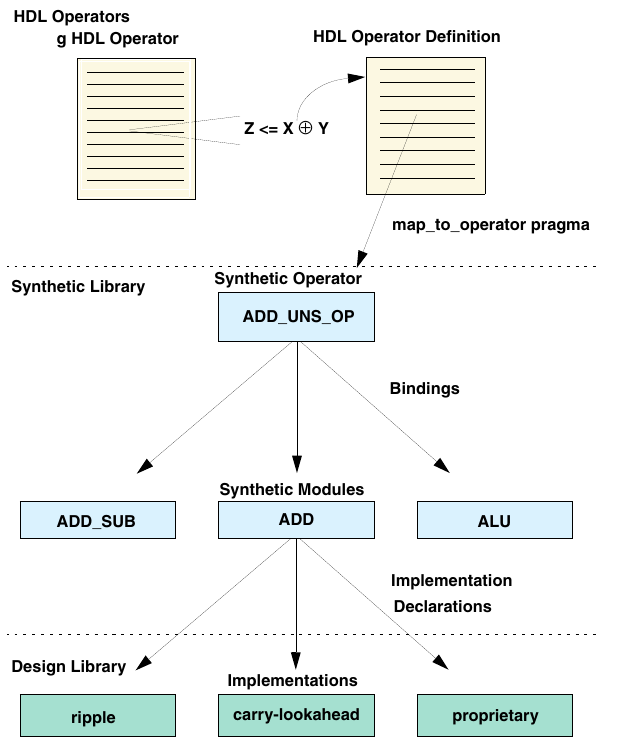

你的源代码,综合库和设计库通过一套抽象层级来建立连接。首先HDL的运算符与综合运算符相互关联,从而与综合模块相互绑定。每个综合模块又能够有数种被称为实现的具体架构方案。

另一类DWBB中的IP被称为子块,只有一种实现,并且只能例化调用。子块对于不具有多种实现的大的模块非常有用,比如错误检查与校验IP。从结果上来说,子块的层级抽象结构和下图的描述不同。

HDL运算符是HDL语言中那些处理输入值产生输出值的结构。有的运算符内嵌在语言之中,比如+,-和*。用户定义的子程序(比如函数和过程快)也被称为HDL运算符。

DWBB实现了许多内嵌的HDL运算符,包括+,-,*,<,>,<=,>=,/,还有其他通过if和case描述的操作。每个运算符都有一个用HDL书写的定义,每个定义都包含了运算符行为的可仿真规范,以及可选的map_to_operator编译只是,该编译指示将HDL运算符链接到等效的综合运算符。"/"运算符需要DWBB的证书。许多HDL操作符(包括了大部分内嵌操作符)默认映射到Synopsys标准综合库,standard.sldb中。

一个综合库包含了综合运算符的定义,综合模块和绑定关系。它还包含将综合模块与其实现相关联的声明。实现本身则保存在相应的设计库中。

- 综合运算符:表示HDL运算符调用的运算。综合工具会自动进行如算数优化或者资源共享一类的高层次优化

- 综合模块:为一系列实现定义通用结构,给定模块的所有实现都具有相同的端口和相同的输入输出行为

- 绑定关系:将综合运算符和综合模块相关联,例如绑定关系将用于加法的综合运算符和加法器模块相互关联(或者说加法综合运算符被绑定到了加法器模块),可以将多个综合运算符绑定到给定的综合模块上,也可以将一个运算符绑定多个模块。

设计库包含了具体的电路实现,用于执行你在设计中调用的DWBB中的IP的功能。在DWBB中,综合模块和实现的关系很紧密。实现可以被看成是综合模块的具体架构方案。实现既可以是用于特定工艺的网表,也可以是可综合的RTL级设计描述。

2. 基础使用

- 为了访问除了standard.sldb以外的综合库,你必须通过你的synthetic_library和link_library变量来调用这些库

- 要访问设计库(与 standard.sldb 关联的库除外),必须使用 dc_shell 命令 define_design_lib 或设计库文件 .synopsys_sim.setup 中的映射机制指定库目录的路径

- 要列出合成库中可用的运算符、模块和实现,请使用 report_synlib 命令

- 为了推断出DWBB中的IP,你需要:

- 在设计描述中包含适当的 HDL 运算符,

- 分析和阐述你的设计描述(使用analyze和elaborate命令),以及

- 设置约束并编译(compile命令)

- 为了例化一个综合模块,你需要:

- 在设计描述中包含对该模块的引用,

- 分析和阐述,以及

- 设置约束并编译

3. 进阶使用

-

你可以通过在 HDL 设计描述中包含指令,或者将设计读取到 dc_shell 中用 set_implementation 命令这两种方式来手动选择模块和实现

-

你可以使用 replace_synthetic 命令禁用综合运算符的高级优化

-

你可以使用 dont_use 命令禁用特定的综合模块及其实现

-

你可以使用 set_implementation_priority 命令在给定模块的实现中建立优先级

-

默认情况下,实现以层次结构进行例化。你可以使用 set_ungroup 命令取消层级例化

-

你可以使用 remove_unconnected_ports 命令从设计中的选定单元中删除未连接的端口.

-

你可以通过以下方式改进综合库缓存的使用:

- 共享缓存

- 用常用部件填充缓存

- 在探索多种不同的设计备选方案时,通过将 synlib_optimize_non_cache_elements 变量设置为 false 来提高编译速度

附件3中包含了DWBB的Quick Start文档的内容,大概说明了如何设置DWBB环境,如何调用DWBB,如何控制DWBB的综合以及如何对DWBB进行仿真。更细节的DWBB使用可以查看DWBB User Guide。

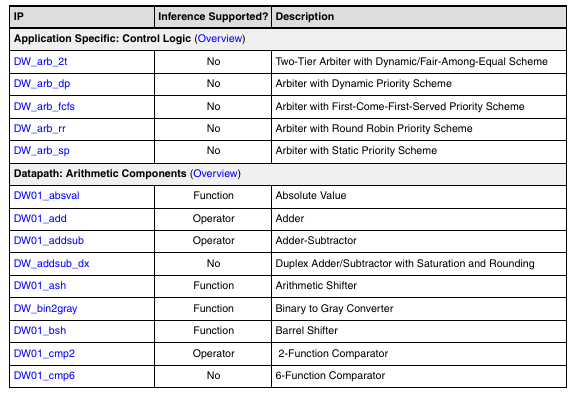

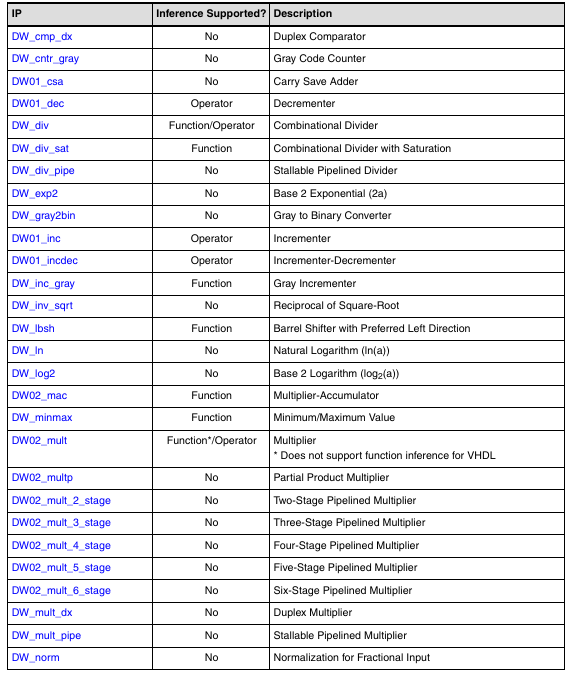

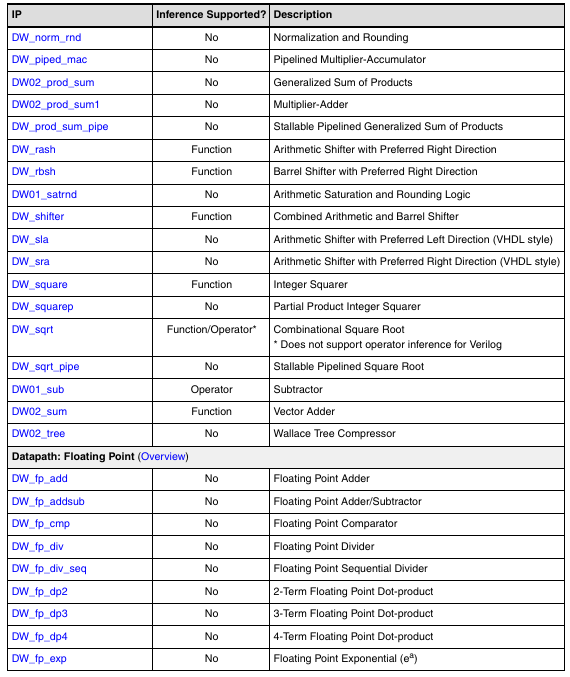

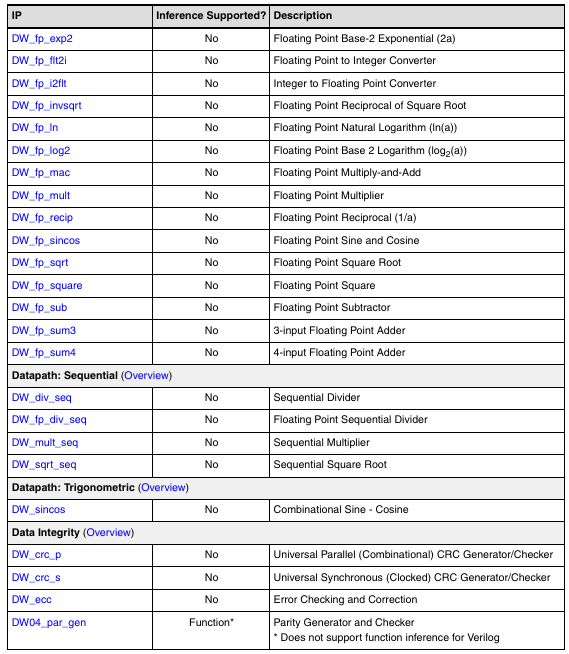

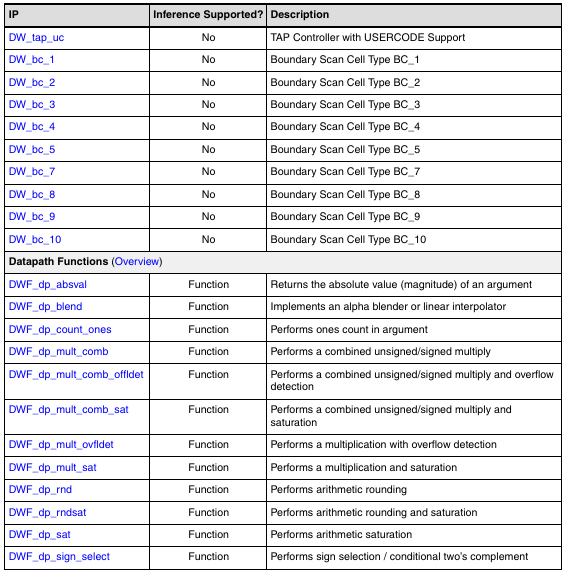

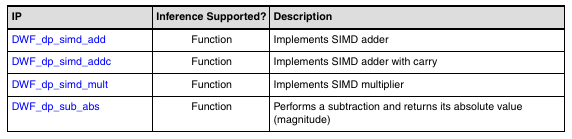

附件1. DWBB IP List

附件2. DW01_add Datasheet

附件3. DWBB Quick Start

Setting Up DesignWare Building Block IP

Include the following lines in your .synopsys_dc.setup file and ensure that you have a valid DesignWare license.

set synthetic_library [list dw_foundation.sldb]

set link_library [concat $target_library $synthetic_library]

set search_path [concat $search_path [list \

[format “%s%s” $synopsys_root “/dw/sim_ver”]]]

set synlib_wait_for_design_license [list “DesignWare”]

Accessing DesignWare Building Block IP

You can access Building Block IP either by operator or functional inference, in some cases, or by instantiating the component directly. The example below shows how to access IP.

assign PROD = IN1 * IN2; // Operator Inference

assign PROD = mult_tc(IN1, IN2); // Function Inference

DW01_mult #(8, 8) U1 (A, B, TC, PRODUCT); // Instantiation

Details about inference and instantiation in VHDL and Verilog are in the following directory: $SYNOPSYS/dw/examples.

Synthesizing DesignWare Building Block IP

Design Compiler automatically selects the best implementation for combinational DesignWare Building Block IP. You can also force Design Compiler to select the implementation of your choice either by adding Synopsys Compiler directives or by using the following commands:

dc_shell-t> set_dont_use standard.sldb/DW01_add/rpl

dc_shell-t> set_implementation clf [list add_68]

Simulating DesignWare Building Block IP

Synopsys VCS MX simulator uses the default setup file while simulating DesignWare Building Block IP. Use the following options to simulate IP with a Verilog simulator:

-y $SYNOPSYS/dw/sim_ver +libext+.v+