1.算法仿真效果

其中Vivado2019.2仿真结果如下:

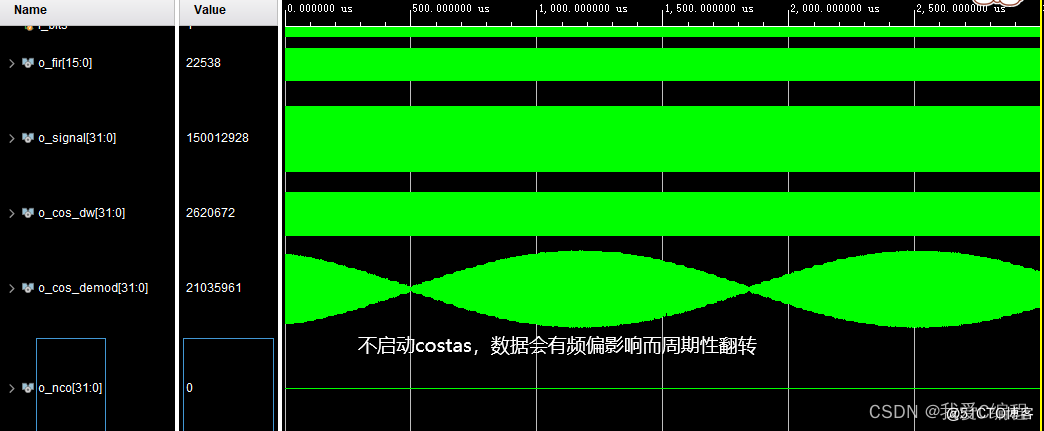

没有costas环,频偏对基带数据的影响

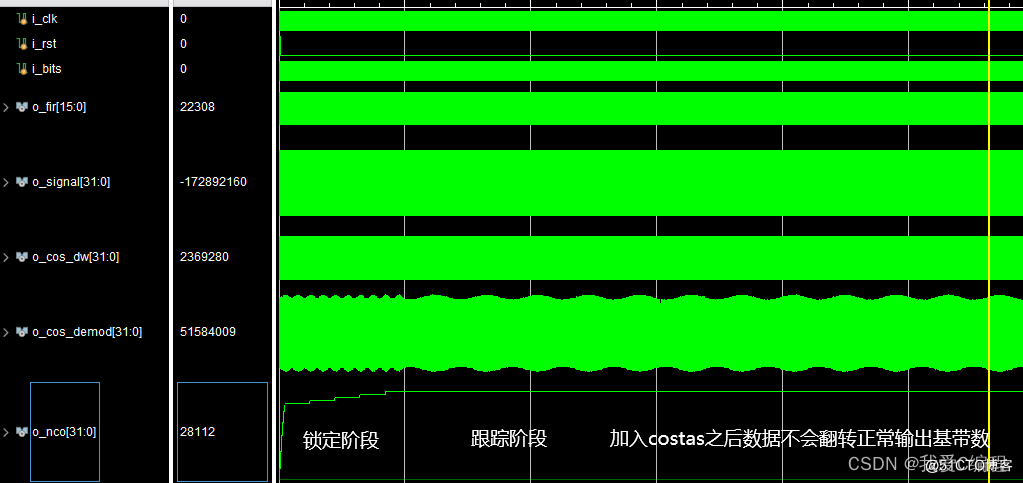

加入costas环的基带数据

2.算法涉及理论知识概要

Costas环是一种用于载波同步的常见方法,特别是在调制解调中,它被广泛用于解调相位调制信号,如二进制调相(BPSK)或四进制调相(QPSK)信号。它的目的是估计和追踪接收信号的相位偏移,以便正确解调数据。

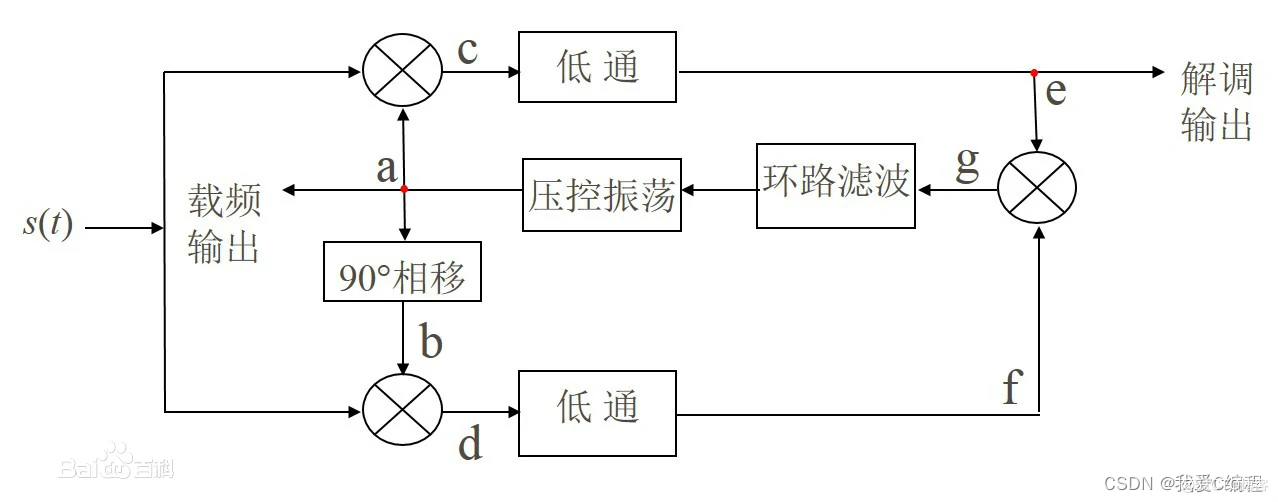

其基本结构如下图所示:

Costas环结构:

如上图所示Costas环包括两个主要部分:一个偏移90度的本地振荡器(Local Oscillator,LO)和一个相移解调器。这两个部分协同工作来估计信号的相位偏移。

Costas环包括以下主要组件:

本地振荡器(Local Oscillator,LO): LO产生一个本地参考信号,其频率与接收信号的载波频率相同。这个本地参考信号通常包括正弦和余弦两路信号,相位相差90度。这两路信号将与接收信号相位进行比较。

相位解调器(Phase Detector): 相位解调器用于测量接收信号和本地振荡器之间的相位差。它的输出是一个带有相位信息的信号。

环路滤波器(Loop Filter): 环路滤波器对相位差信息进行滤波和处理,以生成一个控制电压。这个电压将用于调整本地振荡器的频率和相位,以最小化相位差。

本地振荡器控制单元: 这个单元接收来自环路滤波器的控制电压,并相应地调整本地振荡器的频率和相位。

输出: Costas环的输出是本地振荡器的相位信息,该信息已经被调整,以与接收信号的相位保持同步。这个输出可以用于解调接收信号。

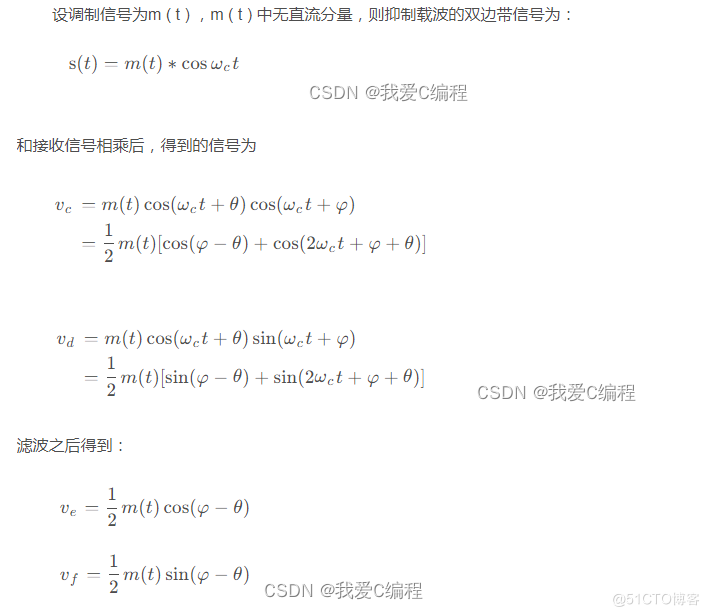

Costas环原理:

Costas环的原理是利用接收信号和LO之间的相位差异来估计信号的相位偏移。当信号的相位偏移接近0或180度时,乘积信号的幅值最大,而当相位偏移接近90或270度时,乘积信号的幅值最小。因此,通过测量乘积信号的幅值,可以估计相位偏移。

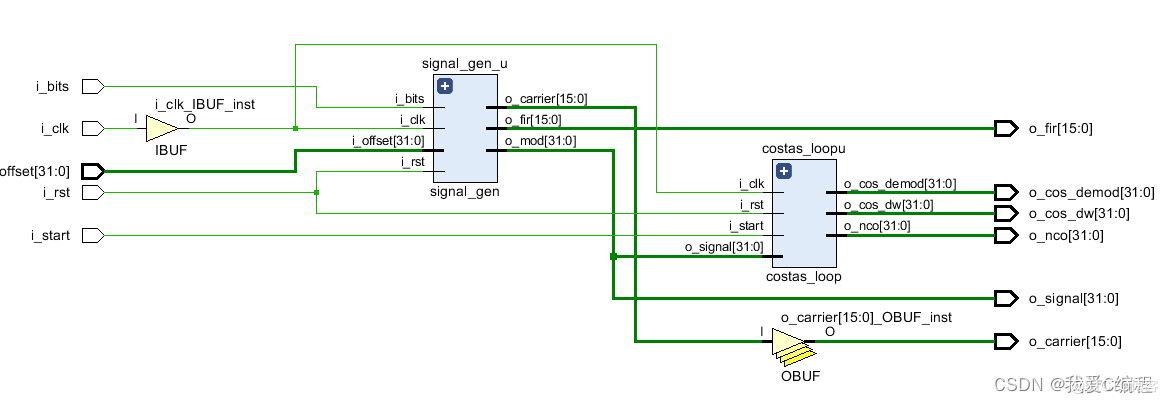

3.Verilog核心程序

`timescale 1ns / 1ps

module costas_tops(

input i_clk,

input i_rst,

input i_bits,

input i_start,

input signed[31:0]i_offset,

output signed[15:0]o_fir,

output signed[15:0]o_carrier,

output signed[31:0]o_signal,

output signed[31:0]o_cos_dw,

output signed[31:0]o_cos_demod,

output signed[31:0]o_nco

);

//调制端

signal_gen signal_gen_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_bits (i_bits),

.i_offset (i_offset),

.o_fir (o_fir),

.o_carrier(o_carrier),

.o_mod (o_signal)

);

/

//解调端 ,考虑载波costas同步

costas_loop costas_loopu(

.i_clk (i_clk),

.i_rst (i_rst),

.i_start (i_start),

.o_signal (o_signal),

.o_cos_dw (o_cos_dw),

.o_cos_demod (o_cos_demod),

.o_nco (o_nco)

);

endmodule