C语言全局变量的extern

全局变量在不同的文件引用,需要加上extern,才能引用到。

如果没有extern关键词,则认为是一个定义,而不是引用,引发同名冲突。

函数也是一样。要在本文件引用其它文件的函数,需要增补extern关键字。

而其它文件,声明和定义过该函数。

typedef函数指针

https://zhuanlan.zhihu.com/p/380264864

typedef char (*p)(int);

p pFun;

char glFun(int a){ return;}

void main()

{

pFun = glFun;

(*pFun)(2);

}

uvm_queue/pool/config_db/resource_db/barrier

主要是看源码实现

uvm_queue

https://developer.aliyun.com/article/1070032

uvm_queue实现了基于类的动态队列,在sv 队列基础上,主要新加了以下方法:

● get_global_queue(),获取全局队列,没有全局队列的话,新建全局队列;

● get_global(int index),获取全局队列并返回第index个元素;

● covert2string(),队列转换为字符串

这个class将sv的queue封装,并引入了单例模式,用于全局共享的一个queue。实例化的时候最好带着参数。

uvm_pool

https://developer.aliyun.com/article/1070423

uvm_queue实现了基于类的动态队列,在sv 队列基础上,主要新加了以下方法:

动态关联数组的封装。和uvm_queue一样,存在单例模式。

uvm_config_db与uvm_resource_db的区别

https://blog.csdn.net/qq_40571921/article/details/121885916

uvm_resource_db虽然也是一种用来共享数据的类,但是层次关系在该类中没有作用; 与uvm_config_db相比,尽管uvm_resource_db也有内建的数据库,可以通过字符串或类型来索引配置数据,但缺点是层次的缺失和因此带来的自顶向下的配置覆盖关系的缺失.

uvm_barrier

https://developer.aliyun.com/article/1070540

uvm_barrier直接扩展自uvm_object,提供多进程间的同步机制。简单讲就是用户设置一个阈值,每个等待同步的进程在执行完之后进入wait_for等待事假触发,当进入wait_for的进程数达到阈值时触发该事件,所有等待同步的进程跳出wait_for继续执行,从而实现多个进程的同步。

接口设计分层

对于一个低速接口的模块设计。内部划分为三层,并被顶层的top包裹。和PCIe内部的事务层、链路层、物理层的设计思想一样,一个低速模块内部的三层为:

● 寄存器层,主要存储寄存器的数据值;

● 事务层,主要构建事务所需要的信息;

● 接口层,主要实现数据的送出过程。

寄存器层和接口层存在和外部交互的接口。寄存器层主要是标准的AMBA低速总线,中断也从该层引出;接口层主要是标准的低速接口如II2、SPI、UART等。

PCIe电气接口

https://zhuanlan.zhihu.com/p/150636536

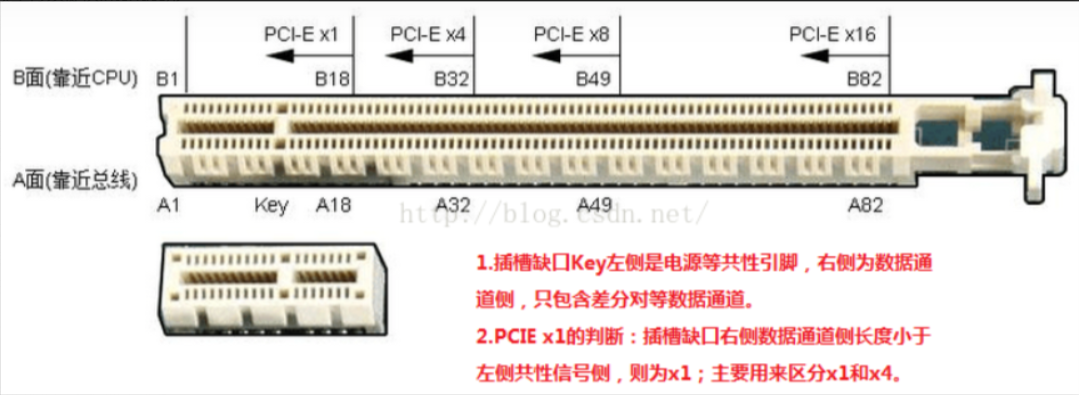

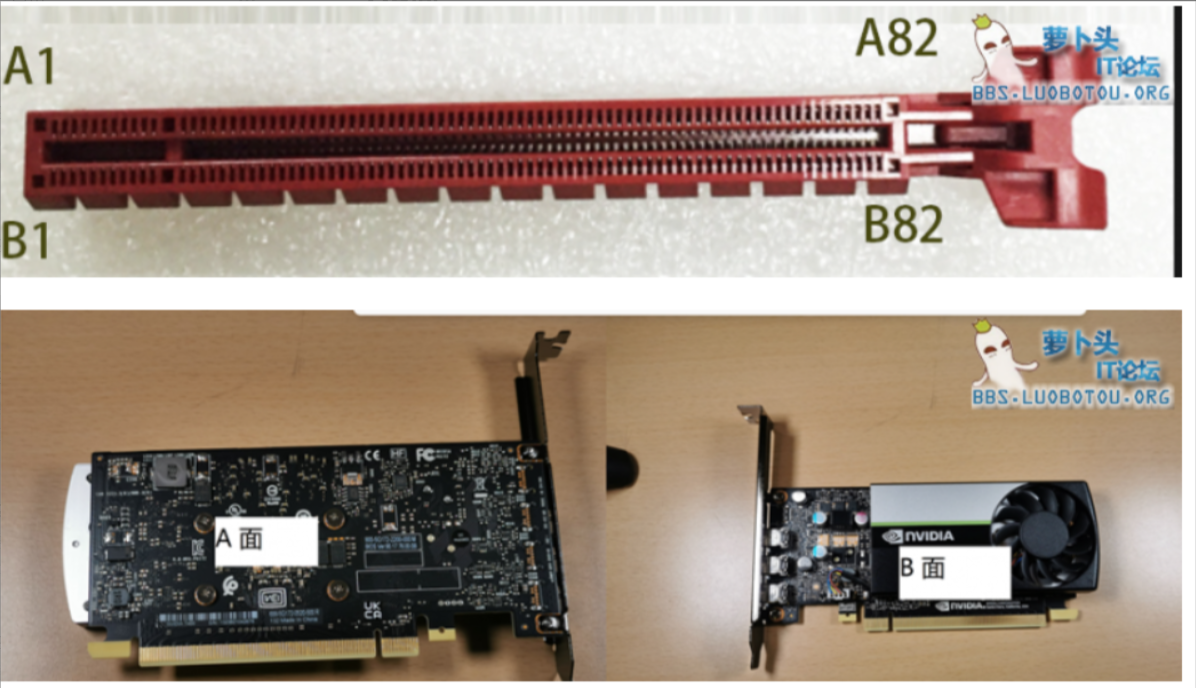

AB面

PCIe引脚有两面,A面B面,两面引脚定义不同。

在主板上,A端靠近CPU。

在显卡等PCIe卡上,有核心和散热器的是B面,背面是A面。(所以插入机箱里的显卡,都是风扇向下的,因为风扇那个是B面,靠近总线)

https://bbs.luobotou.org/thread-51974-1-1.html

JTAG和SMBus

JTAG接口通常会运行的时钟频率为10MHz到30MHz

SMBus规定时钟频率必须在10k~100k内。

所以A面一般接入速率更高的JTAG,B面接入速率不高的SMBus。

JTAG接口的控制器在PCIe的Phy里的pcs_raw的cmn模块中。

JTAG简介

https://liangkangnan.gitee.io/2020/03/21/深入浅出RISC-V调试/

标准JTAG采用四线方式,分别是TCK、TMS、TDI和TDO,有一个可选的TRST引脚。TCK:测试时钟输入。TMS:测试模式选择。TDI:测试数据输入。TDO:测试数据输出。

一个JTAG主机可以同时对多个JTAG从机进行调试,这通过JTAG扫描链(JTAG Scan Chain)完成。

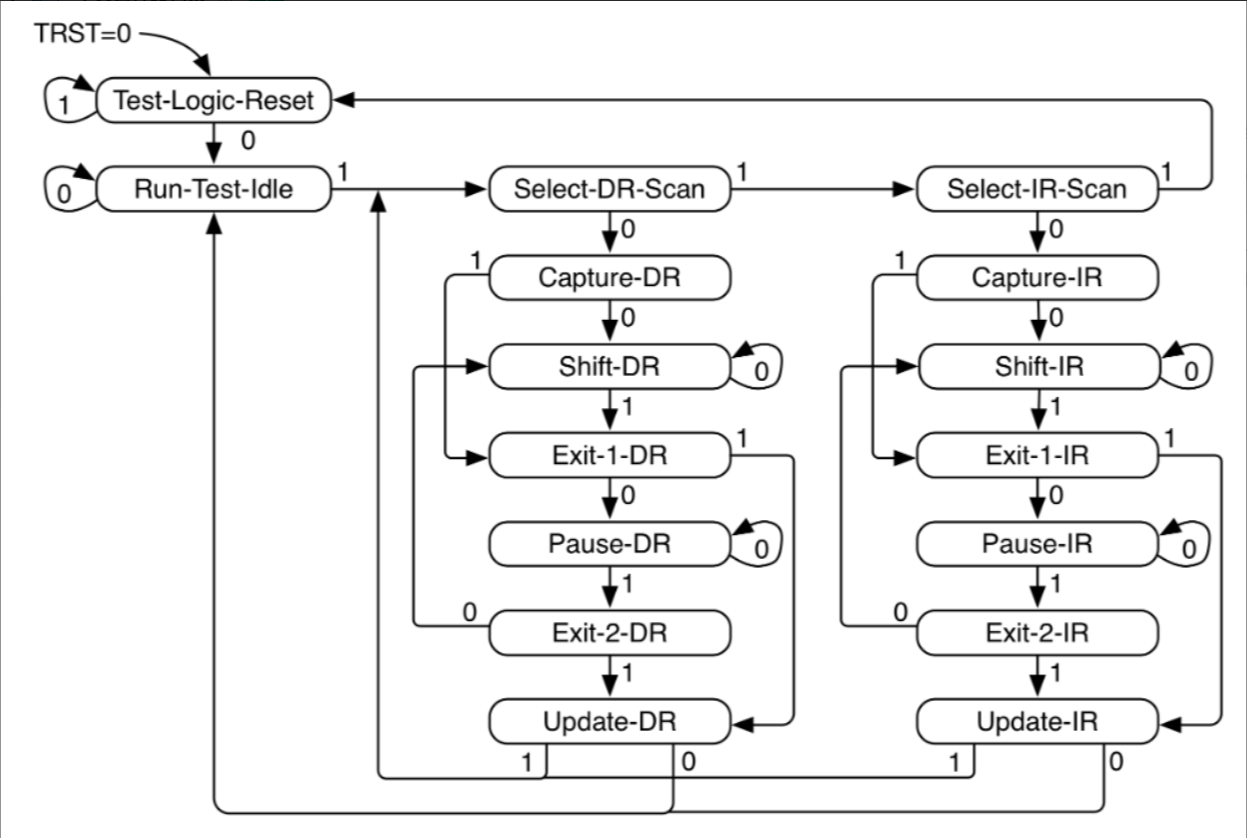

JTAG(slave)内部有一个TAP(Test Access Port)控制器(或者说状态机),通过TCK和TMS信号来改变状态机的状态。这个状态机的核心是两路SCAN,分别是IR SCAN和DR SCAN。箭头上的0或1表示的是TMS信号的电平。JTAG在每一个TCK信号的上升沿采样TMS信号和TDI信号,决定状态机的状态是否发生变化,在每一个TCK信号的下降沿输出TDO信号。可以看到,无论TAP目前处于哪一个状态,只要TMS保持高电平并持续5个TCK时钟,则TAP一定会回到Test-Logic-Reset状态。JTAG内部有一个IR ( instruction register )寄存器和多个DR(data register)寄存器,IR寄存器决定要访问的是哪一个DR寄存器。DR寄存器有IDCODE、BYPASS等。在Test-Logic-Reset状态下IR寄存器默认选择的是IDCODE这个DR寄存器。 JTAG主机通过IR SCAN设置IR寄存器的值,然后通过DR SCAN来读、写相应的DR寄存器。

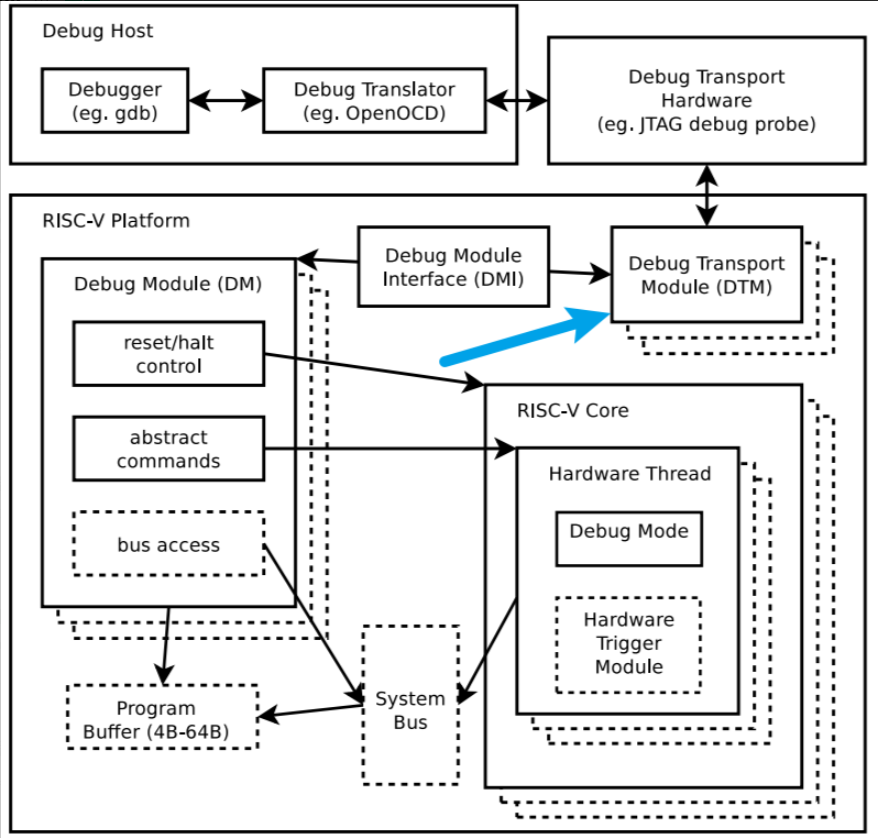

riscv的调试使用jtag:

Debug Transport Hardware,可以理解为JLink或者CMSIS-DAP这样的调试工具;

Debug Transport Module模块,位于RISCV的soc中,通过DMI接口与DM模块交互。DTM模块里实现了一个TAP控制器(状态机)。DTM模块中存在控制、状态、访问等寄存器,操作这些寄存器实现功能调试。

SMBus

系统管理汇流排(System Management Bus, 缩写为SMBus)是一种源自于I2C的汇流排,其设计应用于轻量级的通讯,常见于电脑的电源管理系统(例如笔记型电脑的智能电池子系统),一些装置(如温度、电压、电流或风扇传感器)也通过SMBus报告系统管理资讯。

https://blog.csdn.net/qq_51447215/article/details/127474324

https://zh.wikipedia.org/wiki/系統管理匯流排

和I2C的区别:

● VDD 的极限值不一样。I2C 协议的范围很广,甚至讨论了高达 12V 的情况,而SMBus规定了在1.8V~5V。

● 时钟频率规定不同。I2C 没有时钟频率限制,一般最常见的是100k、400k,而SMBus规定时钟频率必须在10k~100k内。

● 当设备需要处理内部事情时,可将时钟线拉低,I2C 没有规定拉低时长,而SMBus有规定时限。

● 地址应答规定不同。一个 设备接收到它的设备地址后,I2C 协议没有强制要求必须发出回应信号,而SMBus:强制要求必须发出回应信号。

● 数据格式规定不同。I2C 没有定义数据的格式,格式由设备来定义,而SMBus 协议明确了数据的传输格式。

● SMBus 有低功耗的版本

SMBus 和 I2C 的使用建议:

因为很多设备都实现了 SMBus,而不是更宽泛的 I2C 协议,所以优先使用SMBus。即使 I2C 控制器没有实现 SMBus,软件方面也是可以使用 I2C 协议来模拟 SMBus。所以:Linux 建议优先使用 SMBus。

Vcc和Vaux

https://open.tech2real.com/info_detail_page?id=15698#index

PCIe电源有+12V、+3.3Vcc 和+3.3Vaux。其中+12V主要给PCIe设备(如显卡)提供更大的供电能力(PCIe3.0的插槽最大有150w)

PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。其中Vcc为主电源,PCIe设备使用的主要逻辑模块均使用Vcc供电,而一些与电源管理相关的逻辑使用Vaux供电。在PCIe设备中,一些特殊的寄存器通常使用Vaux供电,如Sticky Register,此时即使PCIe设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。

在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间。因为Vaux在多数情况下并不会被移除,因此当PCIe设备的Vcc恢复后,该设备不用重新恢复使用Vaux供电的逻辑,从而设备可以很快地恢复到正常工作状状态。

WEAK和PRSNT

● WAKE#

当PCIe设备进入休眠状态,主电源已经停止供电时,PCIe设备使用该信号向处理器系统提供唤醒请求,使处理器系统为该PCIe设备提供主电源Vcc。

● PERST#(#:低电平有效)

该信号为全局复位信号,由处理器系统提供,处理器系统需要为PCIe插槽和PCIe设备提供该信号,PCIe设备使用该信号复位内部逻辑,当该信号有效时,PCIe设备将对内部逻辑进行复位操作,其中Cold Reset和Warm Reset这两种复位方式与该信号有关。PRSNT1# 和PRSNT2# 引脚必须比其馀稍短,以确保热插入卡完全插入。