一、问题描述

在一个工程中,分别对应[1:0] F4_clk_cnt_pos和[1:0] F4_clk_cnt_neg计数,且计数正常,我使用if语句判断当F4_clk_cnt_pos == 2'b01&&F4_clk_cnt_neg = = 2'b11,从而进行Sample_clk时钟的反转。具体代码如下:

always @(posedge clk or negedge n_rst)

begin

if(n_rst==1'b0)

Sample_clk <=1'b0;

else if((F4_clk_cnt_neg==2'b11)&&(F4_clk_cnt_pos==2'b01))

Sample_clk <=~Sample_clk;

else

Sample_clk <=Sample_clk;

end

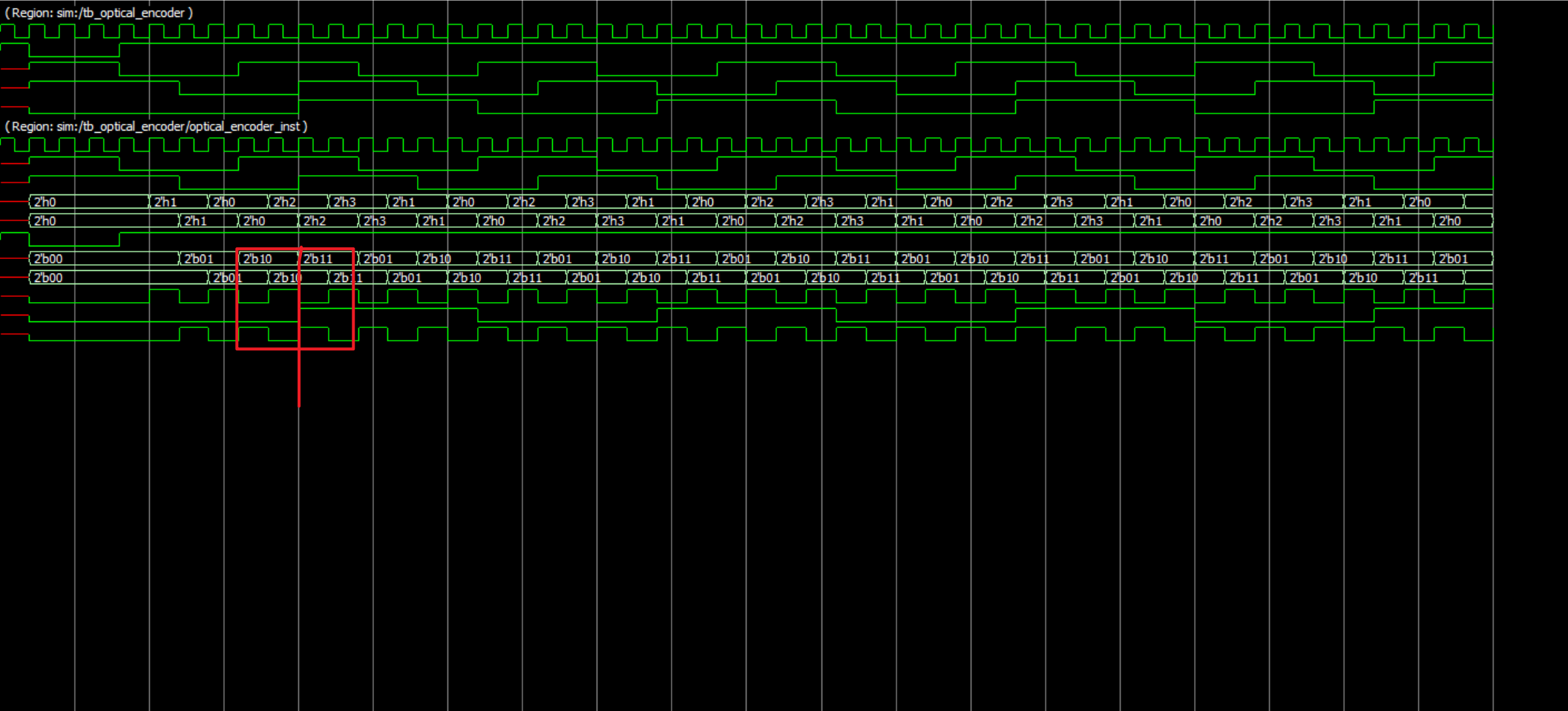

仿真结果如下:

显然存在F4_clk_cnt_pos == 2'b01 F4_clk_cnt_neg == 2'b11的情况,但是Sample_clk未有电平的反转!!!

接着我换了一下判断的值,满足F4_clk_cnt_pos == 2'b10&& F4_clk_cnt_neg == 2'b10进行电平反转,具体代码如下:

always @(posedge clk or negedge n_rst)

begin

if(n_rst==1'b0)

Sample_clk <=1'b0;

else if((F4_clk_cnt_neg==2'b10)&&(F4_clk_cnt_pos==2'b10))

Sample_clk <=~Sample_clk;

else

Sample_clk <=Sample_clk;

end

仿真情况如下:

此时仿真正常,我不理解到底是什么原因导致if判断失效,望大佬指点!!

二、偶然仿真正确

起初我使用的modelsim Altera10.1版本进行仿真,后面因为电脑也安装了modelsimSE-64 10.5,联合进行仿真后发现没问题了,我想可能是太老的modelsim版本还有有点bug吧,但是重新打开运行任然会出现上述问题,不知所以。。。。。?。

三、最终原因

在if语句中的判断不能复杂,不然会出现判断错误的情况,所以我们以后对于稍微复杂的判断条件最好先进行计算赋值,然后再if判断?。代码如下:

wire judge=(F4_clk_cnt_neg==2'b11)&&(F4_clk_cnt_pos==2'b01);

always @(posedge clk or negedge n_rst)

begin

if(n_rst==1'b0)

Sample_clk <=1'b0;

else if(judge)

Sample_clk <=~Sample_clk;

else

Sample_clk <=Sample_clk;

end