2.4.2 全差分折叠Cascode放大器

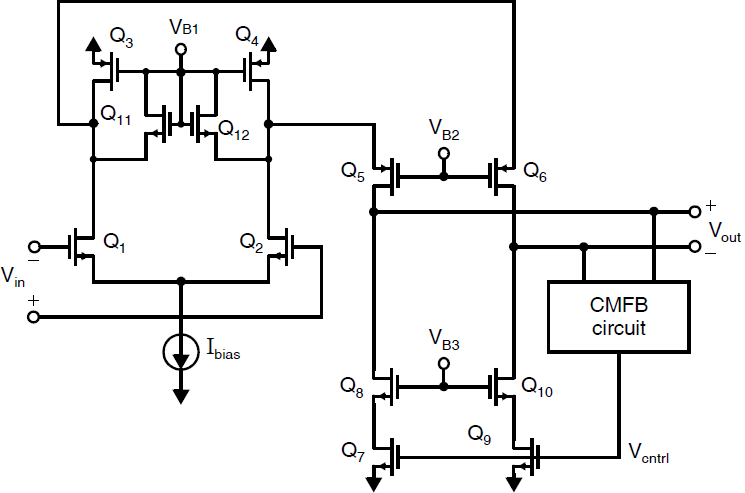

下图展示了一个简化的全差分折叠Cascode放大器。使用两个Cascode电流源来取代之前介绍的结构中的n沟道电流镜,并增加了一个共模反馈电路。这些电流源的驱动晶体管的栅压由共模反馈电路的输出电压\(V_{cntrl}\)决定。共模反馈电路的输入是全差分放大器的两路输出。共模反馈电路会检测这两个输出的平均值,并强制使其等于一个预先确定的值。

注意当放大器输出在变化时,负斜率下的最大的可用电流由\(Q_7\)或\(Q_9\)的偏置电流来决定。如果共模反馈电路够快,那么这个最大可用值将会在摆率期间动态的增加到某个程度,但仍然很难达到单端输出放大器的程度。因此,全差分折叠Cascode放大器一般将输出级的偏置电流设计的与输入晶体管偏置电流相等。同时,为了最小化摆率限制期间的瞬态电压变化,加入了钳位晶体管\(Q_{11}\)和\(Q_{12}\),这与之前的单端输出设计是一致的。如果没有这些晶体管的话,那么折叠Cascode放大器从摆率限制中恢复所需要的时间就会非常久。

现在每条信号路径除了输出节点就只有一个节点,即输入器件的漏极。这些节点自然会主要形成等效第二极点。在负载电容很小的情况,并且增大带宽很重要的情况下,使用一个互补设计(即n沟道和p沟道以及电源供电互换)可以更好的扩大等效第二极点。互补电路会使得输入器件的漏极阻抗为n沟道晶体管的跨导的倒数,而非p沟道晶体管,使得阻抗更小,从而有更快的时间常数。这里的设计代价是放大器的跨导,也即最后放大器的增益,会由于输入晶体管变成了p管而减小。同时,共模反馈电路也会变得更慢,因为电流源也必须变成p沟道驱动晶体管。在一些情况下,使用补偿设计对于高速全差分设计来说是一个合理的选择。