在Verilog中,default_nettype none语句用于禁止隐式声明信号类型,这样可以增强代码的可读性和可维护性。Verilog语言允许在使用信号之前不显式声明信号类型,而是根据信号名的前缀来推断信号的类型(比如wire或reg)。

然而,这种隐式声明的方式可能会导致一些问题,特别是在大型项目或多人协作的情况下。如果信号的类型不是显式指定的,那么代码的阅读者可能需要查看整个代码来确定信号是wire还是reg。这可能导致误解和错误,特别是在复杂的设计中。

通过添加default_nettype none语句,禁止了Verilog的默认行为,要求在使用信号之前显式声明信号类型。这可以帮助提高代码的清晰度,减少可能的错误,并使代码更容易理解和维护。在代码的开头添加这样的语句是一种良好的实践,特别是在大型项目中

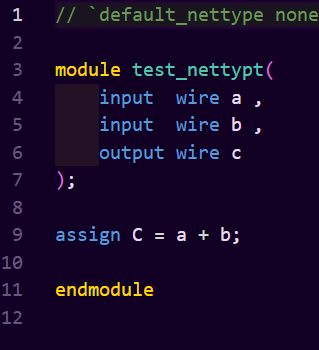

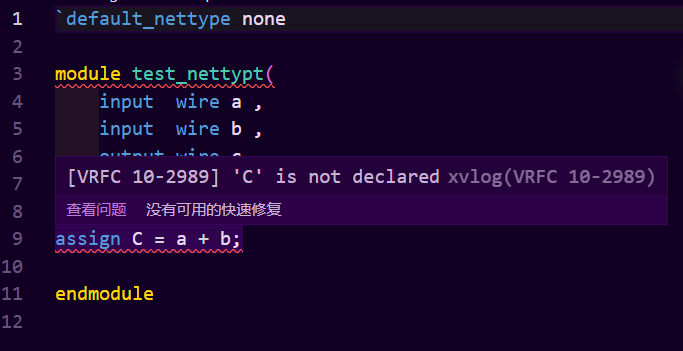

类似以下代码,很明显大写C是笔误,如果不加`default_nettype none是不会报错的

`default_nettype none

module test_nettypt(

input wire a ,

input wire b ,

output wire c

);

assign C = a + b;

endmodule