设计块:

module Detector2 ( input CP,Sin,nCR, output reg Out ); reg [1:0] Current_state,Next_state; parameter S0=2'b00, S1=2'b01, S2=2'b10, S3=2'b11; always @(posedge CP , negedge nCR) begin if(~nCR) begin Current_state = S0; Next_state = S0; end else Current_state = Next_state; end always @(Current_state, Sin) begin Next_state=2'bxx; Out=1'b 0; case(Current_state) S0: begin Out=1'b0; Next_state=(Sin==1)? S0 : S1; end S1: begin Out=1'b0; Next_state=(Sin==1)? S2 : S1; end S2: begin Out=1'b0; Next_state=(Sin==1)? S0 : S3; end S3: if (Sin==1) begin Out=1'b1; Next_state=S0; end else begin Out =1'b0; Next_state=S1; end endcase end endmodule

测试块:

`timescale 1ms / 1ms module Detector2test(); reg CP,Sin,nCR; wire Out ; // 实例化被测试模块 Detector2 test ( .Sin(Sin), .CP(CP), .nCR(nCR), .Out(Out) ); initial begin //Current_state=2'b00; // Next_state=2'b00; nCR=1'b0; CP=1'b0; #100 nCR = 1'b1; Sin=1'b0; #10Sin=1'b1; #10Sin=1'b0; #10Sin=1'b1; #10Sin=1'b0; #10Sin=1'b1; #10Sin=1'b0; #10Sin=1'b1; #10Sin=1'b0; #10Sin=1'b1; #10Sin=1'b0; #10Sin=1'b1; #10Sin=1'b0; end always #5 CP = ~CP; //always #10 Sin =~ Sin; endmodule

使用书上的源代码,报错,分析,发现循环语句中发现为见过的语句。推测打印错误,开始以为是编码问题,使用vs code 打开后取出非法字符

编译还是出现错误,教材未对always @(pose<e CP, nege<e nCR)

begin修改代码做出解释,所以应该是和第一种编写方式一样才对。

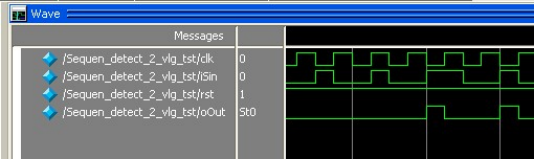

修改后,编译通过。