a)

发射频率2G~4.5GHz,瞬时带宽50M

b)

镜像抑制:45dBc

1.2指标分析

本文主要是分析AD9361的镜像和本振泄露性能指标,其他指标暂不赘述。

1.2.1何为本振泄露

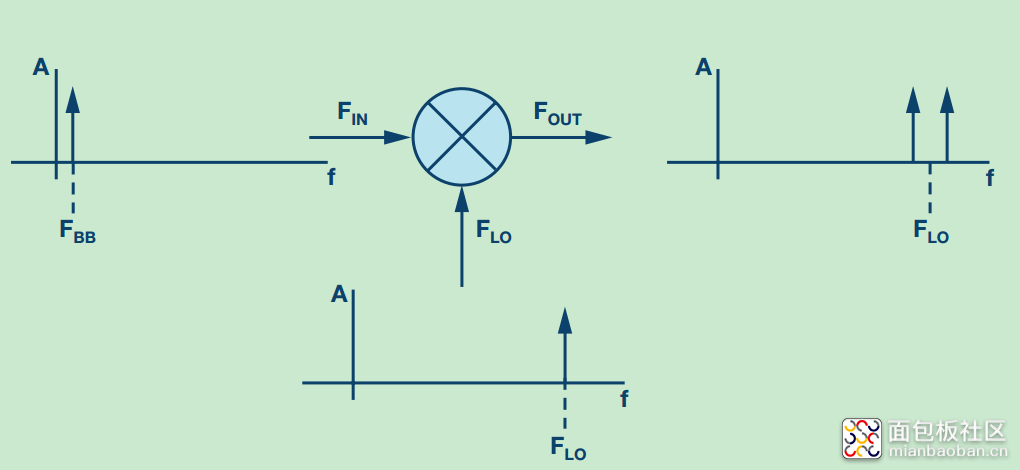

RF混频器有两个输入端口和一个输出端口,如图1所示。理想混频器将产生一个输出,它是两个输入的乘积。就频率而言,该输出的频率应当是FIN + FLO以及FIN – FLO,不含其它项。如果任一输入不在驱动状态下,则不会有输出。

图1.理想混频器

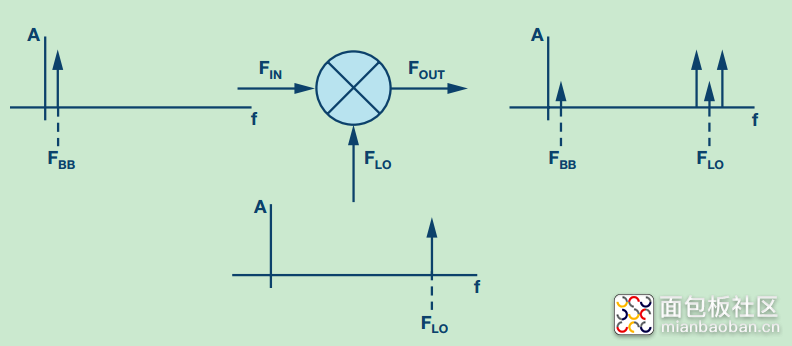

FIN被设置为基带频率为1 MHz的FBB, FLO被设置为本振频率为500 MHz的FLO。如果是理想混频器,它将产生一个输出,其中包含两个信号音,频率分别为499 MHz和501 MHz。在图1中,FIN被设置为基带频率为1 MHz的FBB,FLO被设置为本振频率为500 MHz的F LO。如果是理想混频器,它将产生一个输出其中包含两个信号音,频率分别为499 MHz和501 MHz。然而,如图2所示,在F BB和F LO,真实混频器还将产生一些能量。FBB处产生的能量可以忽略不计,因为它远离所需的输出,并且将被混频器输出之后的RF组件滤除。无论FBB处产生的能量如何, FLO下产生的能量都可能是一个问题。它非常接近或在所需的输出信号内,并且很难或无法通过滤波去除,因为滤波也会滤除所需的信号。LO应该用小一号或两号的产生的这种无用能量被称为LOL。可驱动混频器的本振 (LO) 已经泄漏到混频器的输出端口。LO还有其他途径可以泄漏到系统输出端,例如通过 电源 或跨越硅本身。无论本振如何泄漏,其泄漏都可被称为LOL。

图2.真实混频器

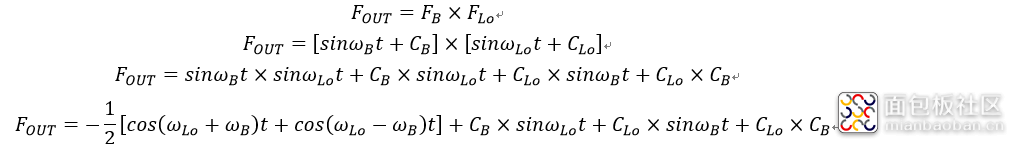

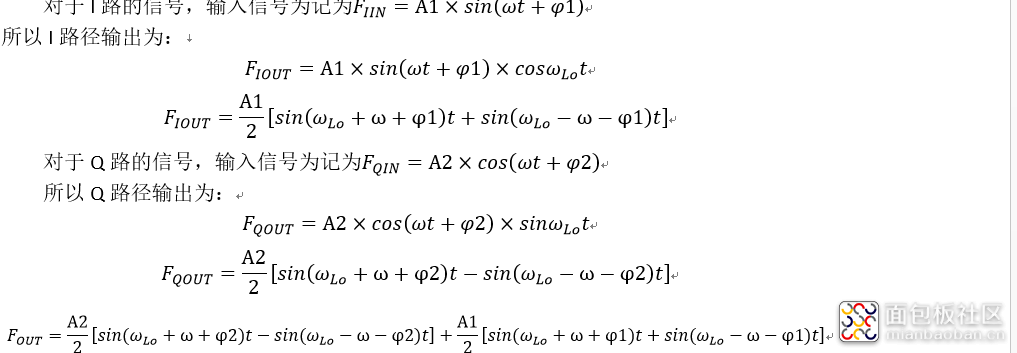

对于混频的过程,可以理解为两个信号在时域上乘积频域上的卷积,输入信号我们记为 本振信号我们记为

本振信号我们记为 两者乘积计算为:

两者乘积计算为:

从数学的表达式中可以看出,在输入信号和本振信号为理想信号时,对于输出信号Fout只有FIN + FLO以及FIN – FLO两个信号,但是实际应用中这些信号都是非理想的,比如输入和本振信号上有直流的偏差,即记为Cb和Clo,这些在信号在频谱上的贡献,如数学表达式所示,会产生一个输入信号的泄露、本振信号的泄露和一个零频的泄露。所以LO泄露信号路径上表达为直流的偏移,在对于复数混频构架为I或Q信号路径中表现为增大的直流失调。其原因是LO直接耦合至射频信号路径中,并被以相干方式下变频至输出。结果产生混频器积,表现为直流失调,加入信号链里存在的任何残余直流失调中。

1.2.2何为镜像

对于混频器而言,还是引用图1的理想混频器的构架进行分析和描述,FIN被设置为基带频率为1 MHz的FBB, FLO被设置为本振频率为500 MHz的FLO。如果是理想混频器,它将产生一个输出,其中包含两个信号音,频率分别为499 MHz和501 MHz,如果我们有用的信号为501MHz,那么499MHz的信号就是无用的信号。简单的理解以本振信号为中心和501MHz对称的信号,既可以简单的理解为有用信号的镜像。推广到零中频的IQ分析,问题可能变得更加复杂一些,只能叠加方法去分析。

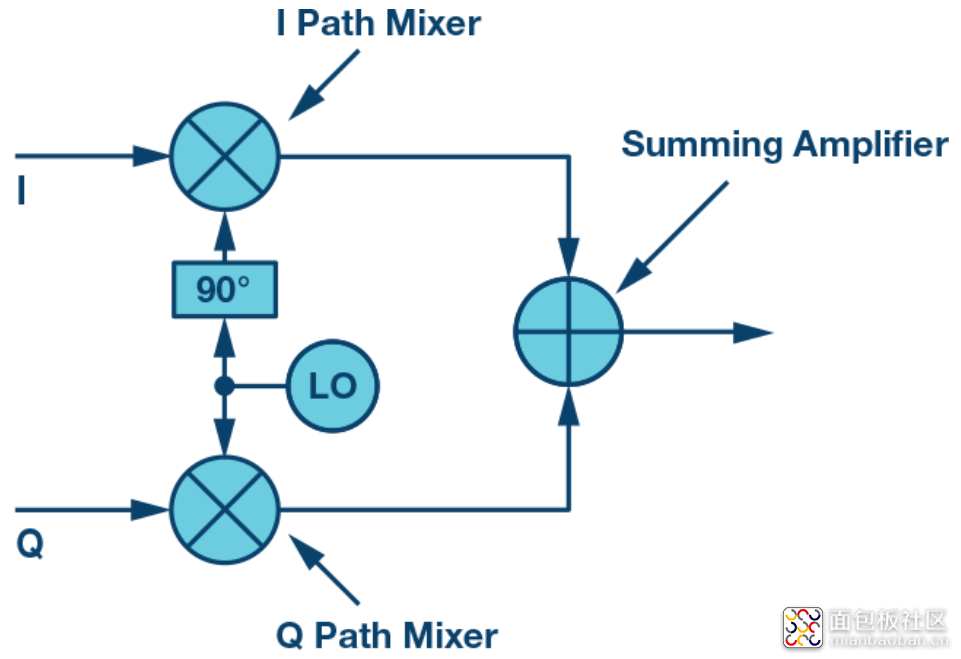

1.2.2.1复数RF混频器基本构架

图3是采用上变频器(发射机)配置的复数混频器原理图。两条并 行路径各有独立混频器,一个公共本振向这些路径馈送信号,本振与其中一个混频器的相位相差90°。两个独立输出随后在求和放大器中求和,产生所需的RF输出。不管是对于ADC输入或是DAC输出,零中频的基本的构架都是适用的。

图3. 复数发射机基本架构

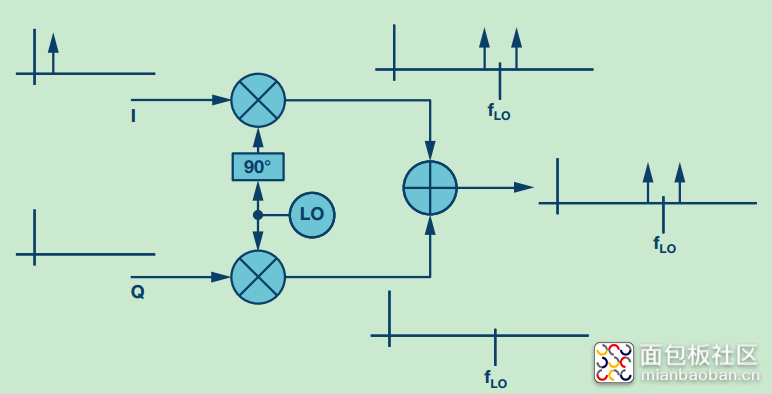

在研究I和Q信号的在输出端的贡献时,我们应该采用电路分析的基本叠加定理进行分析和推导。该配置有一些简单但非常有用的应用。假设仅在I输入上输入一个信号音,但是在Q输入端口不施加任何的输入信号,如图4所示。假定I输入上的信号音频率为x MHz,则I路径中的混频器产生LO频率±x的输出。由于没有信号施加于Q输入,此路径中的混频器产生的频谱为空,I混频器的输出直接成为RF输出。

图4. I路径分析

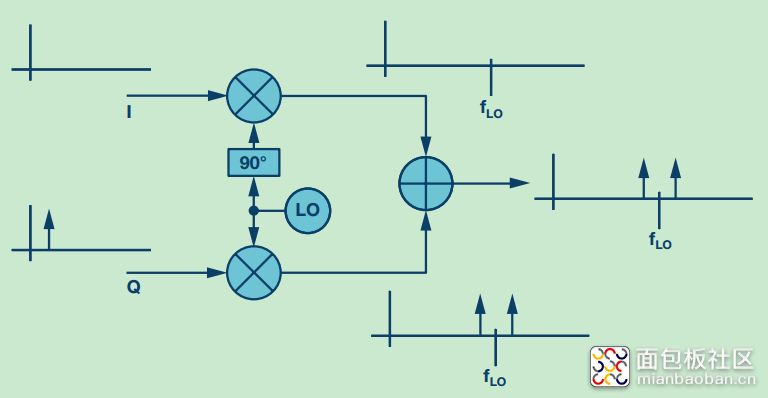

同理,假设仅向Q输入施加一个频率为x的信号音。 Q混频器进而产生信号音为LO频率±x的输出。由于没有信号施加于I输入,其混频器输出静音, Q混频器的输出直接成为RF输出,输出结果如图5所示。

图5. I路径分析

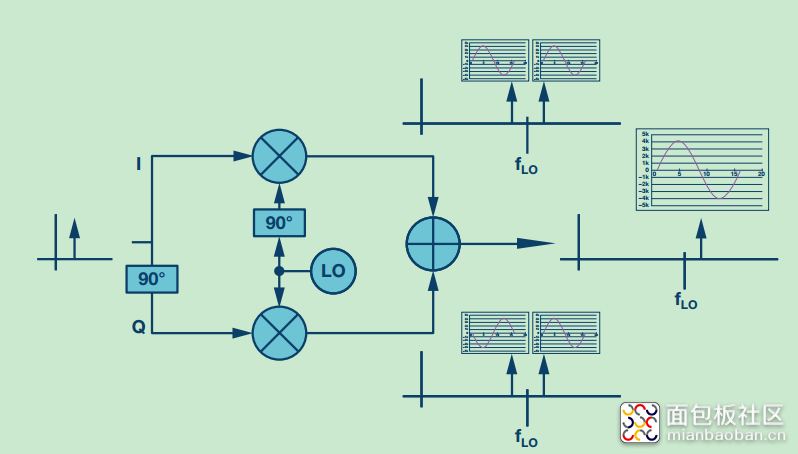

看起来,图4和图5的输出似乎完全相同。但实际上,二者有一个关键差异,那就是相位。假设将相同信号音同时施加于I和Q输入,并且输入通道之间存在90°相移,如图6所示

图6. 同时施加I和Q信号的路径分析

对于混频的过程,可以理解为两个信号在时域上乘积频域上的卷积,对于复数混频构架而言,I和Q分别混频在叠加即可。

在合路后的输出只有一根单点得到输出信号,这就是我们需要单音信号。仔细审视混频器输出,我们观察到: LO频率加输入频率的信号是同相的,但LO频率减输入频率的信号是异相的。这导致LO上侧的信号音相加,而下侧的信号音相消。没有任何滤波,我们便消除了其中一个信号音(或边带),产生的输出完全位于LO频率的一侧。

在合路后的输出只有一根单点得到输出信号,这就是我们需要单音信号。仔细审视混频器输出,我们观察到: LO频率加输入频率的信号是同相的,但LO频率减输入频率的信号是异相的。这导致LO上侧的信号音相加,而下侧的信号音相消。没有任何滤波,我们便消除了其中一个信号音(或边带),产生的输出完全位于LO频率的一侧。

上面计算的I信号比Q信号超前90°。如果变更配置使得Q信号比I信号超前90°,那么可以预期会有类似的相加和相消,但在这种情况下,所有信号将出现在LO的左测。详细计算不在赘述,请参照上述。

理论上应当可以让全部能量仅落在LO的一侧。然而,当 时,在实践中完全相消是不可能发生的,有一些能量会留在LO的另一侧,这就是所谓镜像。为了完全消除镜像, I和Q混频器输出的幅度必须完全一致,而在LO镜像侧上彼此之间的相位恰好相差180°。如果不能满足上述相位和幅度要求,那么图4所示的相加/相消过程就会不太理想,镜像频率的能量仍会存在。

时,在实践中完全相消是不可能发生的,有一些能量会留在LO的另一侧,这就是所谓镜像。为了完全消除镜像, I和Q混频器输出的幅度必须完全一致,而在LO镜像侧上彼此之间的相位恰好相差180°。如果不能满足上述相位和幅度要求,那么图4所示的相加/相消过程就会不太理想,镜像频率的能量仍会存在。

也给ZIF无线电器件也带来了挑战,复数混频器具有同相 (I) 信号和正交相 (Q) 信号。一旦这些信号的相位或幅度出现任何不匹配,组合上变频的I信号和Q信号时会导致求和和消除性能下降,相比于在其他架构(例如超外差架构)中,可以在中间级进行镜像滤波。 ZIF架构的主要优势是去除了这些滤波器和中间混频器级,但这需要极佳的I和Q平衡才能将镜像幅度降低到可接受水平。

1. 不满足要求的指标

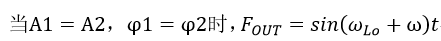

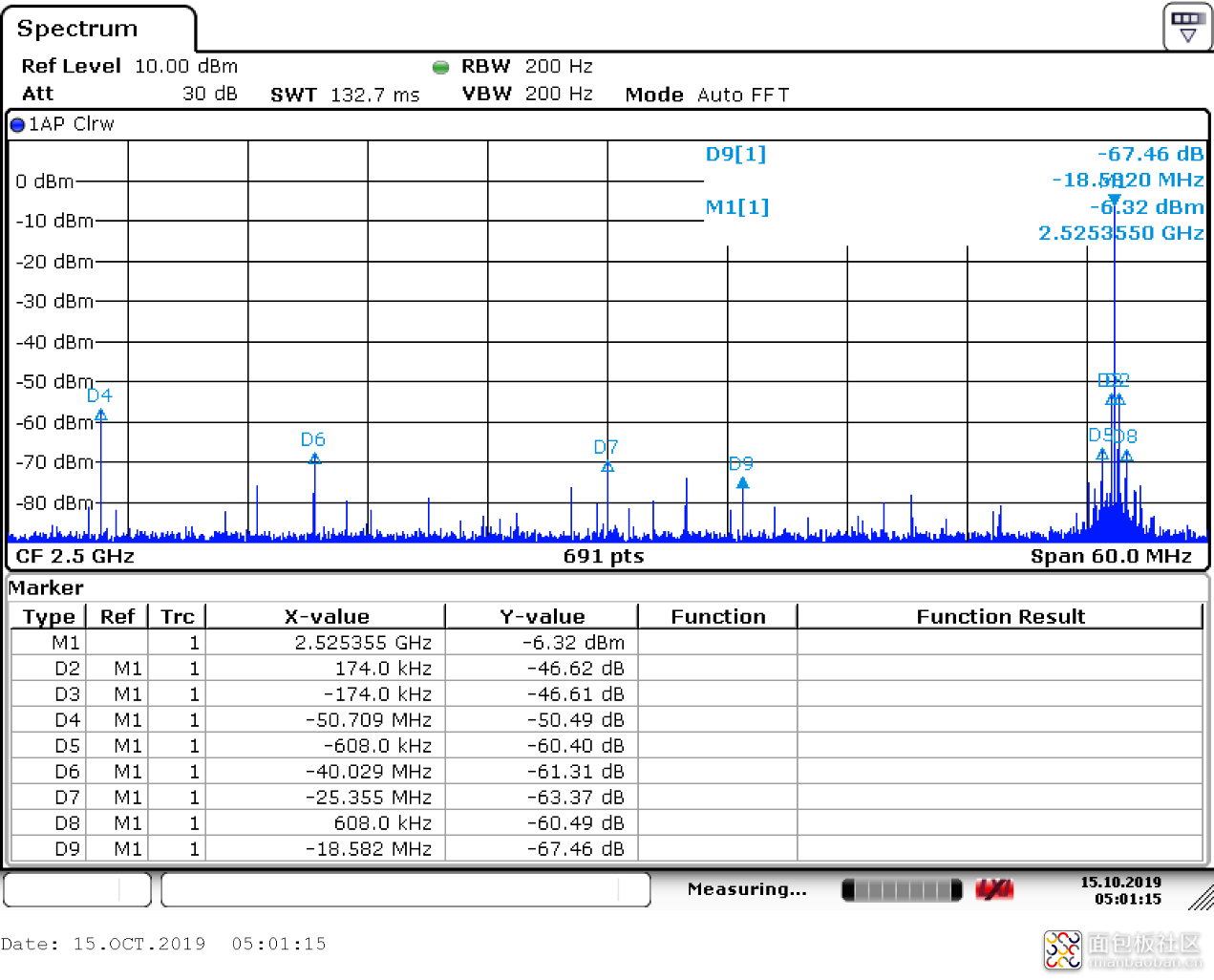

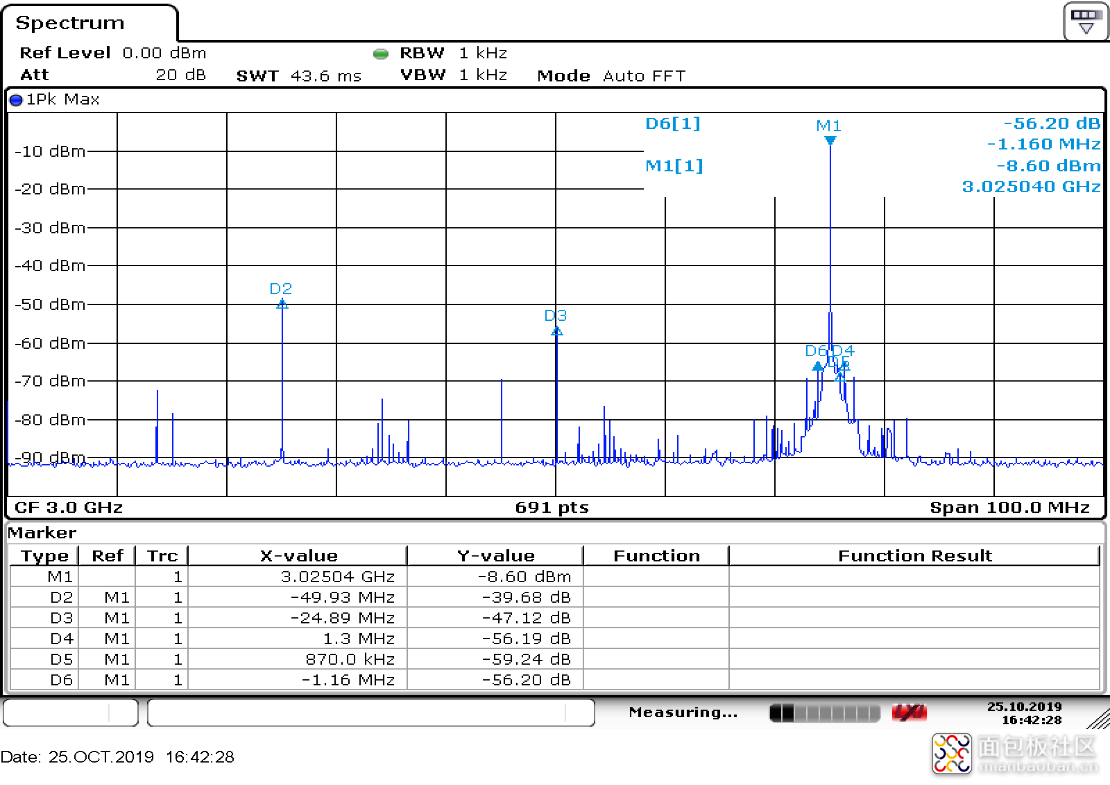

图7. DAC实际输出频谱

如图7,在性能测试时,DAC输出性能测试,本振为2.5GHz,NCO频率为正偏25MHz,对于输出而言2.525GHz为有用信号,2.5GHz为本振泄露,2.475GHz为镜像。通过测试的结果来看,DAC输出性能指标为本振泄露为44dBc,而镜像抑制只有47dBc。协议要求镜像抑制大于45dBc,实际测试的镜像抑制指标满足协议要求,但是切换本振之后,3GHz性能只有39dBc。同时在实际输出的DAC频谱上,本振泄露和镜像抑制在跳,不是一个固定的值。

2. 与开发板性能对比

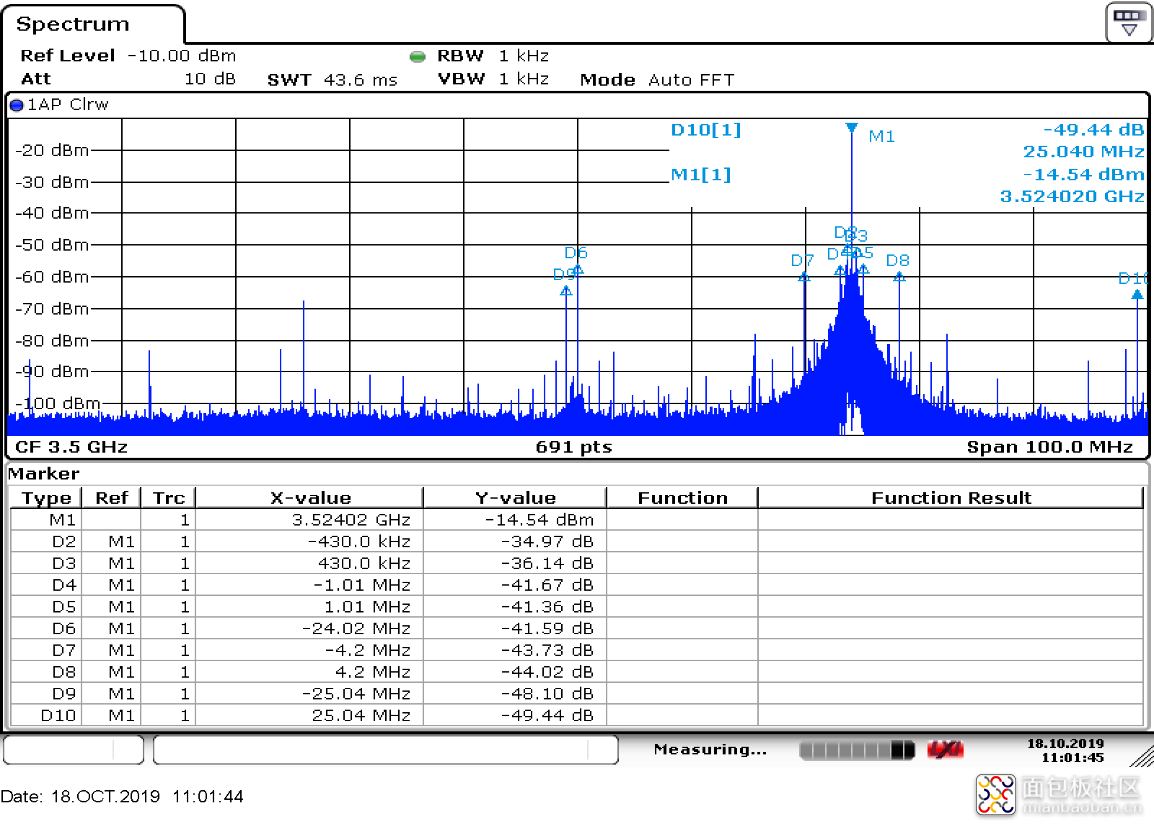

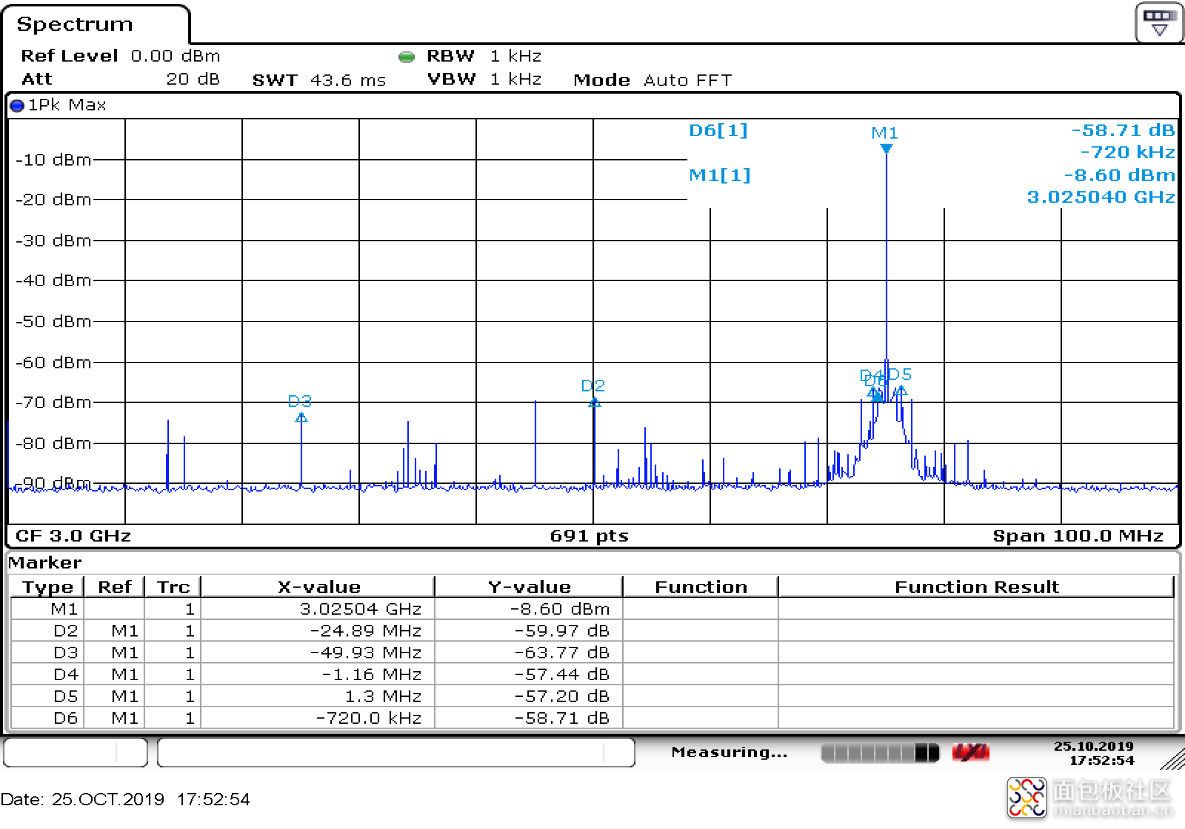

图8. 开发板DAC实际输出频谱

如图8,测试验证开发板DAC输出性能测试,本振为2.5GHz,NCO频率为正偏25MHz,对于输出而言2.525GHz为有用信号,2.5GHz为本振泄露,2.475GHz为镜像。通过测试的结果来看,DAC输出性能指标为本振泄露为63dBc,而镜像抑制只有50dBc。对比之下相差10dB,同时DAC输出的本振泄露和镜像抑制是一个比较固定的值,不会跳。同时开发板近带的杂散也比较多。

3. 问题分析

4.1本振泄露和镜像抑制在跳问题

验证1 更改NCO频率

DAC性能测试时,采用的NCO为24M,AD9361的系统时钟也是25M,为了排除时钟的泄露带来的误差,修改NCO的频率为24M,测试结果如图9所示,核对DAC输出频谱,发现本振泄露和镜像抑制不会跳,但是在频谱上可以看到和信号频偏25M

的杂散。

图9. NCO 24MHz输出频谱

验证2 采用开发板验证输出

使用开发板测试时,采用的NCO为25M,本振2.5GHz,AD9361的系统时钟也是30M。测试结果如图10所示,本振泄露和镜像抑制是一个比较固定的值,但是在频谱上可以看到和信号频偏30M的杂散。

图10. 开发板NCO 25MHz输出频谱

验证3 更换晶振频率

DAC性能测试时,采用的NCO为25M,AD9361的系统时钟也是30M,测试结果如图11所示,核对DAC输出频谱,发现本振泄露和镜像抑制不会跳,但是在频谱上可以看到和信号频偏30M的杂散。

图11. 采用30M晶体输出频谱

分析上面验证的结果,可以定位本振泄露和镜像抑制在跳,不是一个固定的值的原因是AD9361采用25MHz系统时钟时,25M时钟分量泄露到DAC的输出端上,在NCO为25M时,输出本振泄露就和随信号偏移25M时钟分量进行叠加,导致输出的本振泄露和镜像抑制在跳,解决方案就是更换AD9361的系统时钟为30M,规避25M的叠加。

4.2镜像抑制指标不达标

导致镜像的原因

复数混频器具有同相 (I) 信号和正交相 (Q) 信号。一旦这些信号的相位或幅度出现任何不匹配,组合上变频的I信号和Q信号时会导致求和和消除性能下降,相加/相消过程就会不太理想,镜像频率的能量就会一直存在,就会影响到输出的性能指标。

采用内部QEC校准

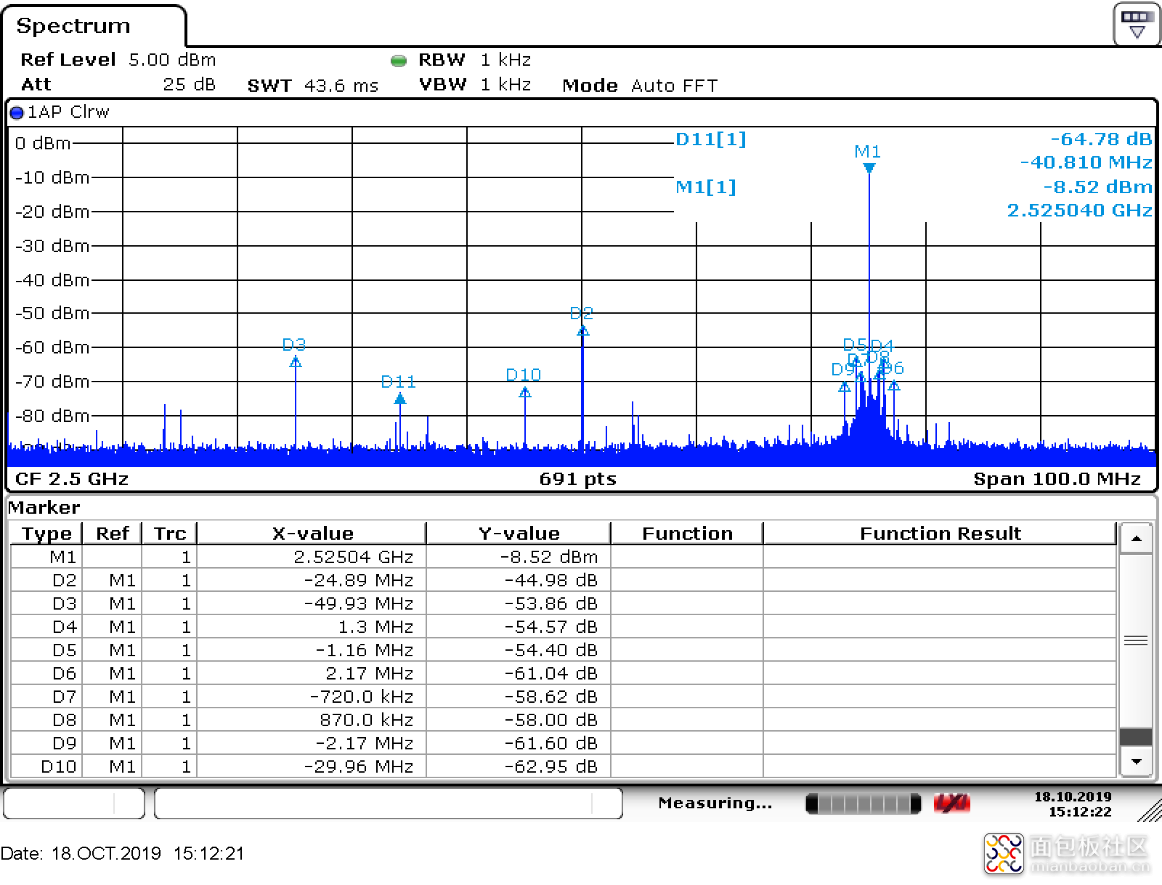

图12 采用QEC校准

如图12,在性能测试时,DAC输出性能测试,本振为3.0GHz,NCO频率为正偏25MHz,对于输出而言3.025GHz为有用信号,3.0GHz为本振泄露,2.975GHz为镜像。通过测试的结果来看,采用内部的QEC校正,DAC输出性能指标为本振泄露为47dBc,而镜像抑制只有39dBc,内部的QEC校正的效果比较差。相比于开发板值相差10dB。

采用手动校准

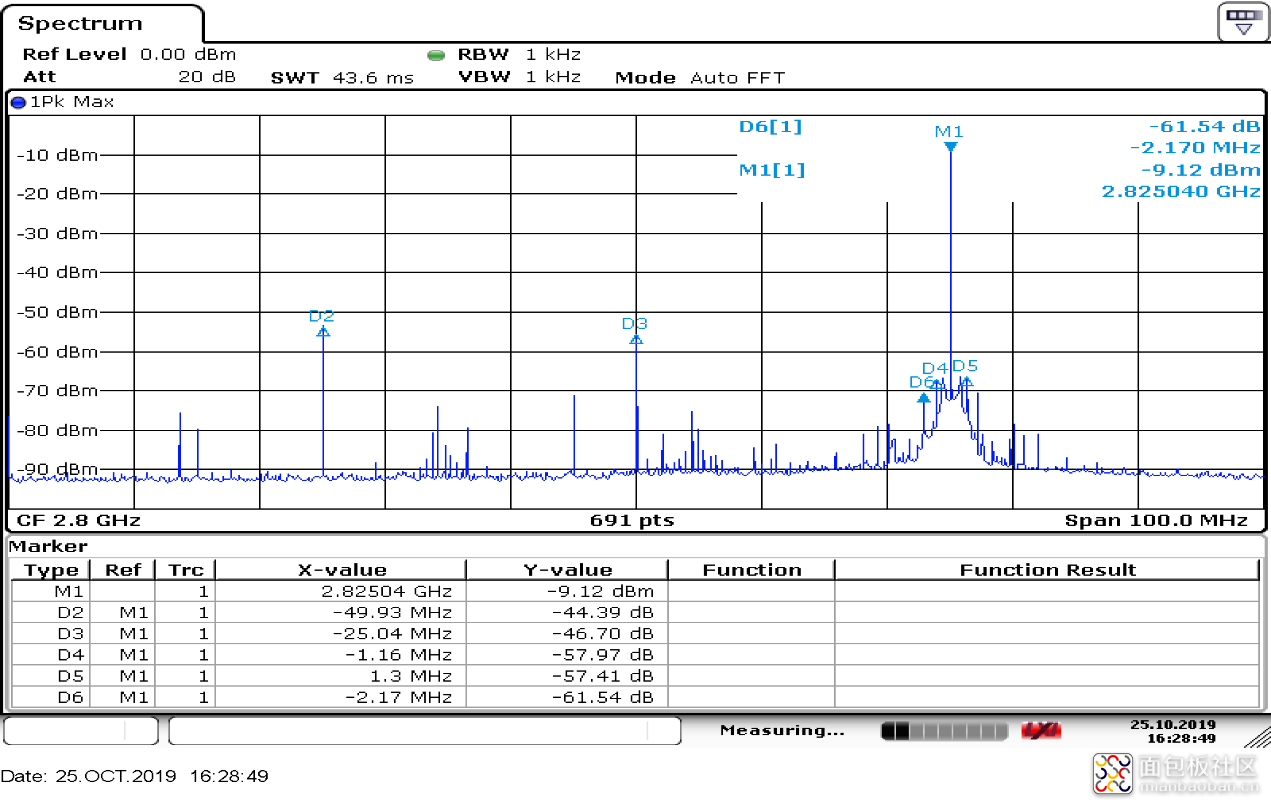

图13 采用手动校准

如图13,在性能测试时,DAC输出性能测试,本振为3.0GHz,NCO频率为正偏25MHz,对于输出而言3.025GHz为有用信号,3.0GHz为本振泄露,2.975GHz为镜像。通过测试的结果来看,采用内部的手动校正,DAC输出性能指标为本振泄露为59dBc,而镜像抑制只有63dBc,内部的手动校正的效果比较好。相比于开发板值优10dB。

4. 提出解决问题的方案

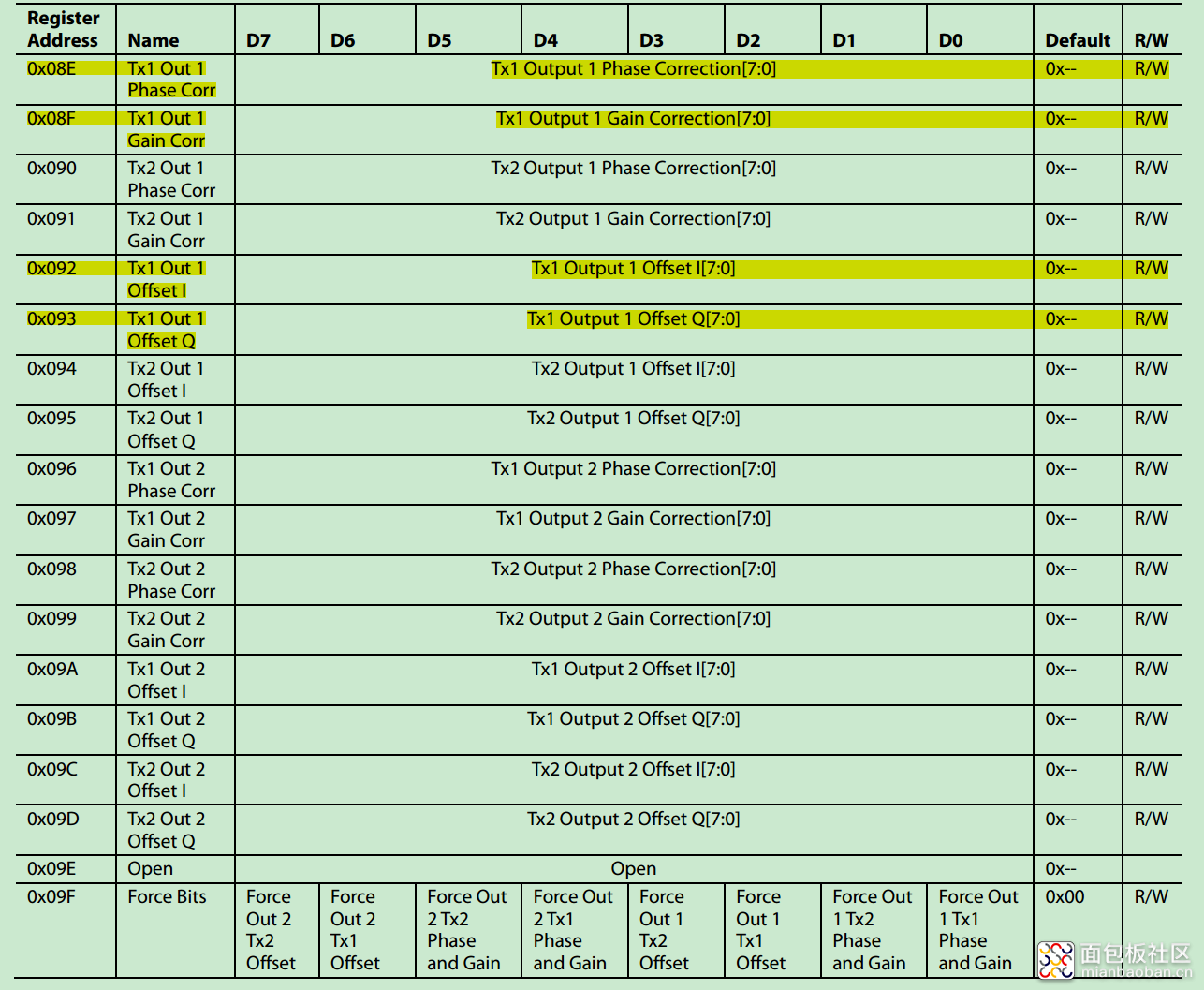

5.1相关寄存器调节

如图14相关寄存器调节

在实践中完全相消是不可能发生的,有一些能量会留在LO的另一侧,这就是所谓镜像。为了完全消除镜像, I和Q混频器输出的幅度必须完全一致,而在LO镜像侧上彼此之间的相位恰好相差180°。如果不能满足上述相位和幅度要求,那么的相加/相消过程就会不太理想,镜像频率的能量会存在。所以在优化AD9361的镜像抑制就是优化I/Q路的相位和幅度,从而使镜像性能到达最佳,同时在优化AD9361的本振泄露就是优化I/Q路路径上的直流偏移,在ADI官方推荐的资料中,给出相关的优化参数,如图14所示,0x08e和0x8f是用于优化输出通道1的镜像抑制,0x092和0x093是用于优化输出通道1的本振泄露,该参数表也为手动校准提供优化方案,手动校准时调节上述的寄存器使本振泄露和镜像抑制可以达到60dBc的抑制。

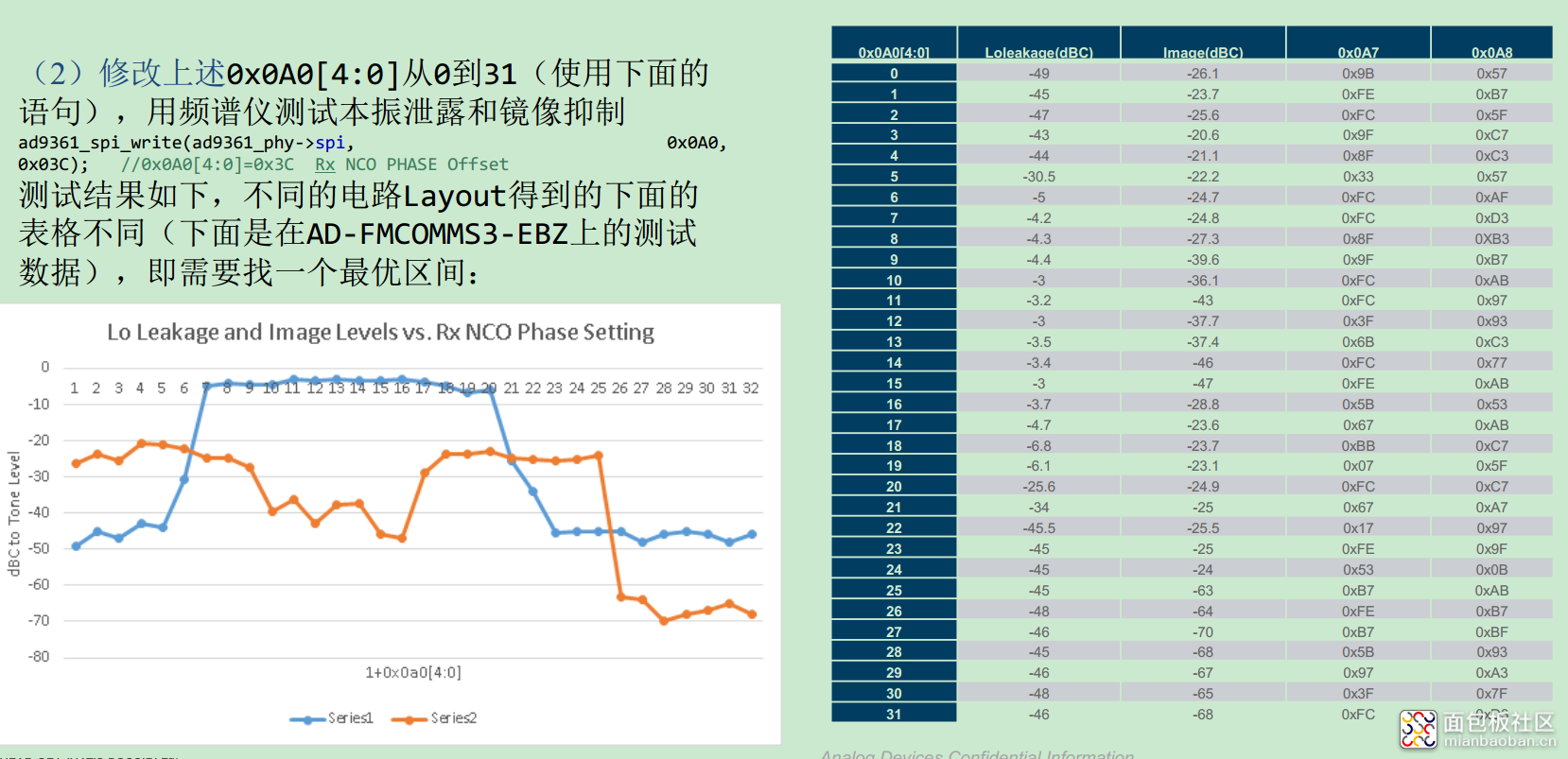

4.2 ADI官方优化方案

如图15 ADI的优化方案

如图15所示,0x0A0[4:0]从0到31(使用下面的语句),用频谱仪测试本振泄露和镜像抑制,调节0x0A0的值,使得本振泄露和镜像抑制达到最优性能。

5. 总结

总体对于AD9361的调试而言,其发射端口的QEC校准机制并不是那么可靠,发射端口的QEC校准不是和接收通道一般具有的跟踪校准,只是上电初始化时应用校准,同时对于AD9361构架而言,其外部并无反馈机制,这就导致在外部电路多样化时无法完成适应外围变化的镜像抑制和本振泄露参数,整体而言就是一个开环的输出端口,可调整的空间比较小。对于后期优化和验证,可以采用其中一个RX通道作为TX的校正反馈路径,在处理器端完成手动QEC算法的校正,以满足在AD9361自身校准不理想下去优化其镜像抑制和本振泄露性能。难点在于手动QEC算法验证上,采用什么样的校准机制进行调整,待后续的验证和开发。