总体简介

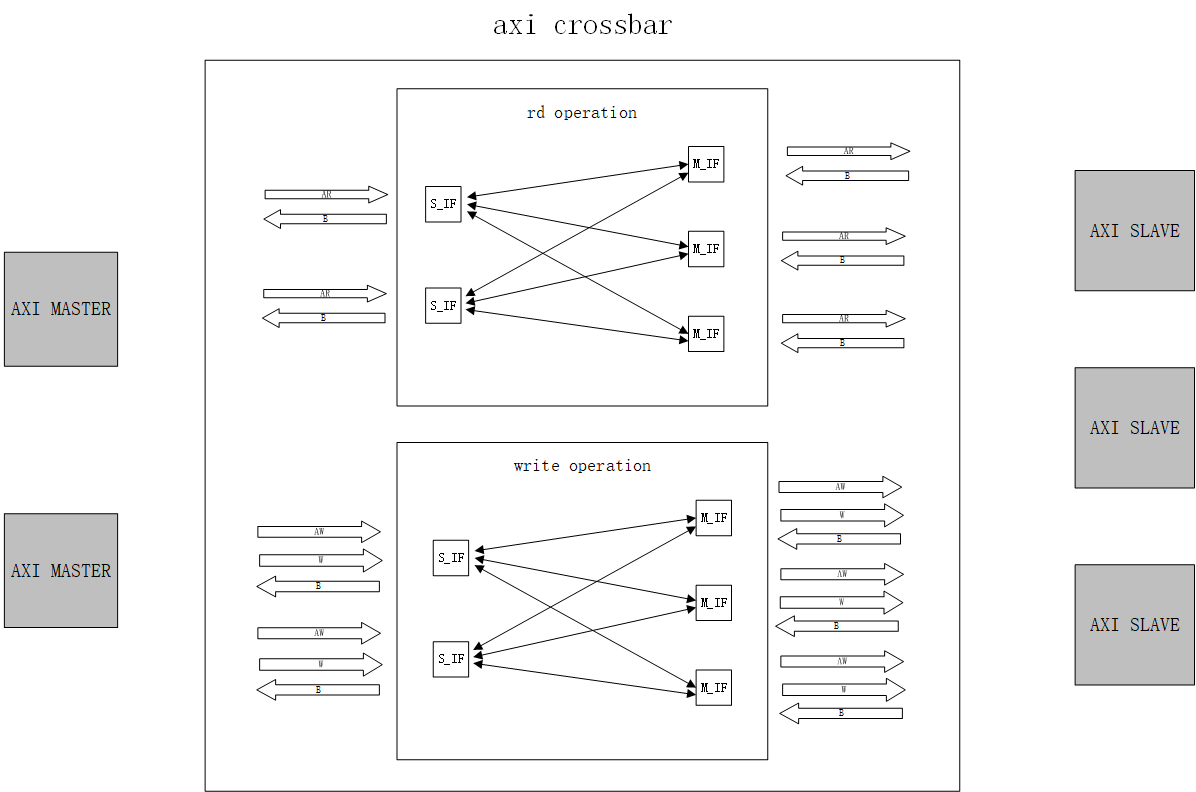

图例是2X3的配置

主要特性

▲支持Master、Slave接口数量配置

▲支持全连接、部分连接

▲支持多threads、多issue效率匹配

▲支持输入BURST最大数量匹配

▲支持Master、Slave接口寄存,优化时序

▲支持Region、User、Secure配置

一些参数描述

DATA_WIDTH:

默认值为32,AXI数据宽度。

ADDR_WIDTH:

默认值为32,AXI地址宽度。

S_ID_WIDTH:

默认值为8,Slave port ID 宽度

M_ID_WIDTH:

默认值为8+clog2(8),Master port ID宽度,多出的clog2(8)为响应路由

Sxx_THREADS:

默认值为2, 允许同时出现的不同ID数量, 若是Master只能发出一种ID,这里设置为1,可以节省资源。

Sxx_ACCEPT:

默认值为16, 允许缓存的数据长度,若是Master不能支持burst传输,这里的长度设置为1,可以节省资源。

Mxx_ISSUE:

默认值为4,Masterxx 最大连续issue的请求个数,有可能连续issue多个AW/AR command。

Mxx_BASE_ADDR:

默认值为0,Masterxx入口起始地址。

Mxx_ADDR_WIDTH:

默认值为{M_REGIONS{32’d24}}, Masterxx地址宽度。它与Mxx_BASE_ADDR共同决定了Masterxx的地址空间。

Mxx_CONNECT_READ:

默认值为{Master_NUM{1’b1}},其可以配置Master可以可以读到某Slave。

Mxx_CONNECT_WRITE:

默认值为{Master_NUM{1’b1}},其可以配置Master可以可以写到某Slave。

Sxx_*_REG_TYPE:

默认值0,1:允许S接口使用简单BUF,2:运行接口使用skid buffer,可以提升效率和时序。

Mxx_*_REG_TYPE:

默认值0,1:允许M接口使用简单BUF,2:运行接口使用skid buffer,可以提升效率和时序。

感悟

axi crossbar需要结合自身SOC系统的heavy程度,选择合适的配置,否则会对芯片的面积、时序带来负面影响。相较于总线,上层架构的设计对系统性能的影响是最大的,因此需要首要考虑。。