要让CH32V003正常工作,首先要对它的时钟源进行配置。CH32V003的最高工作频率为48MHz,因此给它的主时钟频率最大不能超过48MHz。实际上,通常会使用频率较低的晶振,以降低外部电磁干扰,然后再通过内部倍频的方式把主时钟频率提高。根据管方手册给出的数据,外部晶振的频率范围是4~25MHz,一般情况下可使用24MHz晶振,然后经内部PLL进行2倍频,把主时钟工作频率设置为48MHz。

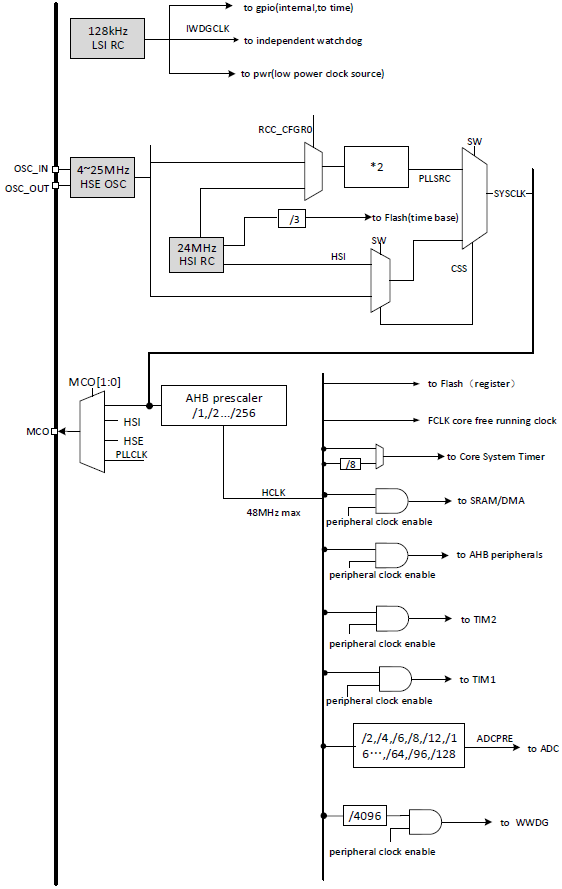

要对CH32V003的时钟进行配置,必须要了解它的时钟结构,先来看一下它的时钟结构图,如下图所示。

从上图中可以看到,CH32V003的时钟源主要有三个,即内部低速时钟(LSI)、内部高速时钟(HSI)和外部高速时钟(HSE)。

内部低速时钟是芯片内部RC振荡器产生的约128KHz时钟信号,它可以在停机或待机模式下保持运行,为RTC时钟、独立看门狗和唤醒单元等提供一个时钟基准。

内部高速时钟是芯片内部RC振荡器产生的24MHz时钟信号,它的启动时间很短,能够在不需要任何外部器件的条件下为整个系统提供时钟。此外,在外部晶体振荡器失效时,HSI时钟会被作为备用时钟源(时钟安全系统)。

外部高速时钟是通过外部石英晶体或陶瓷谐振器产生的高速时钟,它也可以由外部振荡器直接送入,为系统提供更为精确的时钟源。外部高速时钟的频率限定在4-25MHz之间。

从上图中还可以看出,系统时钟(SYSCLK)除了可以取HSI和HSE之外,还可以取自PLL时钟的输出。而PLL时钟可来自HSI或HSE,并且输出是它们的2倍频。这就表明,系统时钟的最高频率48MHz只能来自于PLL时钟,且输入PLL的时钟为24MHz。部分单元设置了时钟使能端,置1时使能时钟,置0时禁止时钟。

在上图中,AHB时钟(HCLK)可直接取自系统时钟(SYSCLK),也可取自系统时钟的分频(2~256分频),由时钟配置寄存器0(RCC_CFGR0)来确定,默认不分频(直接取SYSCLK)。AHB时钟可以提供给片内的FLASH单元、FCLK单元、内核定时器(可选8分频)、SRAM及DMA单元、AHB外设单元、定时器2、定时器1、ADC单元(可选2~128分频)和窗口看门狗单元(经4096分频)。

另外,从图中还可看出,SYSCLK、HSI、HSE及PLLCLK四个时钟,还可以通过MCO引脚(复用在PC4)进行输出,以供外部检测使用。

下表给出了与时钟配置相关的寄存器信息,一共有9个。

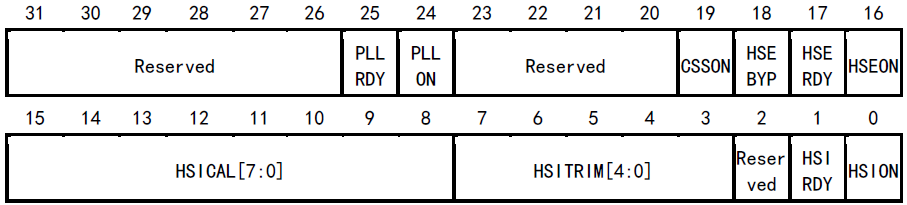

先来看时钟控制寄存器R32_RCC_CTLR,下面是它的全部位结构。

(1)第31~26位及其后的23~20、2均为保留位。

(2)第25位(PLLRDY)为PLL 时钟就绪锁定标志位。该位为只读属性,当PLL时钟锁定(稳定)后由硬件置1。该位复位值为0。

(3)第24位(PLLON)为PLL 时钟使能控制位。置1时使能PLL时钟,置0时关闭PLL时钟。在芯片进入待机低功耗模式后,该位由硬件自动清零。该位复位值为0。

(4)第19位(CSSON)为时钟安全系统使能控制位。置1时使能时钟安全系统,置0时关闭时钟安全系统。在使能时,当HSE时钟准备好(即HSERDY位置1时),硬件将开启对HSE的时钟监测功能。当发现HSE时钟异常时会触发CSSF标志及NMI 中断。当HSE时钟没有准备好时,硬件会关闭对HSE的时钟监测功能。该位复位值为0。

(5)第18位(HSEBYP)为外部高速晶体旁路控制位。置1时外部高速晶体或陶瓷谐振器被旁路,置0时不旁路,该位要在第16位HSEON为0的情况下才允许写入。该位复位值为0,一般在使用外部有源晶振时,需要把该位置1。

(6)第17位(HSERDY)为外部高速晶体振荡HSE稳定就绪标志位。该位为只读属性,当HSE稳定后由硬件置1,为0时表示HSE还未稳定。在第16位HSEON置0后,该位需要6个HSE周期才能自动清零。该位复位值为0。

(7)第16位(HSEON)为外部高速晶体振荡HSE使能控制位。置1时使能HSE振荡器,置0时关闭HSE振荡器。芯片进入待机低功耗模式后,该位由硬件清零。该位复位值为0。

(8)第15~8位(HSICAL)为内部高速时钟HSI的校准值,在系统启动时被自动初始化。该值不允许用户修改,为只读属性。

(9)第7~3位(HSITRIM)为内部高速时钟HSI的调整值。该调整值叠加到HSICAL(第15~8位)的数值上,可根据电压和温度的变化调整内部高速RC振荡器的频率。复位值为16,每个步长的调整变化率约为60KHz,可以把HSI调整到24MHz±1%的精度 。

(10)第1位(HSIRDY)为内部高速时钟HSI振荡稳定就绪标志位,该位为只读属性,当HSI稳定后由硬件置1,为0时表示HSI还未稳定。在第0位HSION置0后,该位需要6个HSI周期才能自动清零。该位复位值为1。

(11)第0位(HSION)为内部高速时钟HSI使能控制位。置1时使能HSI振荡器,置0时关闭HSI振荡器。当芯片从待机模式返回或用作系统时钟的外部振荡器HSE发生故障时,该位会由硬件自动置1来启动内部24MHz的RC振荡器。该位复位值为1。

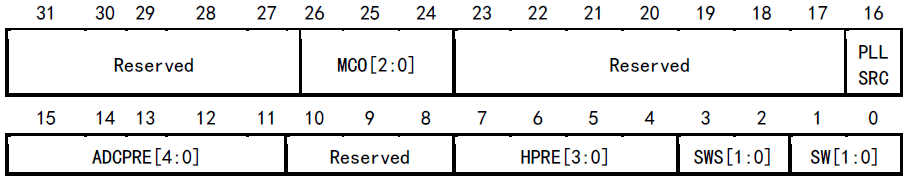

接下来看第0号时钟配置寄存器RCC_CFGR0,下面是它的全部位结构。

(1)第31~27位及其后的23~17、10~8均为保留位。

(2)第26~24位(MCO)为MCO引脚时钟输出控制选择位。这三位的值为000时不输出时钟,为100时选择系统时钟(SYSCLK)输出,为101时选择HSI时钟输出,为110时选择HSE时钟输出,为111时选择PLL时钟输出 。复位值为000。

(3)第16位(PLLSRC)为PLL输入时钟源选择位。该位在PLL关闭时才可写入,置1时选择不分频的HSE时钟,置0时选择不分频的HSI时钟。该位复位值为0。

(4)第15~11位(ADCPRE)为ADC时钟来源预分频控制选择位,复位值为0。这五位值与分频系数的具体对应关系如下所示。注意,ADC时钟最高频率不能超过24MHz。

(5)第7~4位(HPRE)为AHB时钟来源预分频控制选择位。这四位的值为0x0时表示不分频,值从0x1到0x7分别对应2~8分频(连续),值从0x8到0xF分别对应2~256分频(2倍)。当AHB时钟来源的预分频系数大于1时,必须开启预取缓冲器。复位值为0x02(即3分频)。

(6)第3、2两位(SWS)为系统时钟状态值。该值由硬件提供,为只读属性。这两位的值为00时表明当前系统时钟是HSI,为01时表明当前系统时钟是HSE,为10时表明当前系统时钟是PLL。复位值为00。

(7)第1、0两位(SW)为系统时钟来源选择位。这两位的值为00时选择HSI作为系统时钟,为01时选择HSE作为系统时钟,为10时选择PLL作为系统时钟。在使能了时钟安全系统的情况下(即CSSON=1时),当芯片从待机和停止模式返回或用作系统时钟的外部振荡器HSE发生故障时,由硬件强制选择HSI作为系统时钟。复位值为00。

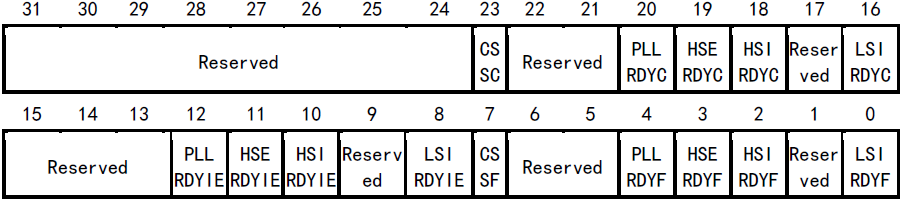

接下来是时钟中断寄存器RCC_INTR,下面是它的全部位结构。

(1)第31~24位及其后的22~21、17、15~13、9、6~5、1均为保留位。

(2)第23位(CSSC)为清除时钟安全系统中断标志位。置1时清除CSSF中断标志(第7位),置0时无动作。该位复位值为0。

(3)第20位(PLLRDYC)为清除PLL振荡器就绪中断标志位。置1时清除PLLRDYF中断标志(第4位),置0时无动作。该位复位值为0。

(4)第19位(HSERDYC)为清除HSE振荡器就绪中断标志位。置1时清除HSERDYF中断标志(第3位),置0时无动作。该位复位值为0。

(5)第18位(HSIRDYC)为清除HSI振荡器就绪中断标志位。置1时清除HSIRDYF中断标志(第2位),置0时无动作。该位复位值为0。

(6)第16位(LSIRDYC)为清除LSI振荡器就绪中断标志位。置1时清除LSIRDYF中断标志(第0位),置0时无动作。该位复位值为0。

(7)第12位(PLLRDYIE)为PLL就绪中断使能位。置1时使能PLL就绪中断,置0时关闭PLL就绪中断。该位复位值为0。

(8)第11位(HSERDYIE)为HSE就绪中断使能位。置1时使能HSE就绪中断,置0时关闭HSE就绪中断。该位复位值为0。

(9)第10位(HSIRDYIE)为HSI就绪中断使能位。置1时使能HSI就绪中断,置0时关闭HSI就绪中断。该位复位值为0。

(10)第8位(LSIRDYIE)为LSI就绪中断使能位。置1时使能LSI就绪中断,置0时关闭LSI就绪中断。该位复位值为0。

(11)第7位(CSSF)为时钟安全系统中断标志位。该位为只读属性,值为1时表示HSE时钟失效并产生时钟安全中断CSSI,值为0时表示无时钟安全系统中断。该位由硬件置位,由软件写1到CSSC位清除。该位复位值为0。

(12)第4位(PLLRDYF)为PLL时钟就绪中断标志位。该位为只读属性,值为1时表示PLL时钟锁定产生中断,值为0时表示无PLL时钟锁定中断。该位由硬件置位,由软件写1到PLLRDYC位清除。该位复位值为0。

(13)第3位(HSERDYF)为HSE时钟就绪中断标志位。该位为只读属性,值为1时表示HSE时钟就绪产生中断,值为0时表示无HSE时钟就绪中断。该位由硬件置位,由软件写1到HSERDYC位清除。该位复位值为0。

(14)第2位(HSIRDYF)为HSI时钟就绪中断标志位。该位为只读属性,值为1时表示HSI时钟就绪产生中断,值为0时表示无HSI时钟就绪中断。该位由硬件置位,由软件写1到HSIRDYC位清除。该位复位值为0。

(15)第0位(LSIRDYF)为LSI时钟就绪中断标志位。该位为只读属性,值为1时表示LSI时钟就绪产生中断,值为0时表示无LSI时钟就绪中断。该位由硬件置位,由软件写1到LSIRDYC位清除。该位复位值为0。

从以上描述可以看出,RCC_INTR寄存器的0~7位为中断标志(末尾字符F), 8~12位为中断使能(末尾字符E),16~23位为清除标志(末尾字符C)。

接着看APB2外设复位寄存器RCC_APB2PRSTR, 下面是它的全部位结构。

(1)第31~15位及其后的13、10、8~6、3、1均为保留位。

(2)第14位(USART1RST)为USART1接口复位控制位。置1时复位USART1接口模块,置0时无动作。该位复位值为0。

(3)第12位(SPI1RST)为SPI1接口复位控制位。置1时复位SPI1接口模块,置0时无动作。该位复位值为0。

(4)第11位(TIM1RST)为定时器1复位控制位。置1时复位定时器1模块,置0时无动作。该位复位值为0。

(5)第9位(ADC1RST)为ADC1复位控制位。置1时复位ADC1模块,置0时无动作。该位复位值为0。

(6)第5位(IOPDRST)为PD端口复位控制位。置1时复位PD端口模块,置0时无动作。该位复位值为0。

(7)第4位(IOPCRST)为PC端口复位控制位。置1时复位PC端口模块,置0时无动作。该位复位值为0。

(8)第2位(IOPARST)为PA端口复位控制位。置1时复位PA端口模块,置0时无动作。该位复位值为0。

(9)第0位(AFIORST)为IO辅助功能复位控制位。置1时复位IO辅助功能模块,置0时无动作。该位复位值为0。

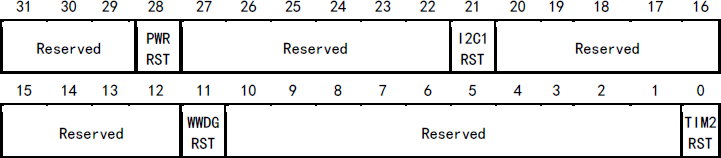

RCC_APB2PRSTR寄存器管理的是位于APB2区域的模块的复位,还有位于APB1区域的模块的复位管理,由APB1外设复位寄存器RCC_APB1PRSTR负责,下面是它的全部位结构。

(1)第31~29位及其后的27~22、20~12、10~1均为保留位。

(2)第28位(PWRRST)为电源接口复位控制位。置1时复位电源接口模块,置0时无动作。该位复位值为0。

(3)第21位(I2C1RST)为I2C1接口复位控制位。置1时复位I2C1接口模块,置0时无动作。该位复位值为0。

(4)第11位(WWDGRST)为窗口看门狗复位控制位。置1时复位窗口看门狗模块,置0时无动作。该位复位值为0。

(5)第0位(TIM2RST)为定时器2复位控制位。置1时复位定时器2模块,置0时无动作。该位复位值为0。

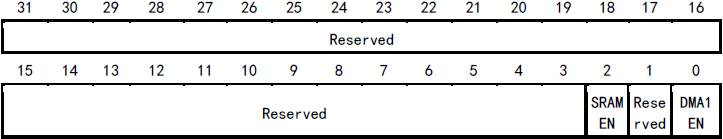

接下来看AHB外设时钟使能寄存器RCC_AHBPCENR,下面是它的全部位结构。

(1)第31~3位及其后的1均为保留位。

(2)第2位(SRAMEN)为SRAM接口时钟使能位。置1时表示在睡眠模式下SRAM接口模块时钟依然开启,置0时表示在睡眠模式下SRAM接口模块时钟被关闭。该位复位值为1。

(3)第0位(DMA1EN)为DMA1时钟使能位。置1时开启DMA1模块时钟,置0时关闭时钟。该位复位值为0。

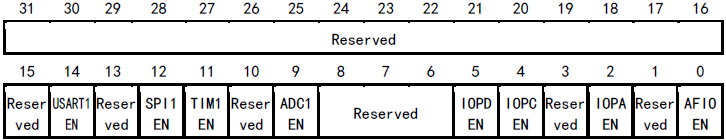

RCC_AHBPCENR寄存器控制的是位于AHB区域模块的时钟,还有位于APB区域模块的时钟需要控制,分别由APB2外设时钟使能寄存器RCC_APB2PCENR和APB1外设时钟使能寄存器RCC_APB1PCENR来负责。先来看APB2外设时钟使能寄存器RCC_APB2PCENR,下面是它的全部位结构。

(1)第31~15位及其后的13、10、8~6、3、1均为保留位。

(2)第14位(USART1EN)为USART1接口时钟使能位。置1时开启USART1接口模块时钟,置0时关闭时钟。该位复位值为0。

(3)第12位(SPI1EN)为SPI1接口时钟使能位。置1时开启SPI1接口模块时钟,置0时关闭时钟。该位复位值为0。

(4)第11位(TIM1EN)为定时器1时钟使能位。置1时开启定时器1模块时钟,置0时关闭时钟。该位复位值为0。

(5)第9位(ADC1EN)为ADC1时钟使能位。置1时开启ADC1模块时钟,置0时关闭时钟。该位复位值为0。

(6)第5位(IOPDEN)为PD端口时钟使能位。置1时开启PD端口模块时钟,置0时关闭时钟。该位复位值为0。

(7)第4位(IOPCEN)为PC端口时钟使能位。置1时开启PC端口模块时钟,置0时关闭时钟。该位复位值为0。

(8)第2位(IOPAEN)为PA端口时钟使能位。置1时开启PA端口模块时钟,置0时关闭时钟。该位复位值为0。

(9)第0位(AFIOEN)为IO辅助功能时钟使能位。置1时开启IO辅助功能模块时钟,置0时关闭时钟。该位复位值为0。

接着看APB1外设时钟使能寄存器RCC_APB1PCENR,下面是它的全部位结构。

(1)第31~29位及其后的27~22、20~12、10~1均为保留位。

(2)第28位(PWREN)为电源接口时钟使能位。置1时开启电源接口模块时钟,置0时关闭时钟。该位复位值为0。

(3)第21位(I2C1EN)为I2C1接口时钟使能位。置1时开启I2C1接口模块时钟,置0时关闭时钟。该位复位值为0。

(4)第11位(WWDGEN)为窗口看门狗时钟使能位。置1时开启窗口看门狗模块时钟,置0时关闭时钟。该位复位值为0。

(5)第0位(TIM2EN)为定时器2时钟使能位。置1时开启定时器2模块时钟,置0时关闭时钟。该位复位值为0。

注意,当外设时钟没有启用时,软件不能读出这些外设对应寄存器的数值,返回的数值始终为0。

最后来看控制/状态寄存器RCC_RSTSCKR,下面是它的全部位结构。

(1)第31位(LPWRRSTF)为低功耗复位标志位。该位为只读属性,当发生了低功耗管理复位时由硬件置1,由软件写1到RMVF位(第24位)清除。该位复位值为0。

(2)第30位(WWDGRSTF)为窗口看门狗复位标志位。该位为只读属性,当发生了窗口看门狗复位时由硬件置1,由软件写1到RMVF位清除。该位复位值为0。

(3)第29位(IWDGRSTF)为独立看门狗复位标志位。该位为只读属性,当发生了独立看门狗复位时由硬件置1,由软件写1到RMVF位清除。该位复位值为0。

(4)第28位(SFTRSTF)为软件复位标志位。该位为只读属性,当发生了软件复位时由硬件置1,由软件写1到RMVF位清除。该位的复位值要根据实际情况来确定。

(5)第27位(PORRSTF)为上电/掉电复位标志位。该位为只读属性,当发生了上电/掉电复位时由硬件置1,由软件写1到RMVF位清除。该位的复位值要根据实际情况来确定。

(6)第26位(PINRSTF)为外部手动复位(NRST引脚)标志位。该位为只读属性,当发生了NRST引脚复位时由硬件置1,由软件写1到RMVF位清除。该位的复位值要根据实际情况来确定。

(7)第25位及其后的23~2位均为保留位。

(8)第24位(RMVF)为清除复位标志控制位。置1时清除所有复位标志,置0时无动作。该位复位值为0。

(9)第1位(LSIRDY)为LSI时钟稳定就绪标志位。该位为只读属性,当LSI稳定后由硬件置1。在第0位LSION置0后,该位需要3个LSI周期才能自动清零。该位复位值为0。

(10)第0位(LSION)为LSI时钟使能控制位。置1时使能内部128KHz的LSI振荡器,置0时关闭LSI振荡器。该位复位值为0。

以上详细描述时钟配置中使用到的寄存器,下面来总结一下:

1、系统时钟可选择来自HSI(默认),HSE及PLL,其中PLL可来自HSI及HSE,并进行2倍频。其时钟来源的选择通过配置RCC_CTLR寄存器和RCC_CFGR0寄存器来决定,分别如下:

(1)配置为HSI的24MHz模式,设置RCC_CTLR的第0位为1(默认值)开启HSI时钟,然后等待第1位变为1即可。如果有必要,可设置RCC_CTLR第3~7位进行频率补偿。

(2)配置为HSE的无源晶振频率模式,设置RCC_CTLR的第16位为1开启HSE时钟,然后等待第17位变为1即可。

(3)配置为HSE的有源晶振频率模式,设置RCC_CTLR的第18位为1启用旁路,然后设置RCC_CTLR的第16位为1开启HSE时钟,最后等待第17位变为1即可。

(4)配置为PLL频率模式,该模式的频率值为HSI或HSE原始频率的2倍频。分两种情况,当使用HSI作为输入时钟时,设置RCC_CTLR的第0位为1(默认值)开启HSI,然后设置设置RCC_CFGR0的第16位为0(默认值)以选择HSI,然后设置RCC_CTLR的第24位为1开启PLL,最后等待第25位变为1即可。当使用HSE作为输入时钟时,设置RCC_CTLR的第16位为1开启HSE,然后设置RCC_CFGR0的第16位为1以选择HSE,然后设置RCC_CTLR的第24位为1开启PLL,最后等待第25位变为1即可。当然,还有一种使用外部有源晶振时的PLL模式,只需要在最前面设置RCC_CTLR的第18位为1启用旁路就行,其余步骤不变。

需要注意的是,根据官方手册的建议,当时钟频率大于24MHz时,在配置完时钟之后,还需要配置一下FLASH的等待状态(FLASH_ACTLR寄存器第0位置1)。

2、系统时钟配置完成后,还可以通过读取RCC_CFGR0的第2、3两位的值,来判断系统时钟当前的选择状态。

3、系统时钟的频率只可能是内部24MHz、外部4~25MHz以及它们的2倍频值(PLL),无其他频率值。但芯片内各个模块的时钟可通过AHB来进行1~256的分频获得。也即系统时钟的最大值只能为PLL的48MHz,而其余时钟则可根据RCC_CFGR0寄存器中的第4~7位来进行分频,最小为256分频,最大为不分频。