1. 超前传输(outstanding transaction)

- 这篇博客中提到,考虑写数字通道有缓存,所以可以在从机返回写回复信号之前,开启下一次的传输。

- 超前传输就是在当前传输完成前,可以开始发起下一次的传输。如果多个事务可以并行处理,那么可以提高系统的性能。

- AXI的从机可以选择是否支持超前传输。

- 如不支持,在第一次地址传输握手成功(后面突发传输的控制信息和地址都已经传输给从机了)后,将AxREADY信号拉低,停止第二次的传输的地址信号和控制信号的发送。

- 直到完成一整个传输之后才可以再次拉高从机的AxREADY信号。

- 超前传输深度

- 表示主机正在进行中的事务数量N,这个概念的本质是缓存区可以保存第二/三/更多批传输数据。

- 假设途中有可以支持的最大数量N个传输事务,那么只有其中结束了几个才可以再次发起几个传输。

2. 多事务乱序

- 什么情况下会用到不同ID的传输事务

- 主机读取DDR时,由于存储性质,读取不同地址所需周期可能很大不同,那么主机在发出多个地址不同的读事务时就可以采用不同的ID,让从机可以乱序响应这些读事务,提高效率。

- outstanding 引入的问题

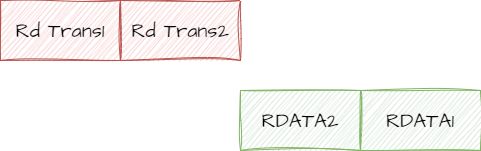

- 以读传输为例,假设从机对不同传输事务的准备周期不同,例如对于事务1是2个准备周期(RDATA1),对于事务2不需要准备周期(RDATA2),那么返回给主机的数据RDATA2会在RDATA1前面。

- 此时主机会分辨不清先返回的数据是哪个传输事务的。

- 以读传输为例,假设从机对不同传输事务的准备周期不同,例如对于事务1是2个准备周期(RDATA1),对于事务2不需要准备周期(RDATA2),那么返回给主机的数据RDATA2会在RDATA1前面。

- 解决方法

- 超前传输需要标识数据所属事务。为此,AXI协议设计了ID号,根据发送方区分ID一共有这几种:

- 主机制定并发送:AWID ARID,标识传输事务。

- 从机制定并发送:RID BID,标识数据或回复信号。

- 上面四个信号对应四个通道,对于写数据通道有WID信号,但是该信号只在AXI3中可以用,AXI4中被取消了,具体原因下面有介绍。

- 超前传输需要标识数据所属事务。为此,AXI协议设计了ID号,根据发送方区分ID一共有这几种:

- ARID相关判断

- 对于ARID相同的多个事务,从机需要根据接收事务的顺序,返回其读数据。可以通过一些重排序电路实现。

- 一种实现方法

- 具体可以看参考文献中的图片,容易理解。

- 新建一个缓冲区域A,以传输事务(地址和控制信息)的到达顺序保存;先准备好的数据与缓冲区域中的传输事务地址进行比对,如果相同,那么读数据直接发送给主机,如果不匹配,那么将读数据打入缓冲区域B,先发送与缓冲区域A地址匹配的读数据。

- 注意这个缓冲区的深度需要在设计时就确定好,AXI协议不支持主机对从机重排序缓冲区深度的调节。

- 一种实现方法

- 对于ARID不同的事务,可以不用重排序,直接按照数据准备顺序返回,加速传输。

- 前面介绍读地址和读数据都有自己的ID号:ARID、RID;对应事务两个ID标为相同。

- 主机接收数据时可以通过RID与ARID进行匹配。

- 对于ARID相同的多个事务,从机需要根据接收事务的顺序,返回其读数据。可以通过一些重排序电路实现。

- 实例(ARID 相同、不同都存在)

- 对于ARID不同的支持乱序,对于ID相同的,支持重排序。

- ARID的缓冲区

- 为每一个不同的ARID提供了一块缓冲区,该缓冲区中也包含了前面“重排序”介绍的传输事务缓冲区以及传输数据缓冲区。

- 数据的RID与缓冲区的ARID进行比对,将数据送入相同ID的缓冲区内,再决定是否需要重排序。

- 具体可以看参考文献中的图片,容易理解。

- 当ARID数量较多时,硬件开销很大,但是从机支持的ARID不会超过16个。

- 写事务传输 & 读事务传输

- 写事务没有必要乱序传输,主机(一般为CPU/DMA)可以直接控制写数据和写地址、控制信号。

- AXI4规定写数据是顺序传输的,不需要WID将写数据与写事务进行匹配。

- 写事务中存在一个写回复信号,该信号处理方式可以认为与读数据相同,存在AWID和BID进行判断。

- 协议规定读事务和写事务之间是不存在顺序约束的,但是主机可以额外在发送写事务和读事务时添加顺序约束。

如有错误,请指正!!