Cortex M3 CORE

发布时间 2024-01-07 12:06:47作者: Icer_Newer

Cortex CM3 内核架构

- CM3内核主要包含几个部分:取指(Fetch)\指令译码(Decoder/DEC)\执行(EXEC)\ALU

- 内存取数通过load & store指令,就是通过一个LSU(Load & Store Unit)单元

- Status - 状态上报

- 内核和外部进行交互都是通过中断进行的,CPU通常不会一直查询外部的设备,降低CPU效率,通常都是设备发起中断给CPU,CPU进行响应中断

- PMU模块是可选的

- 接口 - AHB总线接口和PPB接口,两个总线的命令会进行一定的转换

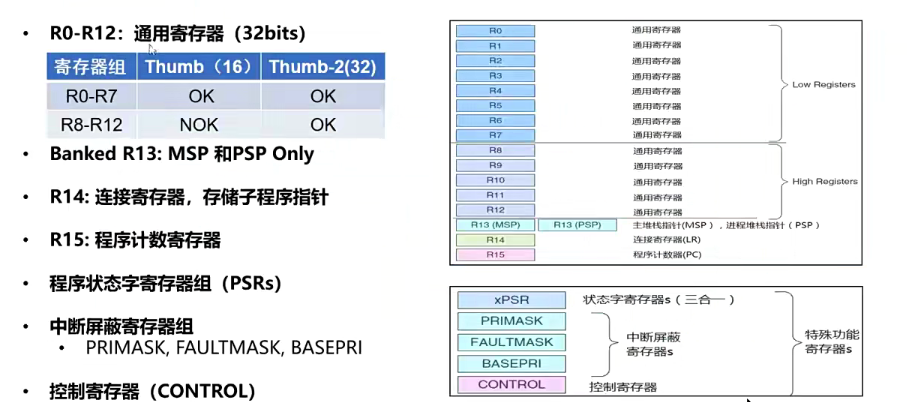

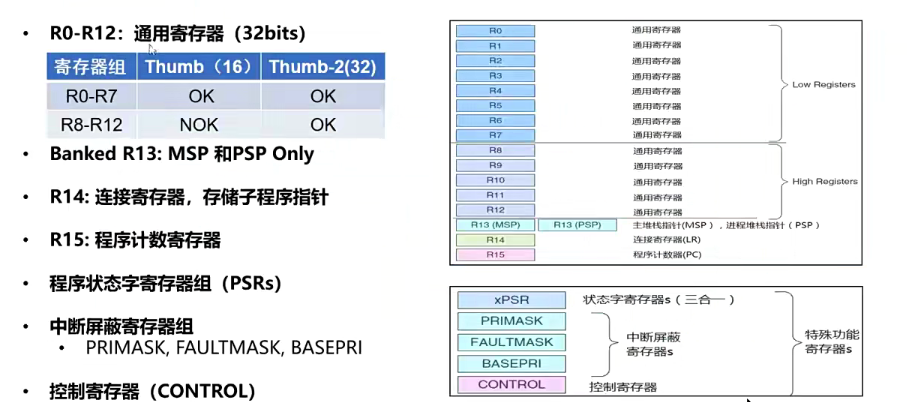

内核 - 寄存器

- 内置13个通用寄存器

- MSP(master stack point)和PSP(processor stack point) - 用于防止内存踩踏

- 连接寄存器,存储子程序指针,cpu收到中断之后,可以执行中断处理程序,读到stack point,之后可以执行程序;如果子程序的指针存储在CPU外部的RAM中,访问需要时间,中断处理程序执行比较慢

- 程序计数寄存器 - 计算机执行指令完成后,下一条指令的取址通过程序计数寄存器存储

- 程序状态字寄存器组(PSRs)

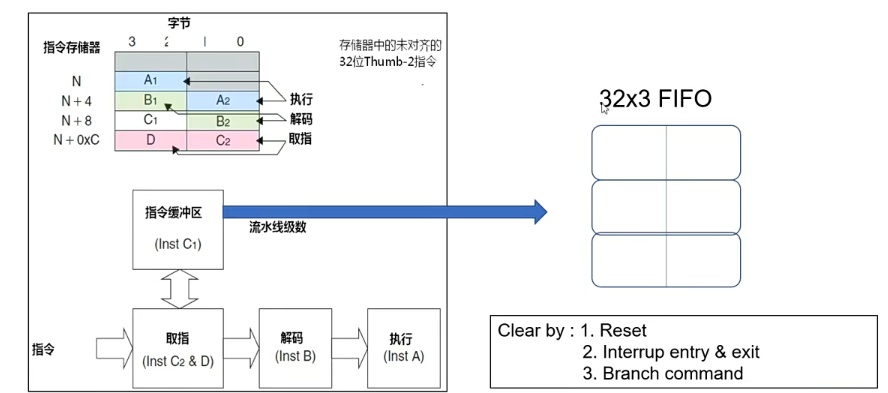

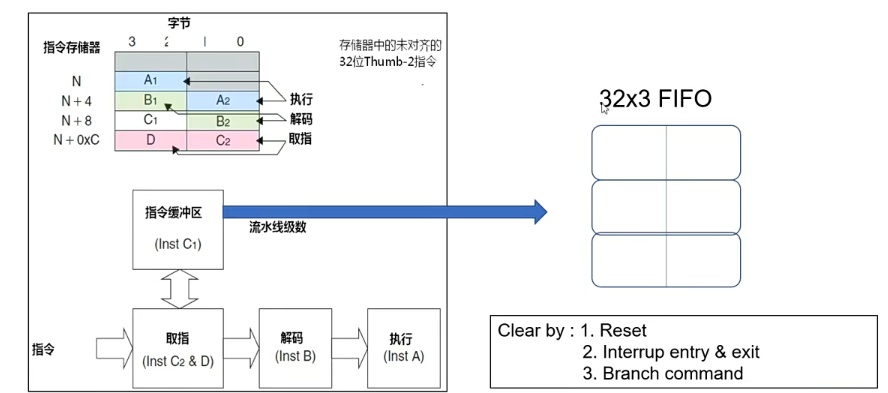

指令预取

- 指令预取,指令取回来之后会放到指令的缓冲区(32*3 FIFIO),第一个指令存储在FIFO的第一个存储单元,下一个指令会存在下一个FIFO单元

- Thumb 16bit - 一个cycle会取两个指令,数据总线是32bit的,所以一个cycle可以取两个指令

- Thumb2 - 一个cycle取一个指令

- 取值\解码\执行的指令依次进行存储,取指才能连续

- 如果遇到中断或者分支预测(if-else)的时候,流水会被打断,FIFO就会被清除掉

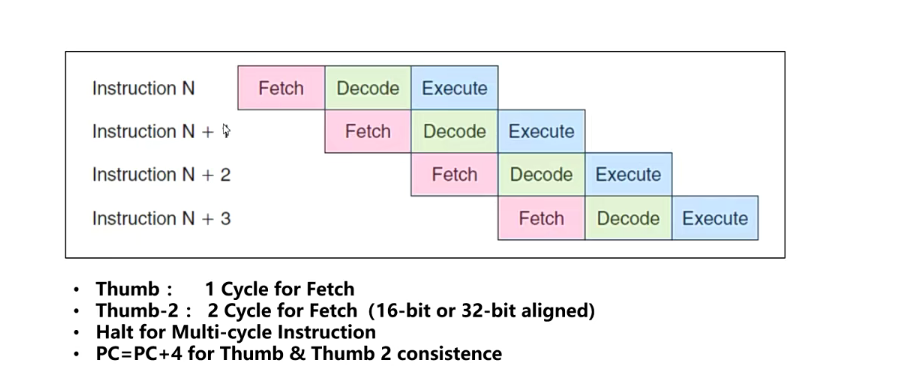

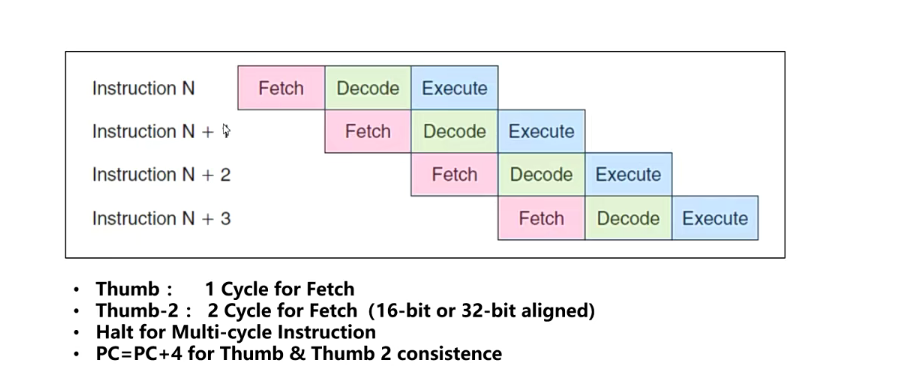

流水技术

- 非流水的操作,一个指令执行完成之后才会执行下一个指令

Interface

- AHB_Lite主要包含Icode(指令接口)\Dcode(数据接口)\System Bus(系统总线命令)