3D Nand基本原理-你想知道的全在这里(上)

0. 引言:

最近想要从原理上了解3D Nand,搜了很多资料,发现很多资料都只侧重某一方面,不够系统详细,于是把自己学习获得的知识总结归纳一下。

1. 存储器诞生:

现代计算机构想是基于冯 · 诺依曼架构的图灵计算机设备,关于这两个人,历来都有现代计算机之父的争议,这里我们不做讨论,可以简单的理解为,图灵从理论上去论证了现代计算机可以实现,也就是给现代计算机注入了灵魂,而冯诺依曼给这样的计算机提出了具体的构想---中央处理器(CPU)和存储器分开的存储程序计算机,也就是给现代计算机构筑了肌肉。

今天我们主要聊一聊计算机的存储器,存储器的功能是存储信息,因为1945年冯洛伊曼和他的小伙伴发表了“101页报告”,规定了现代计算机中使用二进制,所以存储器中就是存储 '0'和 '1',然后通过人们规定的ASCII 码(美国信息交换标准代码)来翻译二进制数字与人们日常生活中常用的信息,这些信息包括我们现在计算机设备中常用的指令(空格,回车等),字母,数字,标点。1992年发布了Unicode,也就是字符标准码,补足了ACSII码表达其他国家地区语言不足的缺点。根据'0','1' 不同的排列组合,就能得到不同的信息和人类进行交流。这里提一下,为什么是二进制呢,因为受限于当时甚至现在的技术,人们制造的场效应晶体管(FET)只有在区分关态和开态的时候,其灵敏度是最高的。如果我们在开和关之间引入其他的态,一般是用固定电压下的电流值来区分态,所以当外界环境比较恶劣时,容易引起电流不受控制的变大或变小(例如温度因素,半导体的本征载流子浓度严重依赖温度,温度较高时,本征载流子浓度迅速增大,电流会急剧升高,变流变得不可控,从而失去目的开关与放大作用,所以CPU等半导体器件运行,降温散热非常重要),从而致使计算机运行中对态的错误识别,态越多,其误码率也就越高。

中央存储器运行过程一般是取指令--->解码--->执行,这个时间就是所谓的一个时钟周期。这个时间的倒数就是我们目前CPU频率,有趣的是,这么多年了我们貌似一直卡在4~5 GHz之间,难以提升,其实这个频率已经非常高了,现代计算机的性能瓶颈也不在这里,而是各个单元相互连接制约了信息的传递,总有一些朋友追求极致去超频,其实无论怎么超,也不会有数量级的变化,当然超频一时爽,一直超频一直爽,液氮超频了解一下?

一个完整的CPU应该包括控制单元,寄存器,ALU(算数逻辑单元),RAM(随机存取存储器)。当然这个RAM一般是独立存在的器件,通过数据线,地址线,读取线以及写入线连接CPU,这样的一个构造其实就可以运行很多计算机指令了,但是有一个问题就是,这个计算机只能在供电的情况下才能使用,断电后,就立马失去了运行的数据。那么为了解决这个问题,我们就发明了ROM(只读存储器),这种存储器可以将想要的CPU运行结果保留起来,即便是断电情况下,也可以长时间保存,比如你写的文档,下载的音乐、视频都可以长时间保存起来。这里存储器的一种分类方式就出来了,根据断电后数据能否长时间保存,我们将存储器分为易失性存储器和非易失性存储器。下面是我汇总的存储器基本分类思维导图。

事实上, RAM和ROM的读操作几乎相同。更恰如其分地说有时把RAM称为读-写存储器。然而,人们一直开发ROM的重写能力。因此,现在RAM和ROM之间的主要差别在于擦除和可编程的频度和容易程度。RAM重写和读的机会总是相等的;而ROM的读的频率远大于重写。

这句话可能让大家对RAM以及ROM的认识更加清楚,由于RAM也是FET构造,其读写能力是通过电刷新的,CPU中的控制单元会经常将指令存入RAM,从RAM中读取指令,所以其读写的频率基本相等。对于ROM,现在我们用的比较多的形式是NOR flash 和NAND flash,根据不同的场景,使用不同的存储器,Nor flash 多用于嵌入式系统;手机,PC,USB,一般是存放数据,这个数据我们的读取的次数一般比写入要多,但是写的频率还是比较高的,这里一般使用NAND flash,这个我们稍后将展示原因。

2. 存储器的底层原理:

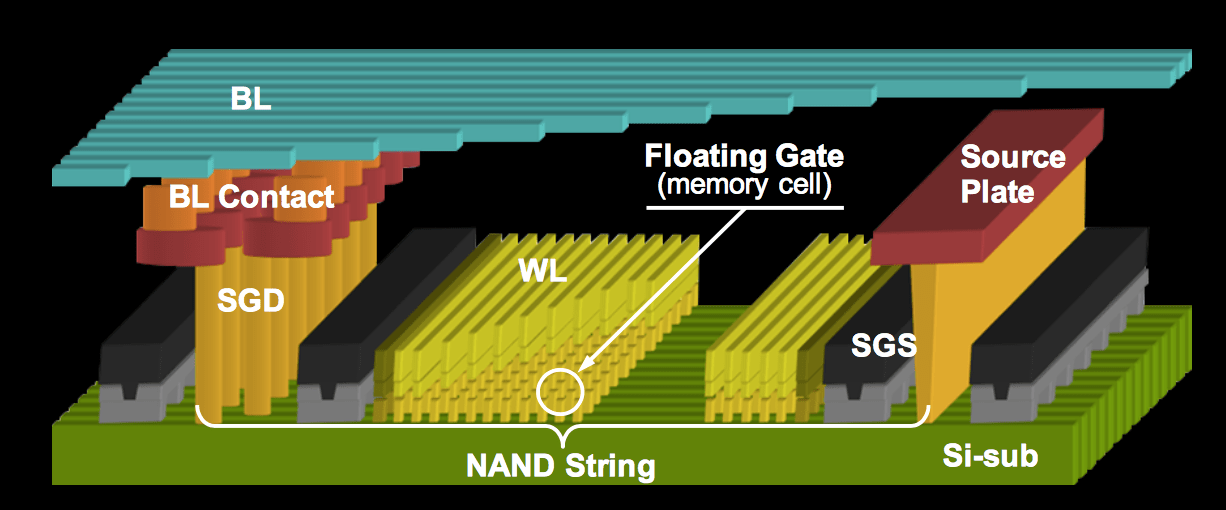

今天的展示的主角就是ROM家族中NOR flash 和 NAND flash,至于RAM,可以日后单独讨论,ROM的发展历程就是上面思维导图中ROM部分。发展到现在,NOR flash和 NAND flash都是在FET的基础上,增加一个浮柵上,通过将电子注入到浮栅上,实现编程。其基本构造如下:

2.1 存储器理论

以上图为例,通过在n沟道FET栅极上偏置正(负)电压,在源漏沟道之间感应负(正)电荷,可以打开(关闭)源漏之间的电通道。这个打开源漏之间电流通道的电压叫做阈值电压 �� ,也就是沟道从平带到反型所需要的电压。那么在在栅极氧化层中再插入一个浮栅,当浮栅上充入电子时,此时由于电子的屏蔽作用,想要将n沟道FET打开,则需要更高的 �� 。我们把未注入电子时的 �� 叫做 ��1 ,把注入电子后的 �� 叫做 ��0 。试想一下,当我们用大于 ��1 小于 ��0 的电压 ��′ 去尝试开启FET,若这时电路被打开,则说明FET浮栅中未注入电子,若没有打开,则说明FET浮栅中注入了电子。我们知道在CPU逻辑电路中,开态表示‘1’,关态表示‘0’,沿用这个逻辑,浮栅上未注入电子,是开态,表示逻辑 '1' ;浮栅上注入电子,是关态,表示逻辑‘0’。不要怀疑,这个和你的直觉的确相反,在这里,注入电子表示写入‘0’;擦除电子,表示写入了'1'。这种类型的存储器的原理概括成一句话就是,通过在浮栅上注入电子改变FET阈值电压 �� 来实现存储功能。

2.2 存储器两种编程方式

我们已经为存储器注入了灵魂,现在来铸造其肌肉,也就是如何实现注入、擦出电子的过程。注入电子主要有两种过程原理,一种是热电子注入,另外一种是F-N 隧穿(Fowler-Nordheim隧穿)。热电子注入就是在源漏之间加上一个电压,由于压降原理,在漏端附近电场强度达到最大值(因为源极一般接地),因此电子在电场作用中,在漏极附近能量最大,变成热电子,当其能量大于 ��/���2 界面势垒,电子就能越过势垒(经典力学),进入到浮栅,热电子在电场作用下,与晶格发生碰撞会形成二次电子,二次电子也能注入到浮栅上。为了让电子能够有效的注入到浮栅上,一般会在控制栅上加一个正偏压,形成三角形势垒(如下图),帮助电子注入到浮栅上,与此同时就会产生一个栅电流,有电流就会有功耗,这是一个弊端。

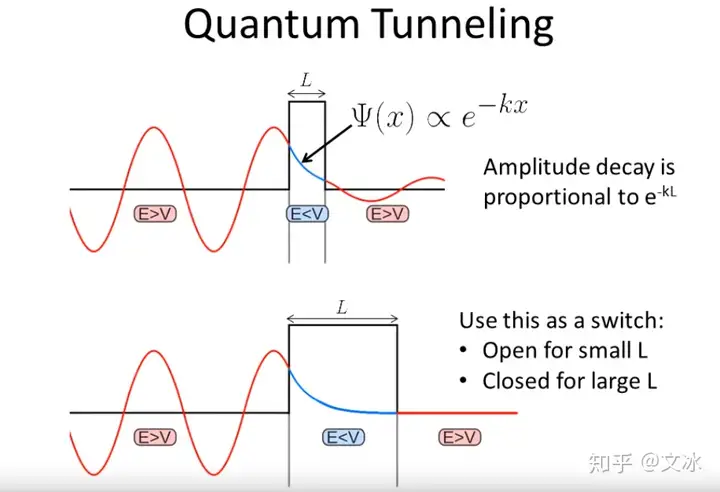

另外一个方式就是F-N隧穿,根据量子力学理论,电子有几率可以隧穿比本身能量高的势垒。隧穿的几率严重依赖势垒的高度与宽度,在存储器中,这个势垒就是介电层,介电层一般是 ���2 ,但是也有其他高介电常数的材料应用在存储器中。材料决定了,势垒高度就决定了,其厚度就变成唯一的参数,我们可以通过控制势垒的厚度来控制电子是否可以隧穿,起到开关的作用。

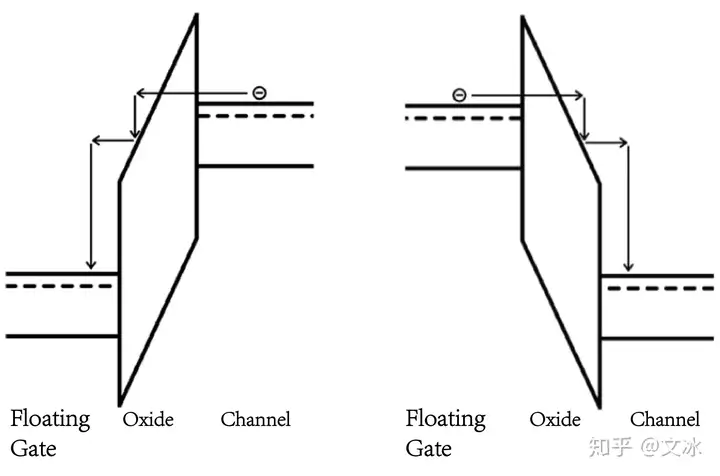

有了这样的理论,我们如何实现呢?好在控制栅可以帮助我们更改势垒厚度,还记得刘恩科《半导体物理学》中第八章MIS结构吗?控制栅加上电压,介电层能带会弯曲成为一个三角形势垒,这对电子来说,其势垒厚度就变窄了。所以我们可以通过控制栅来改变介电层势垒厚度,从而控制电子是否能够隧穿介电层进入浮栅。下图是示意图。左图表示控制栅加正偏压使得沟道电子隧穿底部介电层进入浮栅,完成编程‘0’右图表示控制栅加负偏压使得浮栅电子隧穿底部介电层到沟道,完成编程‘1’。

讲到这里,存储器的底层原理就讲完了。总结一下,存储器就是在FET的基础上,在介电层中增加一个浮栅,通过控制栅,改变电子注入到浮栅或是从浮栅上擦除,从而实现编程,注入电子表示编程写入‘0’,擦除电子表示编程写入‘1’。读取过程是通过在栅极偏置一个比未注入电子FET阈值电压稍高的电压,源漏之间通就是‘1’,断就是‘0’,刚好和写入对应。编程注入电子的过程分为两种,一种热电子注入,一种是F-N隧穿,但是擦除电子只有F-N隧穿。F-N隧穿中加在控制栅的电压很高远大于读取的电压,毕竟是要隧穿过去。这里讲的是浮栅器件,还有一种器件就是电荷俘获器件,对比与浮栅器件,这里的电子俘获层一般是氮化硅,电子主要俘获在氧化物-氮化物界面。打个比方,浮栅器件俘获的电子如水流一般,而电荷俘获器件如奶酪一般。其F-N隧穿是修正的F-N隧穿,首先隧穿一个很薄的梯形氧化层势垒,然后再是一个三角形氮化硅势垒。

3. 存储器重要参数

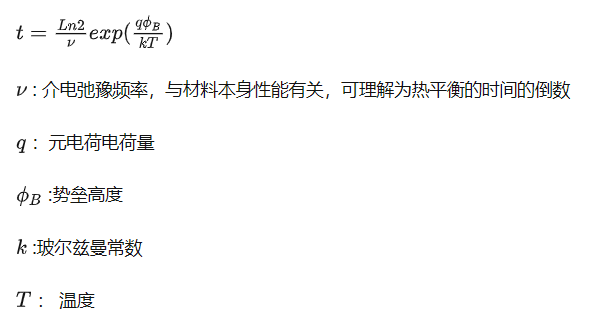

基本介绍了一下存储器的基本单元,再看看其中影响它的重要参数。一个存储器,我们看中什么?便宜,存储密度大,存储时间久,读写速度快,读写次数多。存储器小声BB:MMP,人类啊,什么都要好的,臣妾做不到啊。便宜就不说了,需要采用低廉的材料,成熟的工艺(降低边际成本),而存储密度就需要先进的工艺技术。我们着重看看后面三个参数,存储时间久,这个好理解,存储器无非存储的是‘1’和‘0’。‘1’还好说,就是浮栅上没有电子,前面说了想要注入电子,是需要很高的控制栅电压的,所以电子不会自发进入到浮栅上,从而消灭你的数据‘1’。麻烦的是数据‘0’,一旦电子注入到浮栅上后,即便我们不再对存储器进行擦除、写入过程,电子仍然会慢慢逃逸出去(浮栅上的电子化学势比较高),我们一般定义电荷量减小到初始值的50% 时,就称为数据丢失。这个时间可以用下面的公式得到:

从中可以看到势垒高度是最重要的参数,势垒高度由介电层的厚度决定。上面我们说的是存储器不再进行擦除与写入过程,这样电子逃逸时间大概是100年,也就是说,理论上,你将SSD写满数据后,然后再也不写入、擦除数据,这份数据可以放置100年。但实际上不太可能完全不擦除、写入。根据擦除、写入的频率,SSD的理论时间是10-30年不等,如果非常频繁,甚至3-5年就坏了。这是因为擦除、写入过程中浮栅下介电层里的化学键退化,导致介电作用减弱,数据保存的时间越来越短,直到最终不能使用。(以前认为擦除、写入过程会致使介电层变薄,最新研究指出并不会变薄,而是化学键退化,电子变得更加容易进出。)

根据性能要求,我们当然希望存储器保存时间越久越好,那么就需要介电层厚度比较厚,但是厚了就有一个问题,编程时间会增加,因为势垒大了之后,隧穿电流会降低,因为 编程是否成功是看浮栅上电荷的变化量,而一定数目电荷量是电流的时间积分,电流小了,时间自然就长了。所以为了平衡这两个关键参数,工业届会慢慢去优化介电层厚度,尽量去平衡这对欢乐冤家。下层介电层厚度一般在8 nm左右,上层厚度一般在14 nm左右。

最后一个参数就是编程次数,编程次数一定是和使用时间有关的,不谈时间的编程次数就是耍流氓。上面说了,每一次擦除、写入过程都会对介电层造成损耗,这是不可逆的。也就是说,擦写频率越高,寿命越短,擦写频率越低,寿命越长。我找了一篇论文,论文中的研究成果显示:若擦写次数在3000次以内,数据能够保存3年左右,若擦除次数在150000,那么数据就只能保存3天。当然并不是说擦写150000次后,就不能用了,你可以在3天之内,读取数据后,重新写入,就可以再用了,但是随着次数的增多,保存的时间会越来越短,看到没有,非易失存储器慢慢在向易失性存储器“进化”。为了解决这样的问题,目前只有从软件层面去解决,通过优化算法代码,降低存储器的擦写频率,从而提高寿命。

4. NOR 和 NAND 的区别

在存储器的家族中,现在的明星无疑就是NAND和NOR这对兄弟了,都是由日本的桀冈富士雄(Fujio Masuoka)发明,这两个兄弟的诞生、发展故事可以写一部狗血剧,具体的内容老狼写过了,我就不赘述了,这里贴上链接:https://zhuanlan.zhihu.com/p/26745577

这篇帖子写的很好,也写了NAND和NOR的区别。我这里顺着上篇内容,依然是从原理上入手去解释他们的区别,做一下区分吧。

4. 1 NOR和NAND 结构

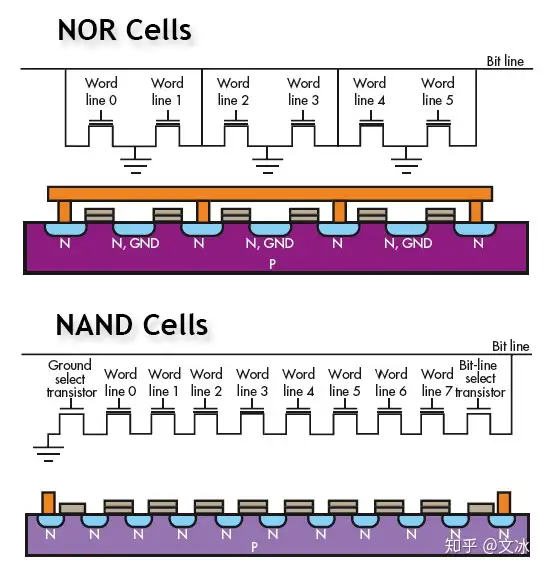

上篇介绍了单个器件的原理和构造,NOR和NAND的平面结构,我先放上来。可以图中看出

Fig. 6 NOR 与 NAND的平面结构

NOR 和 NAND的起名就来源于其结构,分别对应逻辑门电路中的NOR gate和NAND gate,

Fig. 7 NOR gate 和 NAND Gate

这里逻辑门电路,我的理解方法是从基本gate入手,OR Gate 是并联概念,AND gate 是串联概念,这刚好和其布尔逻辑对应,NOR是OR的非集,NAND 是AND的非集,在电路中他们的不同体现在输出端不同,OR gate还有AND gate的输出端在漏极(理解为后面),NOR gate以及NAND gate的输出端在源极(理解为前面)。再回想一下NOT gate, 这种非集 gate均有一个电阻,电阻是用来控制压降,同样地,NOR和NAND也有这样的电阻,靠近源极。当然非集电路也有其他方式控制压降的(CMOS或者同型沟道的耗尽模式),电阻只是其中一种形式。

通过结构上的对比,我们发现NOR flash上每一个浮栅晶体管都要接地,其存储密度就不如NAND。第一回合NAND获胜,KO!

4. 2 读取和写入

先来看读取,小眼睛先看看Fig.6,对于NOR flash, 每一个存储单元都是并联,所以为了读取某一个特定地址的存储状态就需要让其他单元处于关态,也就是说并联中其他存储单元的字线(控制栅)都要处于 ���� (低电压状态),这样是不是就变成我们之前讲述单个器件的情况(详见2.1),你只需要用大于 ��1 小于 ��0 的电压 ��′ 去尝试开启此存储单元,若这时电路被打开,则说明FET浮栅中未注入电子,表示‘1’,若没有打开,则说明存储单元浮栅中注入了电子,表示‘0’。

对于NAND flash, 每一个存储单元都是串联,所以为了读取某一个特定地址的存储状态,就需要让其他单元全部导通,也就是让其他单元的字线偏置大于 ��0 (高电压状态,因为不知道其他的存储单元是否都处于‘1’态,为了确保所有单元都导通,直接选择最大电压),这样就又回到一个存储单元的读取过程,是不是很巧妙?答案当然是,这就是人类的伟大之处。

读的方面,因为NOR的结构是并联的概念,每个器件基本上独立,指哪打哪,这个和CPU中取指操作一致,所以读的速度非常快,支持代码直接执行。而NAND就不一样了,因为串联的概念,你想读某一位置的数据,还需要把与其串联的其他单元打开,所以要先向芯片发送地址信息进行寻址才能开始读写数据,而它的地址信息包括块号、块内页号和页内字节号等部分,要顺序选择才能定位到要操作的字节;这样每进行一次数据访问需要经过三次寻址,至少要三个时钟周期。所以相比于NOR,其速度慢很多,KO!这一轮,NAND惜败。NOR的这种特性极好的满足了嵌入式存储应用场景。

写入过程就有点不一样,写入的过程就包含两个过程:

第一个过程就是擦除。这里插一句,NOR 和 NAND 都属于 flash EEPROM,根据Fig.1 中的分类,他们都没有字选择线,只能大块擦除。NOR 和NAND的擦除都是一样的,直接在所有字线上偏置负电压,把所有的存储状态变成‘1’,擦除过程就完成了(擦除过程原理都是F-N隧穿,因为源漏之间没有电压,就无法热电子注入了)。

第二个过程就是写入,现在全部都是‘1’态了,那么只需要在指定的地址写入‘0’即可,‘0’就是注入电子嘛,那么对于NOR flash来讲,因为并联的原因,每个存储单元都是独立的,在节线上偏置电压,也就是源漏之间偏置电压,对于想要注入电子的存储单元就可以将字线偏置正电压就行了。偏置正电压有两个作用,一是打开晶体管(这里都是NMOS为例),打开就会产生热电子,帮助热电子越过势垒进入到浮栅。不想注入的存储单元直接偏置 ���� 就行,没有打开自然就没有热电子,就不会注入了。

对于NAND来说就不一样了,这里不能使用热电子注入的方式,为什么?热电子注入要满足两个条件,一是通道打开,源漏之间要有电压,二是控制栅也就是字线需要加正偏压(这里虽可以满足),由于NAND是串联,这个时候你需要每个通道都打开,这太浪费电了,用爱发电?所以NAND的电子注入就需要使用F-N隧穿,直接偏置高的正压,指哪打哪。

两种注入方式有很大的差别,热电子注入模式工作电压较低,外围高压工艺的要求也较低,但它的编程电流很大,有较大的功耗,不利于应用在便携式电脑等有低功耗要求的产品上;隧穿入模式的功耗小,但要求有更高的编程电压(大概为20V左右),外围工艺和升压电路也就较为复杂。正是写入的方式有差别,所以速度上就有差别,没办法,NAND是F-N隧穿,时间明显小于NOR的热电子注入过程,所以写入速度,NAND获胜。

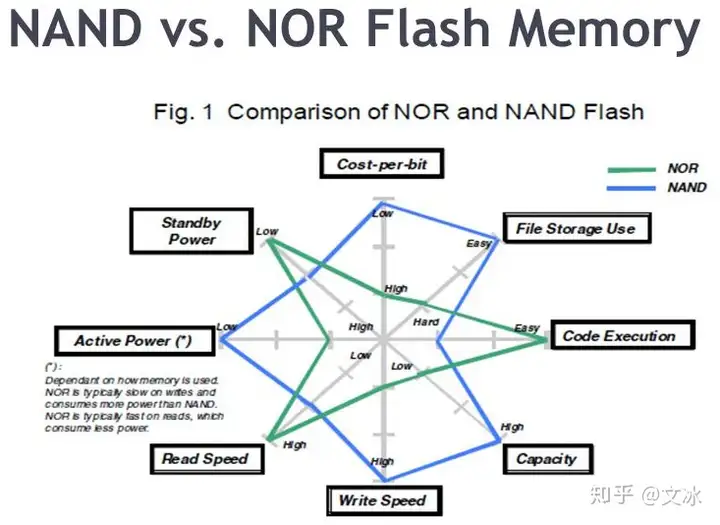

这个NOR和NAND的区别从原理上已经讲述完了,性能比较也很容易理解了,是时候祭出NOR和NAND的八芒星对比图:

Fig. 8 NAND vs. NOR flash Memory (Toshiba)

NAND密度比较高,工艺简单,所以成本低,其他的各项指标都可以从上面的原理推导出来,我就不一一赘述了。

5. SLC MLC TLC QLC

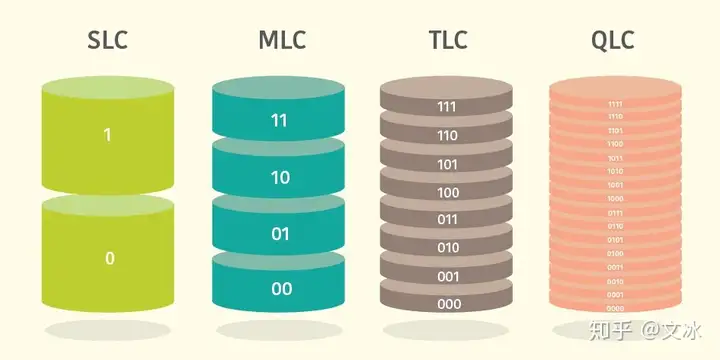

在NAND家族中,会有不同的颗粒说法,买SSD的同学比较清楚,哈哈。先把英文名写全,就知道个大概了:

SLC - Single level cell

MLC - Multi level cell

TLC - Triple level cell

QLC - Quad level cell

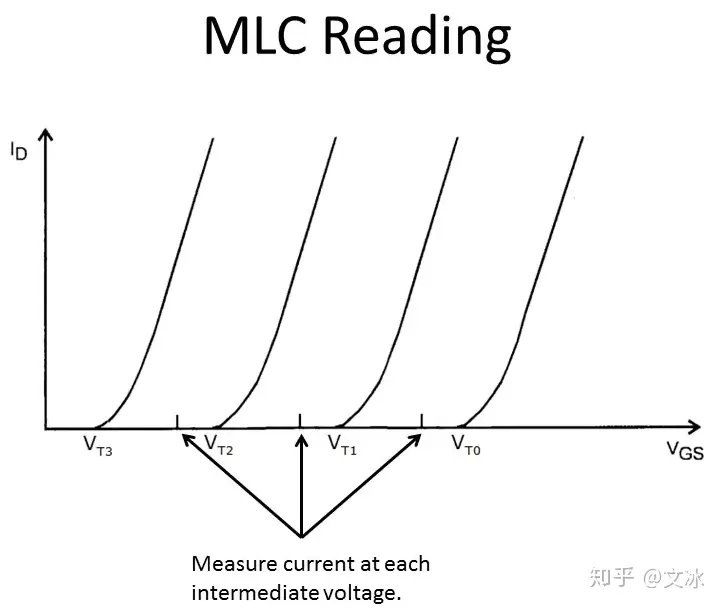

也就是1234嘛,这是什么含义呢?就是一个单元可以存储1个/2个/3个/4个bit数据,根据之前论述的原理,NAND是通过改变晶体管阈值电压从而实现存储控能,阈值电压由什么改变?浮栅电子数量对吧,如果浮栅电子只有‘空’和‘有’两种状态,就只能存储‘1’和‘0’,假定这两种状态是电子数目分别为0 和 100,如果我注入200 ,这个时候的阈值电压是不是就会变得更大,这是就多了一个态,注入300,又多一个,以此类推。

Fig. 9 MLC Reading

上图是MLC的读取示意图,因为注入的电子数量不同,阈值电压就不同,MLC表示可以存储2个bit数据,也就是说包含关态就有4个状态,分别表示‘00’‘01’‘10’‘11’,千万不要以为变成‘0’‘1’‘2’‘3’,目前计算机是读不懂‘1’以上的数字的。

Fig. 10 SLC MLC TLC QLC 数据存储情况

通过预先设定阈值电压与数据对应,MLC,TLC,QLC相比SLC来说,存储密度就更加大,但是有一个问题,就是容忍度,电子不能无限制的往上注入,这样功耗会比较大,所以一般采取的方法是在现有基础上,插入一些中间值。态与态之间的区分的根本是浮栅电子数量,态越多,对电子数量的精确度要求就越高,注入的时候一定要慎重注入。还有一个一个问题就是,存储容量确实变大了,但是由于每个单元存储的数据变多,其擦写频率就变高了,速度也会下降,擦写对介电层的破坏是不可逆的,寿命自然就短了,但是无奈MLC以上的颗粒存储数据密度更高,单位价格就便宜便宜,所以还是有很大市场的。这个其实就看需求了,一分钱一分货。

6. 3D NAND

上面我们介绍了NAND的基本原理与构造,其结构也就是基于平面结构,平面结构的NAND我们称之为2D NAND,在发展过程中,2D NAND不能无限制的平面延伸,来获取高存储密度,因此人们发明了3D NAND, 咱向上发展,因此就有了16 层, 32层,64层,128层3D NAND。其实就是建高楼大厦的概念。我找了一个LAM公司3D NAND 制造视频,有兴趣的可以看一下:3D NAND: Key process steps

3D NAND基本原理写到这里就结束了,下面是我撰写时查找的一些资料,图片还有一些词条都是来自goole和wikipedia,我只是一个知识的搬运工。

后面不定期更新半导体物理与器件方面的文章,任何问题,我们评论区交流学习!

以上图片均来自互联网,如有侵权,请告知!

参考文献:

2. How Flash Memory Works https://www.youtube.com/watch?v=s7JLXs5es7I

3. 刘恩科《半导体物理》第七版,电子工业出版社

4. WARM: Improving NAND Flash Memory Lifetime with Write-hotness Aware Retention Management