Calibre GUI PV 流程介绍(0.8um BCD Process )

Calibre规则名词解释

设计规则检查:Design Rule Check,DRC

版图 & 原理图一致性检查:Layout Versus Schematics,LVS

天线效应检查:Antenna effect,ANT

电学规则检查: Electrical Rule Checking,ERC

寄生参数提取 :Layout Parameter Extraction, LPE

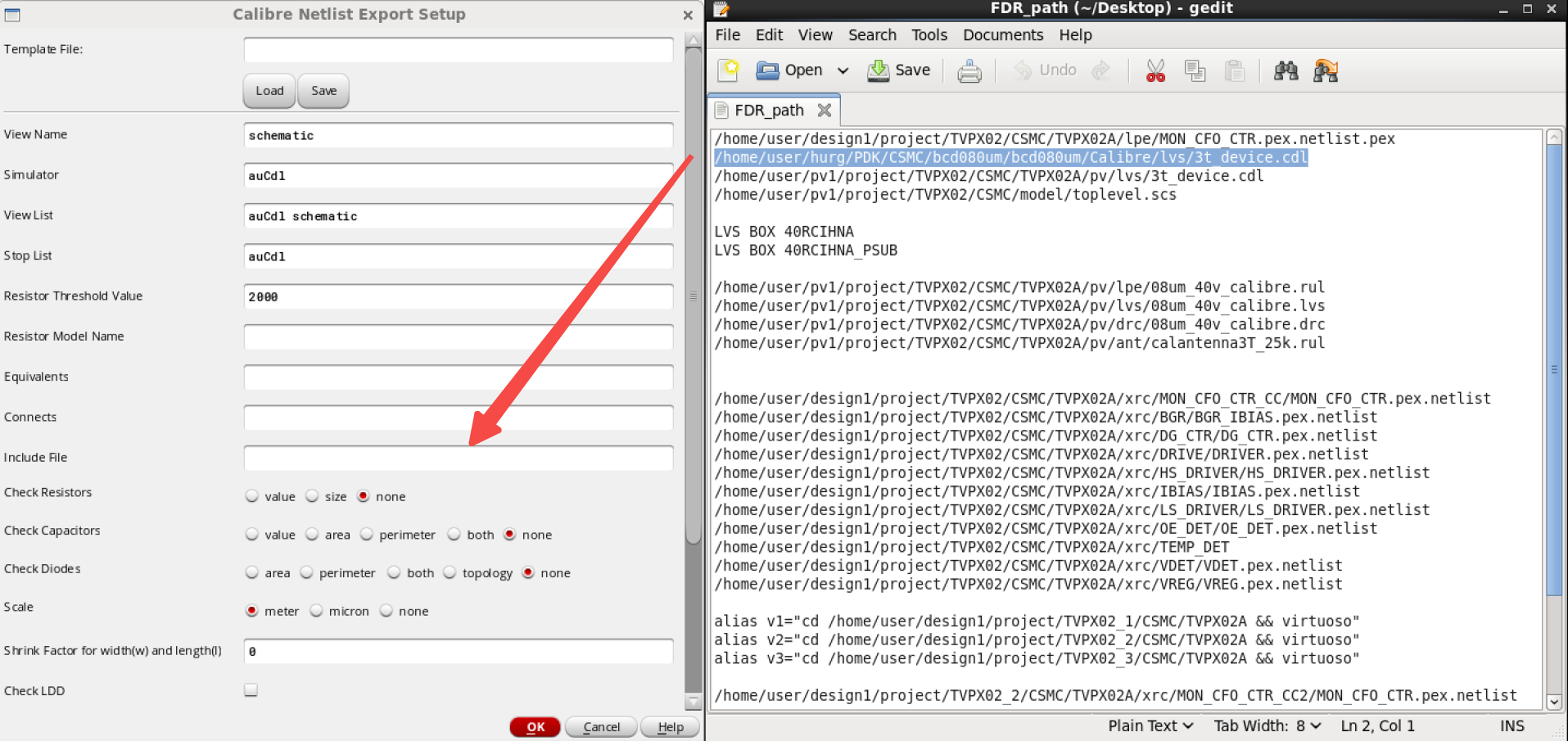

注意1:需要加的CDL文件

cdl器件文件放到网表的include file

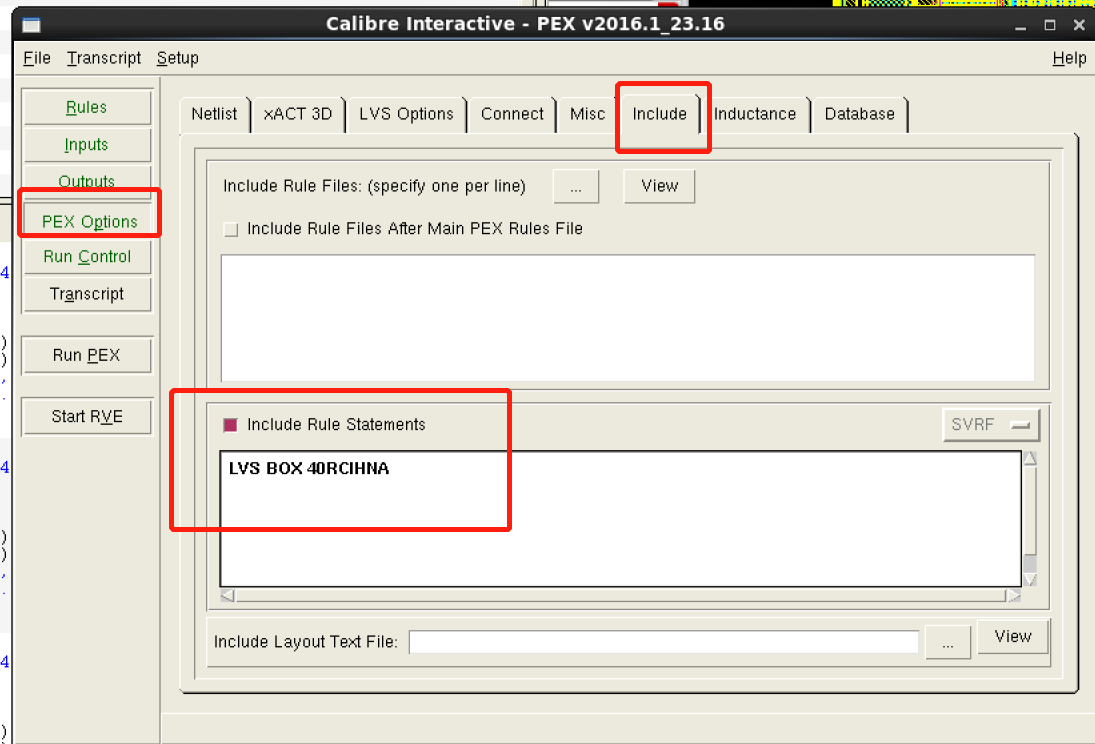

注意2:有些器件没模型需要加BOX规则

40RCIHNA的schematic只有pin,所以这个模块需要做LVS BOX 处理。

解决方法:

直接在pex的rule里加LVS BOX 40RCIHNA

pex option中直接添加 LVS BOX 40RCIHNA.如下:

Calibre GUI流程介绍

- PV文件位置,包括DRC/ANT/LVS/LPE

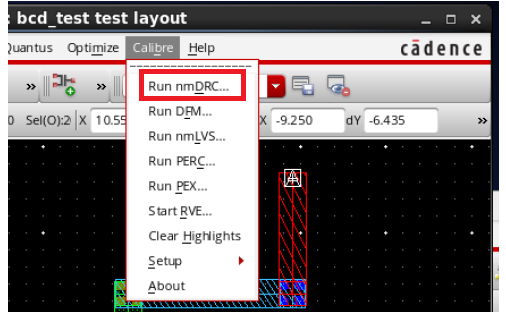

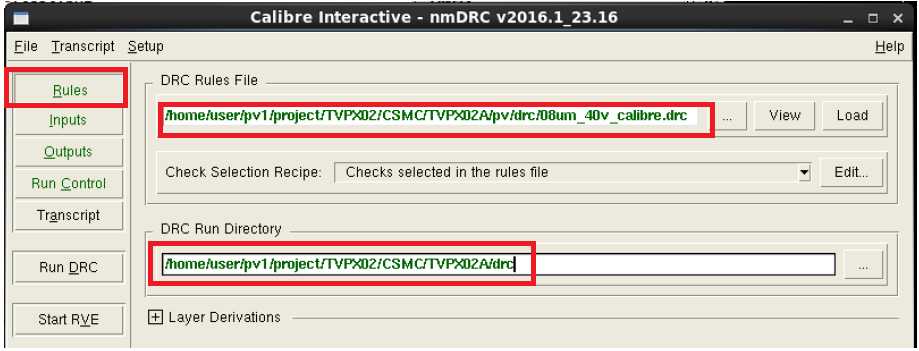

2. DRC流程介绍:

2.1 从版图窗口calibre->Run nmDRC调用DRC界面

2.2 在Rules Tab,输入正确的drc文件和命令运行路径。建议在单独的DRC目录下跑Job,方便文件查找和Debug。

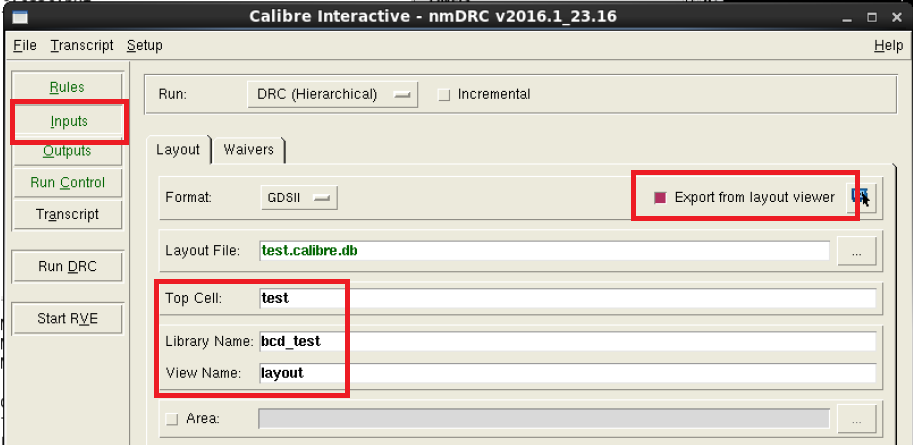

2.3 在Inputs Tab, 选择GDS从版图直接抽取,指定好正确的版图库名和CELL名称。如果数据没有更新,可以用原来的数据。

2.4 在Outputs Tab,选择输出DB的文件名称,DRC Job跑完后,自动直接打开RVE看结果

2.5 点击Run DRC Tab,系统会按照当前的环境设置,自动在后台运行DRC。对应的LOG和脚本产生在相应DRC目录下,方便Debug

3. ANT流程介绍:ANT流程设置和DRC完全一样

唯一区别在于rule 文件的路径和名称不同

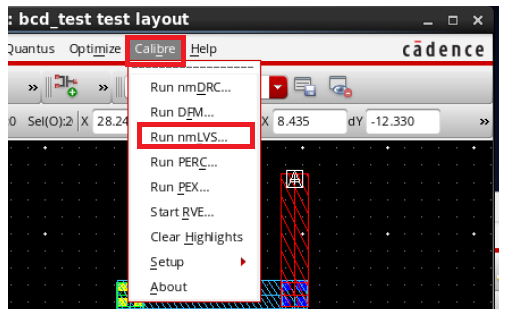

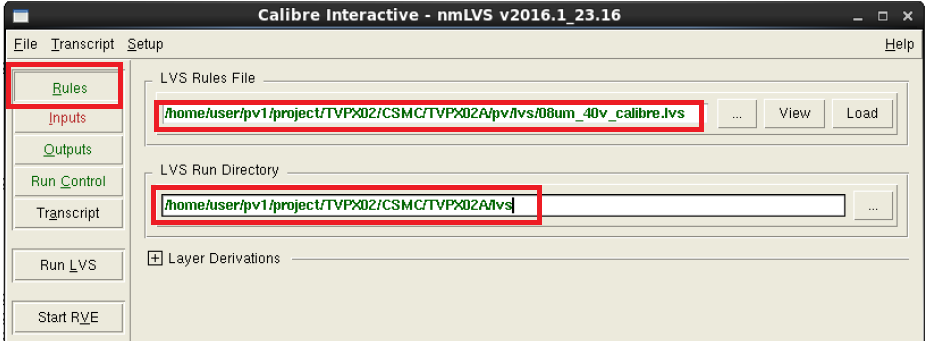

4. LVS流程介绍:

4.1 从版图窗口calibre->Run nmLVS调用LVS界面

4.2在Rules Tab,输入正确的lvs文件和命令运行路径。建议在单独的lvs目录下跑Job,方便文件查找和Debug

4.3在Inputs Tab, 选择GDS/CDL从版图/电路图直接抽取,指定好正确的版图/电路库名和CELL名称。如果数据没有更新,可以用原来的数据;

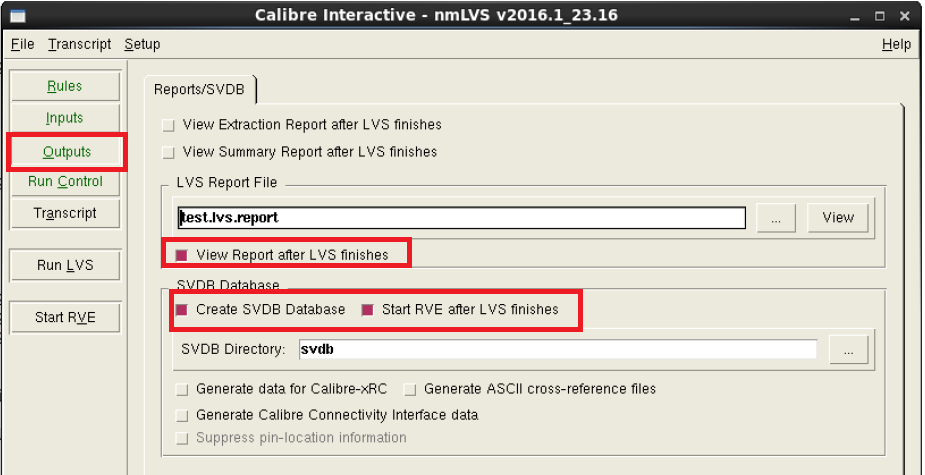

4.4在Outputs Tab,选择输出SVDB database,LVS Job跑完后,自动直接打开RVE看结果

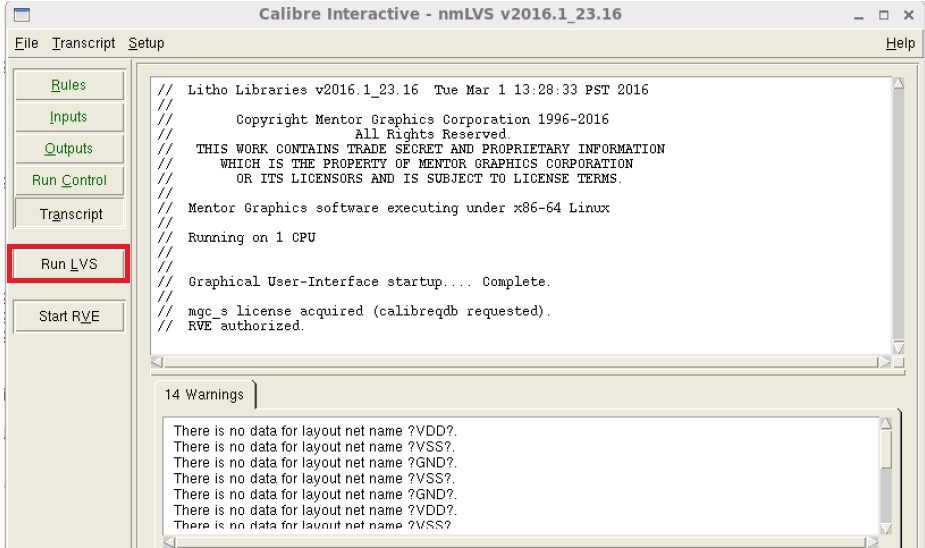

4.5点击Run LVS Tab,系统会按照当前的环境设置,自动在后台运行LVS。对应的LOG和脚本产生在相应LVS目录下,方便Debug

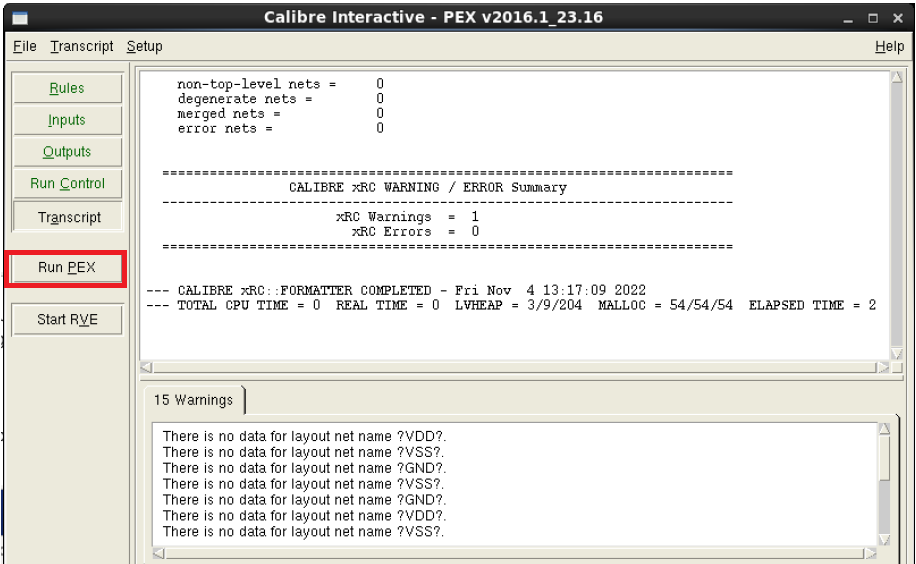

5. LPE流程介绍:

5.1从版图窗口calibre->Run PEX调用LPE界面

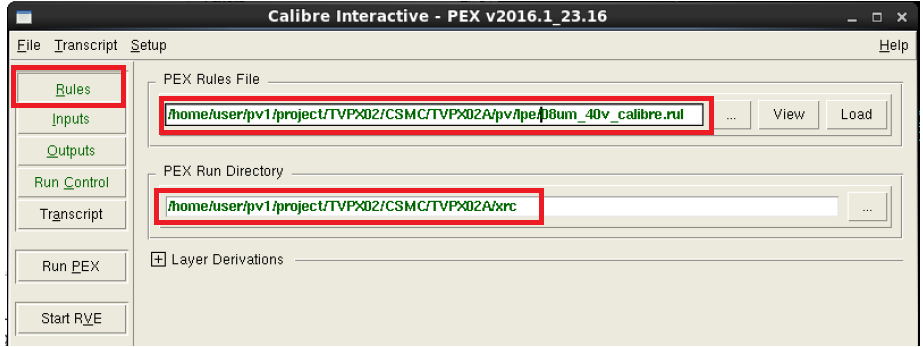

5.2在Rules Tab,输入正确的lpe rule文件和命令运行路径。建议在单独的xrc目录下跑Job,方便文件查找和Debug

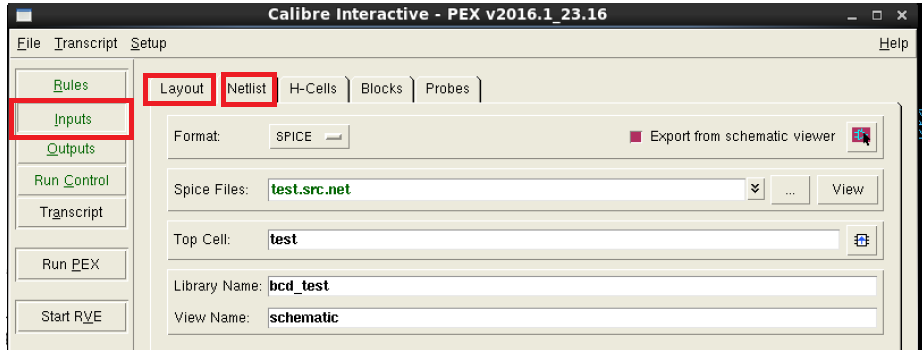

5.3在Inputs Tab, 选择GDS/CDL从版图/电路图直接抽取,指定好正确的版图/电路库名和CELL名称。如果数据没有更新,可以用原来的数据(和LVS设置类似);

5.4在Outputs Tab,选择抽取类型(rcc/rc/r/c…),输出寄生网表选择SPECTRE

5.5 点击Run PEX Tab,系统会按照当前的环境设置,自动在后台运行LPE。对应的LOG和脚本产生在相应xrc目录下,方便Debug

| Bash/home/user/design1/project/TVPX02/CSMC/TVPX02A/lpe/MON_CFO_CTR.pex.netlist.pex

/home/user/hurg/PDK/CSMC/bcd080um/bcd080um/Calibre/lvs/3t_device.cdl

/home/user/pv1/project/TVPX02/CSMC/TVPX02A/pv/lvs/3t_device.cdl

/home/user/pv1/project/TVPX02/CSMC/model/toplevel.scs

LVS BOX 40RCIHNA

LVS BOX 40RCIHNA_PSUB

/home/user/pv1/project/TVPX02/CSMC/TVPX02A/pv/lpe/08um_40v_calibre.rul

/home/user/pv1/project/TVPX02/CSMC/TVPX02A/pv/lvs/08um_40v_calibre.lvs

/home/user/pv1/project/TVPX02/CSMC/TVPX02A/pv/drc/08um_40v_calibre.drc

/home/user/pv1/project/TVPX02/CSMC/TVPX02A/pv/ant/calantenna3T_25k.rul

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/MON_CFO_CTR_CC/MON_CFO_CTR.pex.netlist

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/BGR/BGR_IBIAS.pex.netlist

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/DG_CTR/DG_CTR.pex.netlist

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/DRIVE/DRIVER.pex.netlist

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/HS_DRIVER/HS_DRIVER.pex.netlist

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/IBIAS/IBIAS.pex.netlist

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/LS_DRIVER/LS_DRIVER.pex.netlist

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/OE_DET/OE_DET.pex.netlist

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/TEMP_DET

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/VDET/VDET.pex.netlist

/home/user/design1/project/TVPX02/CSMC/TVPX02A/xrc/VREG/VREG.pex.netlist

alias v1="cd /home/user/design1/project/TVPX02_1/CSMC/TVPX02A && virtuoso"

alias v2="cd /home/user/design1/project/TVPX02_2/CSMC/TVPX02A && virtuoso"

alias v3="cd /home/user/design1/project/TVPX02_3/CSMC/TVPX02A && virtuoso"

/home/user/design1/project/TVPX02_2/CSMC/TVPX02A/xrc/MON_CFO_CTR_CC2/MON_CFO_CTR.pex.netlist

CC

/home/user/design2/project/TVPX02_2/CSMC/TVPX02A/xrc/TOP2_cc.pex.netlist

RCC

| /home/user/design2/project/TVPX02_2/CSMC/TVPX02A/xrc/TOP2.pex.netlist |

|---|