软件版本:VIVADO2021.1

操作系统:WIN10 64bit

硬件平台:适用XILINX A7/K7/Z7/ZU/KU系列FPGA

登录米联客(MiLianKe)FPGA社区-www.uisrc.com观看免费视频课程、在线答疑解惑!

1 概述

随着数字通信技术的进一步发展,各类数据的传输方案对带宽的需求迅猛增长,传统的并行总线的数据传输方式已经远远不能满足如万兆以太网、PCI-Express、SRIO、SFP等技术方案的需求,这个时候,促使高速串行数据开始被广泛地使用,Xilinx系列FPGA内部集成了能实现高速数据收的发串并/并串转换、预加重、接收均衡、CDR、8B/10B线路编解码、弹性buffer、通道绑定和时钟修正等模块,可极大地减小时钟扭曲、信号衰减和线路噪声对接收性能的影响,从而使传输速率进一步提高,可用于实现万兆以太网、PCI-Express、SRIO、SFP等常用接口。在内嵌高速串行接口技术的FPGA被大量应用的同时,高速串行的信号质量测试也变得越来越重要,通常用示波器观察信号波形、眼图、抖动来衡量信号的质量。串行信号的抖动,反映在时域上,信号的稳定时间会变小,眼图宽度会变窄;信号的噪声,反映在信号幅度上,眼图高度变小。通俗点讲眼图的眼睛张开得越大,越端正,表示高速串行数据传输的越稳定。

为了方便用户使用,vivado中提供了一个IBERT(Integrated Bit Error Ratio Tester)的测试工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。通过IBERT我们可以直接获取误码率,观察眼图,调节串行收发器的参数,从而有助于判断可能存在的问题,便于验证硬件的稳定性和信号完整性。

2 电路分析

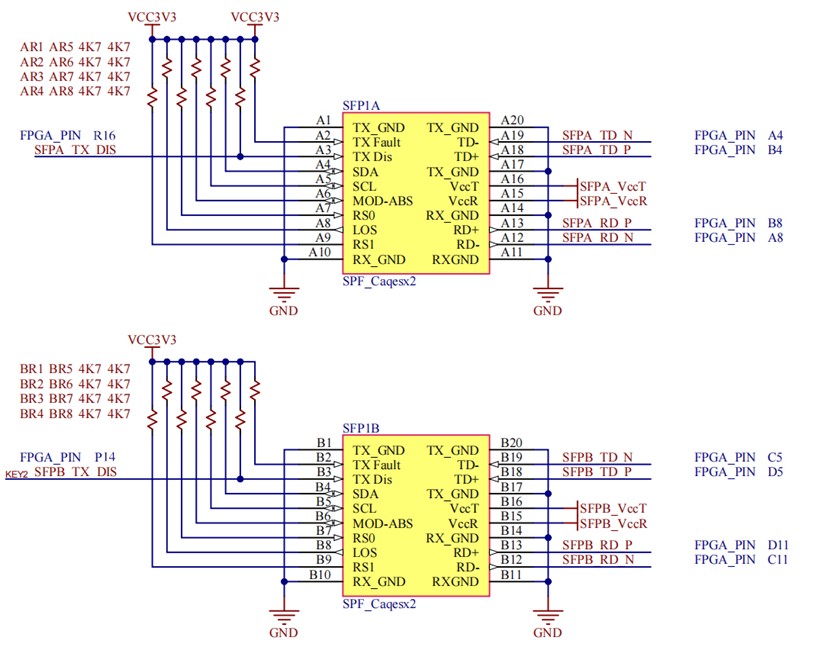

2.1 SFP+接口

F9开发板的 GTP的输入参考时钟125MHZ通过底板上的固定时钟获取。

2.2 测试工具

1)、万兆SFP+高速堆叠线缆(SFP-10G-DAC无源铜缆),传输距离0.5-7M

2)、万兆单模双芯LC-LC光纤线(3m)+万兆单模光模块,具体参数如下

3)、万兆多模双芯LC-LC光纤线(3m)+万兆多模光模块,具体参数如下

3 测试原理

IBERT中的BERT是Bit Error Ratio Test的缩写,指比特出错概率测试,简而言之就是误码率测试。Vivado中IBERT工具的测试原理是通过收发器由外部回环进行自收自发而实现。就是将同一组收发器的TX和RX进行短接,TX发送端通过发送某种特定序列的数据流,在RX接收端接收后,通过比对发送和接收的数据,从而得出误码率和眼图信息,来验证开发板GTP部分工作的稳定性和可靠性。

4 IBERT设置

在vivado的IP Catalog中找到IBERT 7 Series GTP这个IP核。

4.1 千兆1.25G速率

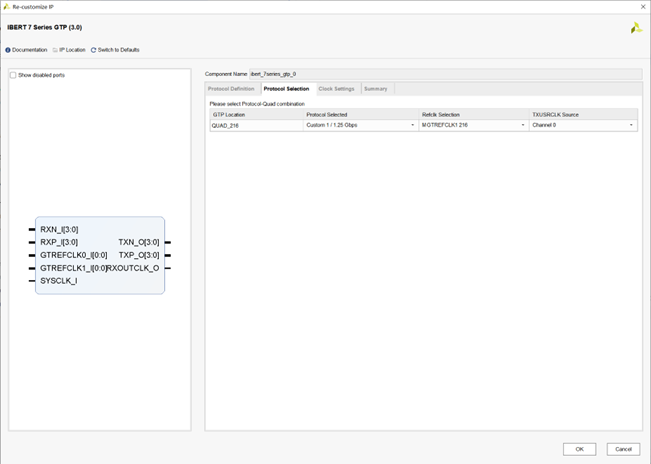

如下图所示,IBERT测试协议选择Custom1,GTP参考时钟频率选择125MHz,只需要测试与SFP连接的2对GTP,Quad Count选择1。传输速率设置为为1.25Gbps,PLL类型选择PLL0即可。

由于与SFP连接的GTP都位于BANK 216,所以在QUAD_216中选择使能协议。在F9-100T开发板中,从上面的硬件电路分析中可以看到,底板时钟芯片输出的差分时钟是与GTP_216_CLKP1连接,所以参考时钟要选择为MGTREFCLK1 216,下图所示。

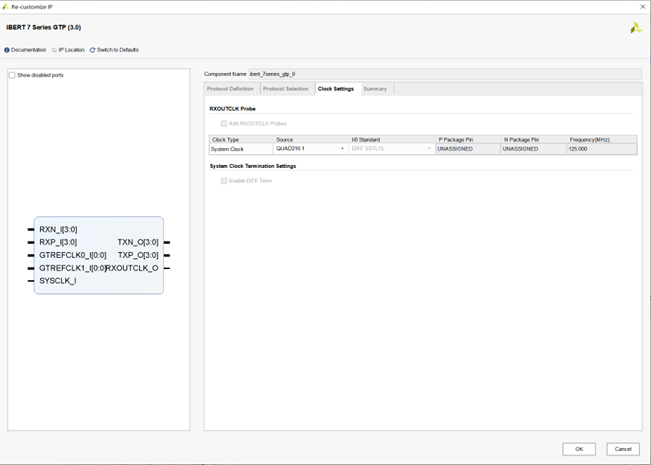

不妨将GTP输入的125MHz的时钟同时作为IBERT内部逻辑的工作时钟,这样就可以不使用额外的外部时钟,如下图所示。当然,用户也可以将该时钟设置为外部时钟,例如通过FPGA板卡的时钟晶振提供,大家可以自行尝试。

点击OK,完成IBERT IP核配置。

4.2 千兆6.25G速率

如下图所示,IBERT测试协议选择Custom1,GTP参考时钟频率选择125MHz,只需要测试与SFP连接的2对GTP,Quad Count选择1。传输速率设置为为1.25Gbps,PLL类型选择PLL0即可。

由于与SFP连接的GTP都位于BANK 216,所以在QUAD_216中选择使能协议。在MA703-35T开发板中,从上面的硬件电路分析中可以看到,底板时钟芯片输出的差分时钟是与GTP_216_CLKP1连接,所以参考时钟要选择为MGTREFCLK1 216,下图所示。

不妨将GTP输入的125MHz的时钟同时作为IBERT内部逻辑的工作时钟,这样就可以不使用额外的外部时钟,如下图所示。当然,用户也可以将该时钟设置为外部时钟,例如通过FPGA板卡的时钟晶振提供,大家可以自行尝试。

点击OK,完成IBERT IP核配置。

5 使用example design

IBERT的example design稍作修改就可以直接使用对GTP进行测试。

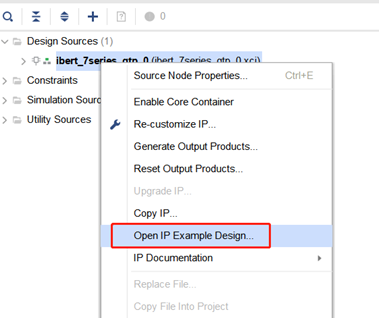

在IBERT IP核配置完成后,右击打开example design工程。

由于开发板的SFP屏蔽笼的tx_disable引脚都默认接了上拉电阻。要使收发回环测试可以正常进行,必须要将tx_disable引脚拉低。因此,在example design的顶层模块,添加2个sfp_tx_disable引脚,且均置为0即可。如下图所示。

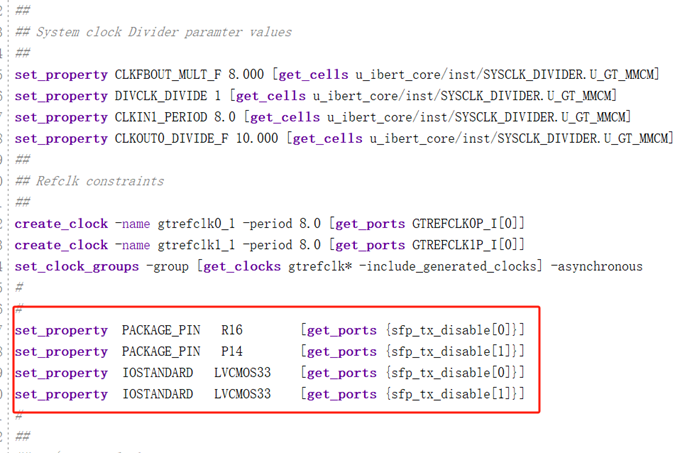

然后,在xdc文件中添加sfp_tx_disable引脚的约束即可,如下图所示。注意:不同的开发板管脚定义不一样

接着,编译工程,生成bit文件即可。1.25G和6.25G的example design修改方法相同。

6 硬件连线

ibert测试需要使用万兆光模块或者万兆电缆。使用单根万兆光纤或者万兆电缆形成回环,我们使用电缆将两个SFP+通道的TX和RX短接,或者使用光纤将光模块的TX和RX短接。

双通道回环

单通道回环

7 GTP IBERT测试

7.1 6.25G测试

测试6.25G,需要将 GTP的参考时钟提前设置为125MHZ(新版本已焊接固定时钟),设置完成后,给开发板上电,在vivado中打开hardware manager,将刚才生成的bit文件和ltx文件下载到开发板中。下载完成后,出现如下图所示的界面。

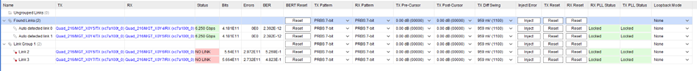

点击auto-detec links,出现如下图所示的界面。点击Reset按钮,使IBERT进行复位,可以看到此时的Errors变为0,代表接收端没有检测到错误。这里只显示出了当前所使用的GTP链路。其他没有建立收发环路的GTP并没有显示。

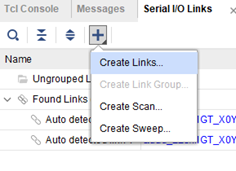

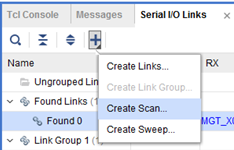

当然,用户也可以手动将其他没有连接的GTP加到当前的显示栏中,点击如下图所示按钮。

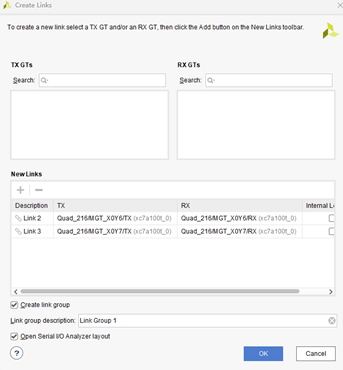

然后,将同1个GTP对应的TX和RX建立link,如下图所示。

添加完成后如下图所示。点击OK即可。

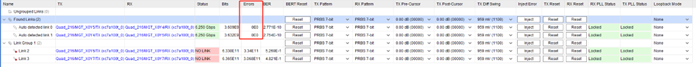

随后显示框中出现了这2对没有连接的GTP,状态显示为"No Link",如下图所示。

如下图所示,经过长时间测试,可以发现Errors一直为0,这代表,测试过程中没有出现任何误码,这说明板级层面的GTP硬件工作稳定。

当前测试使用的数据为7bit的伪随机序列。

在测试进行时用户也可以修改测试数据类型,例如PRBS 23-bit,PRBS 7-bit等等,接收与发送所使用的数据类型必须完全一致,修改完成后,务必点击Reset按钮,复位Errors为0。如下图所示。

误码率可以从数学统计的角度判断GTP的硬件稳定性,vivado还提供了一种更直观的方式来观察GTP的信号完整性,那就是眼图。首先,点击如下图所示按钮。

出现如下界面,所有设置保持默认即可,当然这边可以选择link的通道,然后点击OK。

此时vivado开始进行眼图扫描和生成,用户需要稍等片刻,等到Progress进度为100%时,眼图扫描过程便结束。

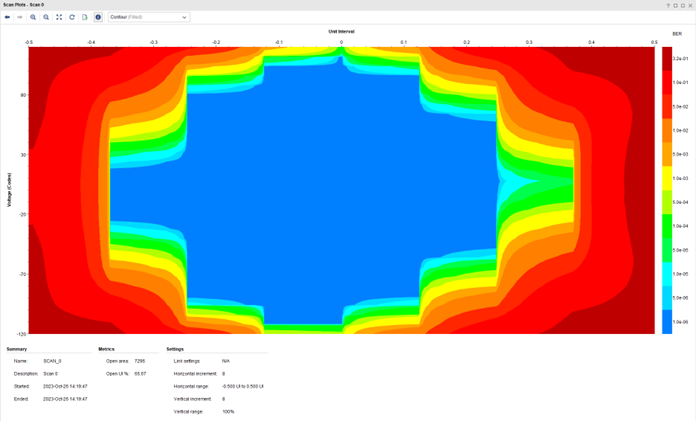

vivado生成的眼图如下图所示。

从信号完整性的角度来看,眼图中间的蓝色区域越大,GTP所对应的PCB高速电路的信号完整性越好。

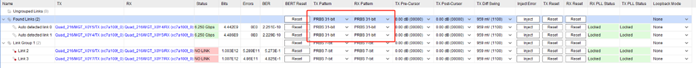

7.2 1.25G测试

测试步骤这边就不再赘述,下面给出对应的测试记录