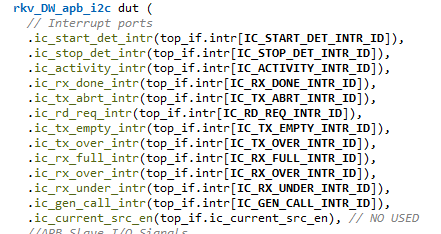

DUT中中断信号的连接

对应的参数定义

parameter IC_INTR_NUM = 12;

parameter IC_RX_OVER_INTR_ID = 0;

parameter IC_RX_UNDER_INTR_ID = 1;

parameter IC_TX_OVER_INTR_ID = 2;

parameter IC_TX_ABRT_INTR_ID = 3;

parameter IC_RX_DONE_INTR_ID = 4;

parameter IC_TX_EMPTY_INTR_ID = 5;

parameter IC_ACTIVITY_INTR_ID = 6;

parameter IC_STOP_DET_INTR_ID = 7;

parameter IC_START_DET_INTR_ID = 8;

parameter IC_RD_REQ_INTR_ID = 9;

parameter IC_RX_FULL_INTR_ID = 10;

parameter IC_GEN_CALL_INTR_ID = 11;

IC_INTR_MASK的默认值

M_RX_UNDER == 1;

M_RX_OVER == 1;

M_RX_FULL == 1;

M_TX_OVER == 1;

M_TX_EMPTY == 1;

M_RD_REQ == 1;

M_TX_ABRT == 1;

M_RX_DONE == 1;

M_ACTIVITY == 0;

M_STOP_DET == 0;

M_START_DET== 0;

M_GEN_CALL == 1;

M_RESTART_DET_read_only == 0;

//1 means interrupt is unmasked

//0 means interrupt is masked

中断屏蔽寄存器

中断屏蔽就是有选择地让中断系统不理睬某些中断源的中断请求,使这些中断信号暂时不被CPU“感觉”,但信号仍保留,以便条件允许时再响应。CPU可用指令将其置1或置0。置0时封闭该设备的中断请求触发器INTR,使其不能将中断请求IR发出。

中断响应的条件

每当一个指令周期结束后,若中断源有中断请求(中断请求标记INTR=1),且CPU允许接受中断请求(处于开中断,EINT=1),CPU就可响应中断请求,进入中断周期。

在I2C中默认不能发出中断请求的中断源为:M_ACTIVITY、M_STOP_DET、M_START_DET、M_RESTART_DET_read_only

I2C的test

1.寄存器测试