AXI传输总结

AXI这部分我没有深入解除过,只是多多少少摸一下看下数据路径有没有传过去,总感觉不到难点在哪里,不就是一个传输协议吗?

这个是soc设计方法与实现中提供的附录,可供参考,但是有版本错误(AXI4不支持写的交织,没有WID)

https://www.hxedu.com.cn/hxedu/w/inputVideo.do?qid=5a79a0187fd903cc01801cd94c353377

这里是版本差异说明:

https://zhuanlan.zhihu.com/p/193006656

AXI4协议去掉了WID信号,因此不再支持write interleaving。这是AXI4和AXI3的很重要和很大的一个改变。

Write interleaving的去除使得在WID信号上传递的信息是多余的。所有写入数据必须与相关的写入地址顺序相同,任何需要WID信息都可以从写入地址通道信号AWID中获得这些信息。

在AWID=0的数据还未发送完后,允许AWID=1的数据先发送;

这样带来的代价是发送端必须要缓存多个ID的wdata,不管是maser还是总线interconnection都必须要增加大量的缓存,所以增加了面积;

另外,Write interleaving增加了系统总线设计的复杂度,而且很容易造成死锁,所以虽然AXI3支持Write interleaving,但是大家在设计的时候,master基本都没支持Write interleaving。

所以AXI4就把Write interleaving的支持去掉了。

其实去掉了WID,应该是乱序也不支持了,都是顺序的了,但是outstanding应该还是有的,写通道可先写数据,后写地址也是可以有的。

https://blog.csdn.net/weixin_45270982/article/details/108888233

未完成状态、乱序、交织的说明

https://blog.csdn.net/qwaszx523/article/details/53737276

outsatanding是对地址而言,一次burst还没结束,就可以发送下一相地址。而out-of-order和interleaving则是相对于 transaction,out-of-order说的是发送transaction和接收的cmd之间的顺序没有关系,如先接到A的cmd,再接到B的cmd,则可以先发B的data,再发A的data;interleaving指的是A的data和B的data可以交错,如A1 B1 A2 B2 B3……

对于AXI master,先看写操作。如果分别发出WCMD1和WCMD2两个写命令给两个不同的slave,假设这两个写命令都是四拍的数据分别记为WDATA1_0,WDATA1_1,WDATA1_2,WDATA1_3,以及WDATA2_0,WDATA2_1,WDATA2_2,WDATA2_3。如果master在自己的写数据总线上,依次发出WDATA2_0,WDATA2_1,WDATA2_2,WDATA2_3,WDATA1_0,WDATA1_1,WDATA1_2,WDATA1_3,这就叫写out of order;如果master在自己的写数据总线上,依次发出WDATA2_0,WDATA1_0,WDATA2_1,WDATA1_1,WDATA2_2,WDATA2_3,WDATA1_2,WDATA1_3,这就叫写out of order且interleave;注意,不论是out of order还是interleave,同一个命令对应的四拍数据在内部必须是顺序的,不能乱序。比如,不允许出现WDATA2_1,WDATA1_0,WDATA2_0,WDATA1_1,WDATA2_2,WDATA2_3,WDATA1_2,WDATA1_3这样的。显然,你自己设计master时,如果是写操作,你不会主动发出out of oder和interleave的操作,因为这个明显增加了复杂度且没带来master自己的效率提高。再看master读,同样发出RCMD1和RCMD2两个读命令给不同的slave,由于不同slave的响应速度不同,就可能出现RCMD2对应的读数据先返回到master的情况;再考虑到复杂系统的总线设计,master依次接收到RDATA2_0,RDATA1_0,RDATA1_1,RDATA1_2,RDATA2_1,RDATA2_2,RDATA1_3,RDATA2_3这样的数据是有可能的,这就是读的out of order且interleave。所以,对于master,不建议发出out of order与interleave的写数据,但是必须支持out of order与interleave的读操作!同理,可以分析,对于slave,必须支持out of order与interleave的写操作,不建议返回out of order与interleave的读数据。在一个系统中,interleave会明显增加设计复杂度,其实可以约定master,slave以及连接总线都不要使用interleave,(另外可以配置depth ==1,达到不支持interleaving的目的)这样可以降低复杂度,但out of order是AXI特性,这个功能必须支持。

窄突发传输,非对齐传输

其实用用strob信号选通就行了,不知道为什么老是被人重视,很难吗?

当然,strob信号的宽度和size的宽度要有一个正确的对应关系。VIP会查这个的。

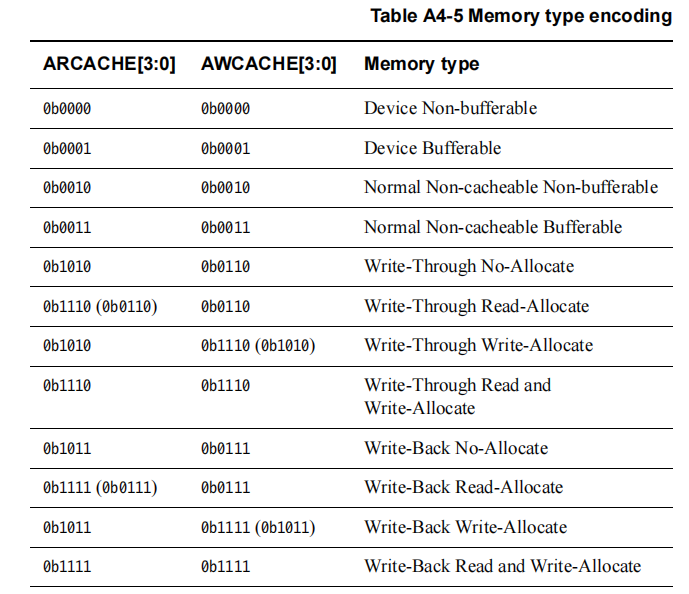

AXI的cache操作

cache操作的各种形式都只是建议,对于一个待测设计,我觉得首先是该设计到底支持那种的cache操作,然后再发送对应激励测试。

读下spec中关于Table A4-4 ARCACHE bit allocations和Table A4-3 AWCACHE bit allocations的部分,这些cache命令发出去,其实待测设计只是建议执行,如果不支持应该是不用实现的。

至于cacheable,我感觉是缓存数据用的,数据会驻留,而bufferable是一个队列性质的,相当于发送数据的时候,即便DUT没有完成操作,也可以提前发起完成响应,而后续空闲周期将buffer中的数据写入到目的地,(反正就是未完成也给一个完成的响应,或者用中途的数据给读返回等)。

会有很多组合,注意看spec是AXI3还是AXI4的,好像有区别。我这个是H版,0022H.c

页面置换算法(虚拟内存管理的软件层面)

页面置换算法,其实硬件也可以实现一部分,当然也要确认硬件设计的复杂度。

软件操作系统本身可以实现这些算法。

https://blog.csdn.net/Wang_Dou_Dou_/article/details/122127087

常用算法是:OPT算法、LRU算法、FIFO算法、NRU算法

https://github.com/DuHouAn/Java/blob/833386c371db15709d00ee2d0e065c466e53fc14/docs/OS/4_内存管理.md#内存管理

硬件上,LRU和NRU都有使用。

每个页面都有两个状态位:R 与 M,当页面被访问时设置页面的 R=1,当页面被修改时设置 M=1。其中 R 位会定时被清零。可以将页面分成以下四类:

R=0,M=0

R=0,M=1

R=1,M=0

R=1,M=1

当发生缺页中断时,NRU 算法随机地从类编号最小的非空类中挑选一个页面将它换出。

NRU 优先换出已经被修改的脏页面(R=0,M=1),而不是被频繁使用的干净页面(R=1,M=0)。

sv的不定态判定

造成不定态的原因有不少,比如直接赋值不定态,比如-xporp=tmerge或xmerge导致的不定态传播,比如多个输入并行驱动同一信号,再比如声明的reg从来没有被驱动。等等情况。

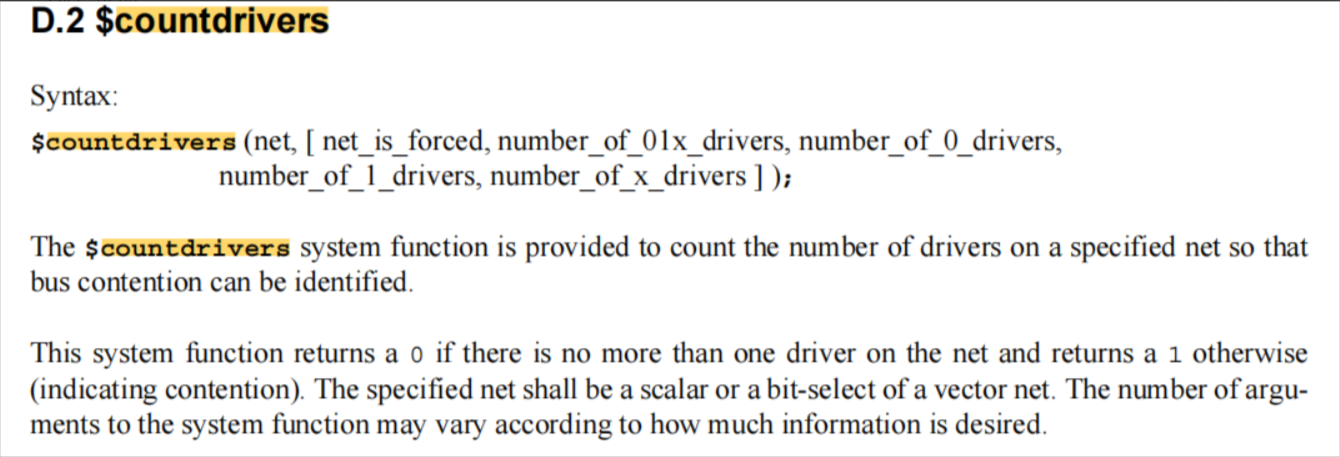

但是,一般只有多个输入并行驱动同一信号的情况,是非预期的行为,在判定不定态的时候,不少的开发者选择使用countdrivers函数,而不是unknown函数,确定不定态的断言。

该VPI接口函数countdrivers,传入net,如果没有多驱动,返回0,否则返回1。

verdi有时候打开一些文件是lib cell的问题

verdi的打开方式除了dbdir命令指定一个生成的结果(这种打开方式需要-kdb -lca的支持),

还是有其它方法,比如指定filelist(这种不需要-kdb -lca支持,但是好像有点慢,但是打开就有层次结构)。

不管如何,有时候最终一些文件的lib cell的形式,缺少了层次结构。

https://mp.weixin.qq.com/s/tAYijnsIMWo9wiOdQLkYWA

之所以确少,是verdi没有识别以下filelist的问题,如果都是文件而不是库的话,就不会有层次问题。

+incdir+./HDL/

-y ./HDL

+libext+.v

top.v

解决的方法是打开verdi时候添加-ssy -ssv选项

通过-y指定文件所在目录,+libext+.v指定文件后缀名。但是这种方法会导致Verdi加载filelist文件后不能显示hierarchy(层级结构)和V文件。为了解决这个问题,可以在命令行中增加-ssy和-ssv选项。

以下是命令行说明:

-ssv 不推荐自动标识在库文件(-v)的库模块作为库cell。

-ssy 不推荐自动标识在库目录(-y)的库模块作为库cell。

https://blog.csdn.net/m0_67393619/article/details/124777559

vcs的-v选项,会将某些文件解析成库。

加-v的log是“prasing library file”,不加-v的log是“parsing design file”

https://bbs.eetop.cn/thread-857774-1-1.html

环境变量的管理

https://blog.csdn.net/Michael177/article/details/121152904

一般就是操作PATH,但是直接操作PATH不够方便而且容易误操作。

使用linux中module工具。

module是一个专门管理环境变量的工具,全程是module environment,可以方便增加PATH,取消PATH,增补新的环境变量

设置module的环境变量,module查找这配置信息对应的文件夹

export MODULEPATH=/opt/modulefiles

文件编写

编写的位置可以是文件夹下新建一个文件夹下的文件。

#%Module1.0#####

conflict xxxxx

prepend-path PATH /usr/local/tools/modules/bin

基本使用

module avail

module list

module load

module unload