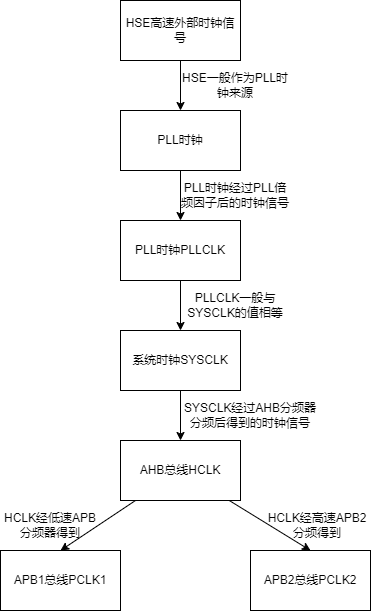

STM32的系统时钟大致可以分为以下流程

1.外部晶振提供HSE高速外部时钟信号

2.HSE经过PLL锁相环,倍频后得到PLL_CLK高速内部时钟信号

3.PLL_CLK经过分频后得到系统时钟SYSCLK

4.SYSCLK经过分频后得到APB1和APB2的时钟信号

如下图所示:

标准库代码如下(需要引用头文件“stm32f10x_rcc.h”,芯片不同,头文件也要更换):

void HSE_SetSysClock(uint32_t pllmul)

{

//__IO是c语言关键字volatile的重定义,防止这两个变量在读取过程中遭到修改导致的数据错误

__IO uint32_t StartUpCounter = 0,HSEStartUpStatus = 0;

//将RCC时钟树初始化为复位状态

RCC_DeInit();

//开启外部晶振

RCC_HSEConfig(RCC_HSE_ON);

//等待HSE稳定,该函数为阻塞式函数

HSEStartUpStatus = RCC_WaitForHSEStartUp();

//判断HSE是否稳定

if(HSEStartUpStatus == SUCCESS){

//设置PLL时钟来源为HSE,第一个参数表示使用HSE几分频,第二个参数表示PLL倍频倍数

RCC_PLLConfig(RCC_PLLSource_HSE_Div1,pllmul);

//AHB预分频因子设置为1分频,使HCLK = SYSCLK;若设置为2分频,则HCLK/2 = SYSCLK

RCC_HCLKConfig(RCC_SYSCLK_Div1);

//APB1预分频因子设置为2分频,使PCLK1 = HCLK/2

RCC_PCLK1Config(RCC_HCLK_Div2);

//APB2预分频因子设置为1分频,使PCLK2 = HCLK

RCC_PCLK2Config(RCC_HCLK_Div1);

//开启PLL

RCC_PLLCmd(ENABLE);

//等待PLL稳定,此函数为非阻塞式

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){

}

//切换SYSCLK时钟源为系统时钟

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

//读取时钟切换位状态,确保切换成功

while(RCC_GetSYSCLKSource() != 0x80){

}

}

else//此处放置初始化失败的程序

{

while(1)

{

}

}

}