在淘宝买了大西瓜的FPGA开发板,准备结合实物理解一下FPGA代码。为什么选择大西瓜呢,因为便宜。虽然闲鱼可能有更便宜的开发板,但我没有闲鱼的账号。

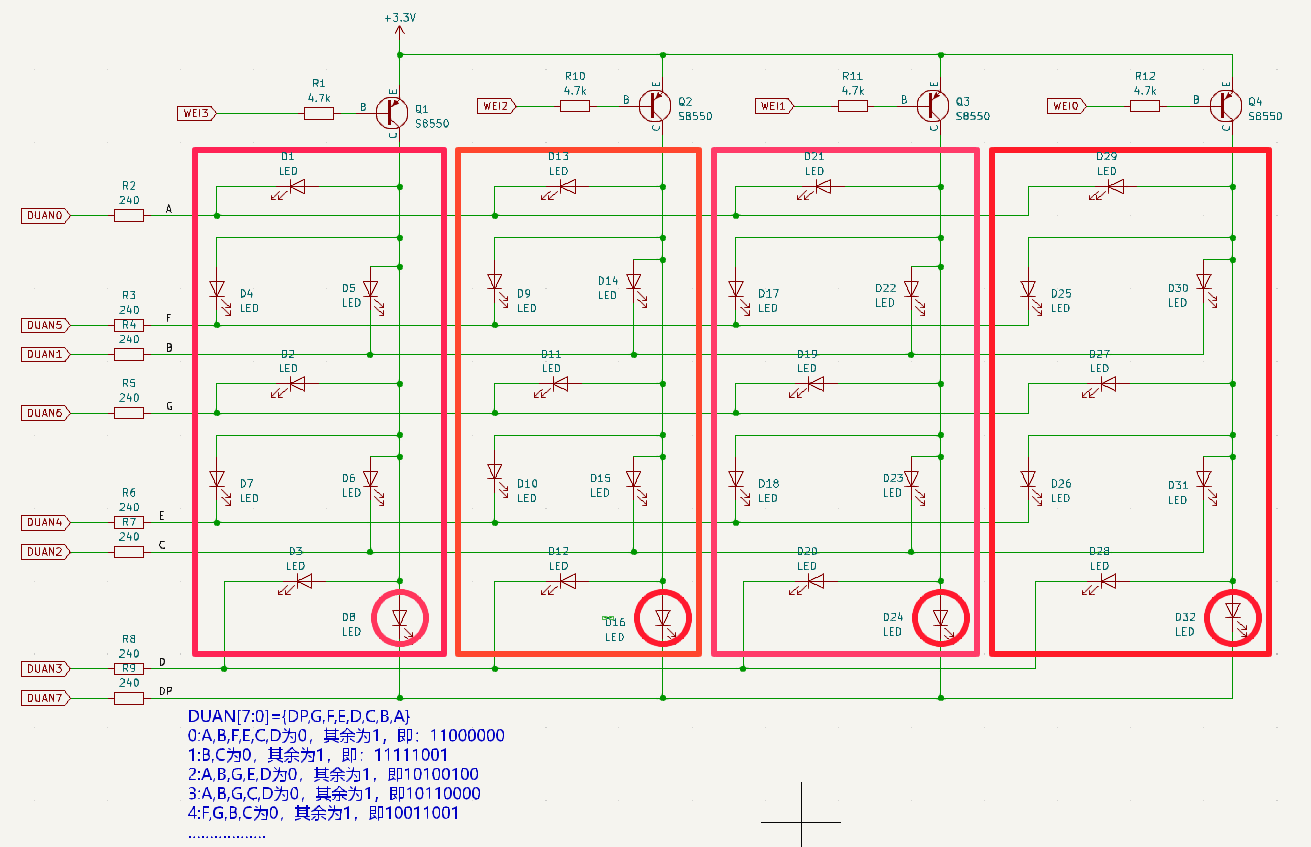

数码管部分的电路是这样的:

这对于强迫症来说,有点不太友好,正好因为不用说都知道的原因,需要练习一下KiCAD,就重画了一下,画完的效果如下:

我的强迫症不算严重,所以“段”的拼音我就没有修改,“位”的拼音也没有修改(改了还要改引脚的pin planner)。不过对应的Verilog代码我也做了一点小小的修改:

1 /********************************版权声明************************************** 2 ** 大西瓜团队 3 ** 4 **----------------------------文件信息-------------------------- 5 ** 文件名称: seg.v 6 ** 创建日期: 7 ** 功能描述:数码管的动态显示 8 ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com 9 ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. 10 **---------------------------修改文件的相关信息---------------- 11 ** 修改人: 你猜呢 12 ** 修改日期: 2023-05-27 13 ** 修改内容: 滚动显示0-9 14 *******************************************************************************/ 15 module seg 16 ( 17 input wire clk, //50MHZ时钟输入 18 output reg [3:0] wei, //wei:数码管位码,硬件上只有4位 19 output reg [7:0] duan //duan:数码管段码,‘0’led亮 20 ); 21 22 integer count;//分频计数器,每计数到50000下clk_1k时钟翻转 23 reg clk_1k;//数码管扫描时钟2000ms 24 reg [3:0] wei_count;//位码计数器 25 26 27 always @(posedge clk)//分频进程 28 begin 29 if(count==20000000) 30 begin 31 count=0; 32 clk_1k=~clk_1k; // 不再是1k了,50MHz时钟,计数20M次,400mS。 33 end 34 else 35 count=count+1; 36 end 37 38 always @(posedge clk_1k)//原本是数码管扫描进程,变成滚动显示0-9了 39 begin 40 case(wei_count) 41 // 第1位数码管亮,7段数字+1段小数点共8段全亮:dp g f e d c b a 42 4'b0000: begin wei=4'b1110; duan=8'b1100_0000;wei_count=wei_count+1'b1;end //0 43 4'b0001: begin wei=4'b1101; duan=8'b1111_1001;wei_count=wei_count+1'b1;end //1 44 4'b0010: begin wei=4'b1011; duan=8'b1010_0100;wei_count=wei_count+1'b1;end //2 45 4'b0011: begin wei=4'b0111; duan=8'b1011_0000;wei_count=wei_count+1'b1;end //3 46 4'b0100: begin wei=4'b0111; duan=8'b1001_1001;wei_count=wei_count+1'b1;end //4 47 4'b0101: begin wei=4'b1011; duan=8'b1001_0010;wei_count=wei_count+1'b1;end //5 48 4'b0110: begin wei=4'b1101; duan=8'b1000_0010;wei_count=wei_count+1'b1;end //6 49 4'b0111: begin wei=4'b1110; duan=8'b1111_1000;wei_count=wei_count+1'b1;end //7 50 4'b1000: begin wei=4'b1110; duan=8'b1000_0000;wei_count=wei_count+1'b1;end //8 51 4'b1001: begin wei=4'b1101; duan=8'b1001_1000;wei_count=wei_count+1'b1;end //9 52 default: begin wei=4'b0000; duan=8'b0111_1111;wei_count=wei_count+1'b1;end //. 53 endcase 54 if(wei_count > 10) wei_count = 4'b0000; 55 end 56 endmodule

看看Verilog,再看STIL,顺带重新温习一下数字电子技术基础,感觉对数字集成电路测试的理解更深了一些。很多概念从不同的角度去理解,会有不同的收获。大约十年前,我也学习过Verilog,但是因为不用,或者说很少用到,浅尝辄止。十年后,虽然还是不用,但是在测试过常见的数字芯片之后,再次学习Verilog,学习起来似乎轻松了很多。尤其是编写Testbench时,再结合实际测试数字电路的pattern去理解,很多当时只是知道How的事情,也渐渐的了解了Why。

顺便说一下,代码修改,是因为我们家的小朋友想看看显示0到9。

不惑之年,也只是不惑了技术,未曾不惑过人生。或者说,知道了好多的道理,很多事情还是不如意。勉励自己,做一个情绪稳定的人。