软件版本:vitis2021.1(vivado2021.1)

操作系统:WIN10 64bit

硬件平台:适用XILINX A7/K7/Z7/ZU/KU系列FPGA

登录"米联客"FPGA社区-www.uisrc.com视频课程、答疑解惑!

9.1概述

本方案使用自定义AXI4 IP FDMA 实现视频的采集和播放,关于FDMA的详细教程可以参考"米联客2024版FPGA数据缓存方案(PL-AXI-FDMA)"部分教程内容。

本方案实现了开发板HDMI视频采集后在PC上位机显示的功能。HDMI输入方案采用ADV7611,I2C的寄存器配置采用FPGA配置,已经封装成源码,方便大家使用。本方案的图片采集用到了XDMA的中断。

9.2系统构架

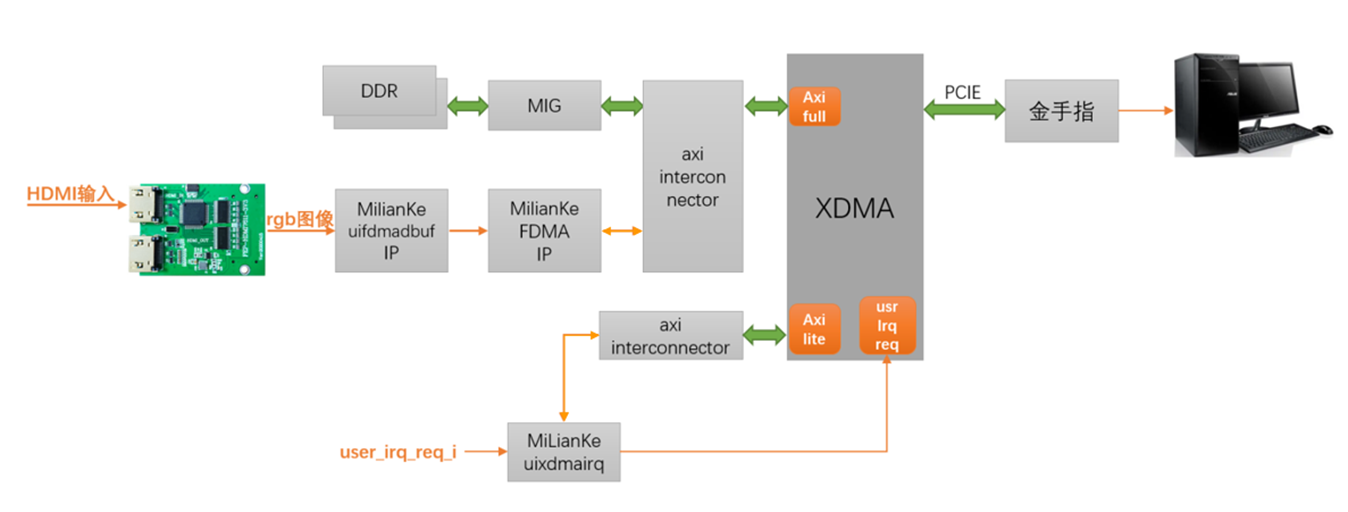

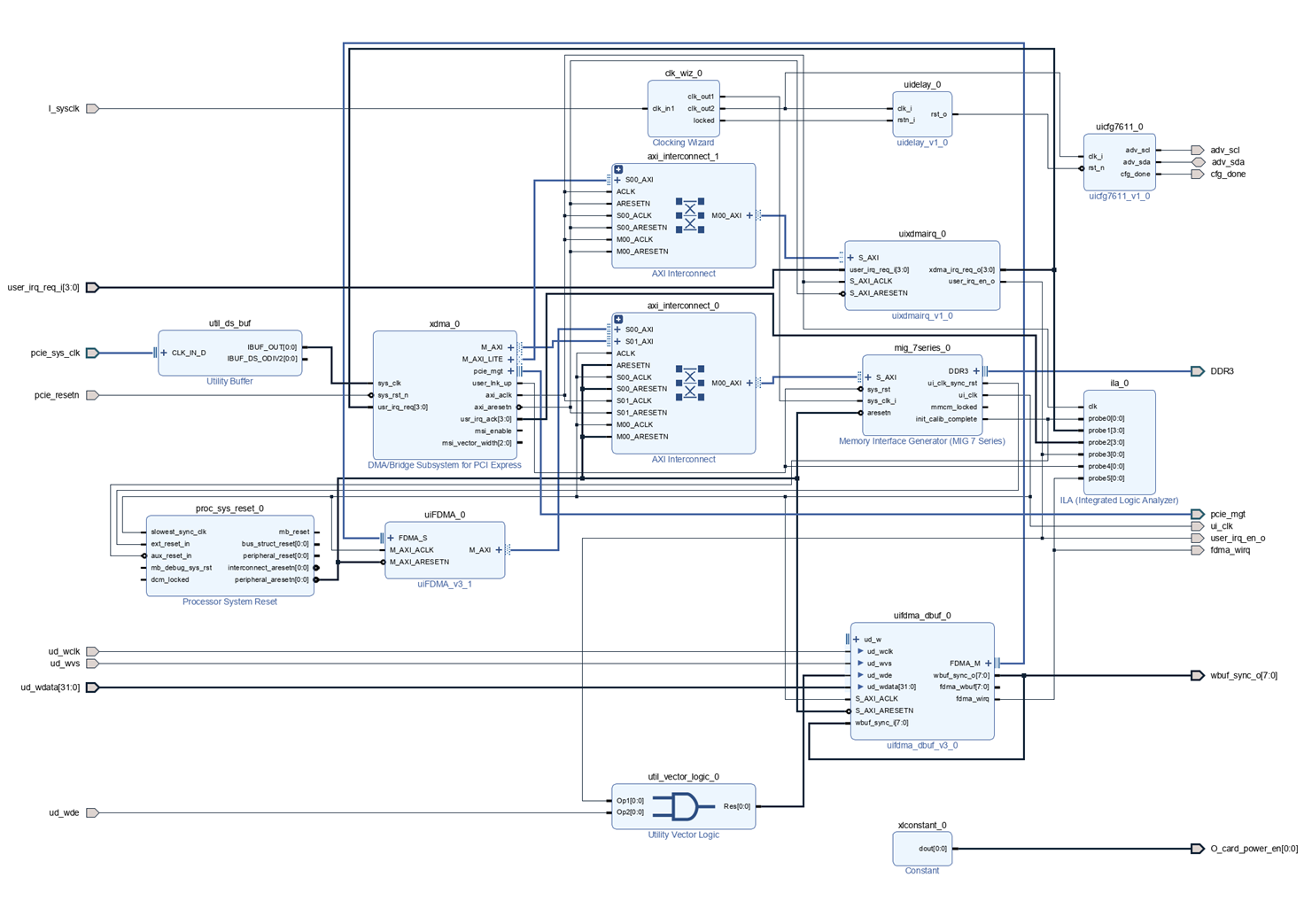

本系统HDMI输入方案采用ADV7611,I2C的寄存器配置采用Milianke uicfg7611 IP配置。通过Milianke uifdma_dbuf将数据写入DDR。PCIE上位机使用XDMA IP通过AXI Interconnect IP读取存放在DDR中的视频数据。

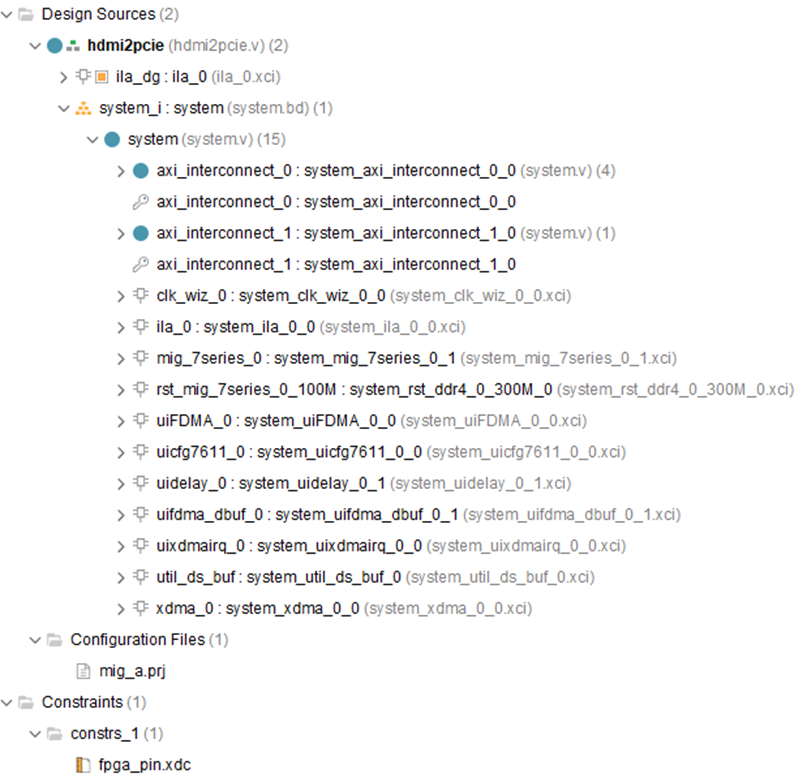

9.3FPGA工程

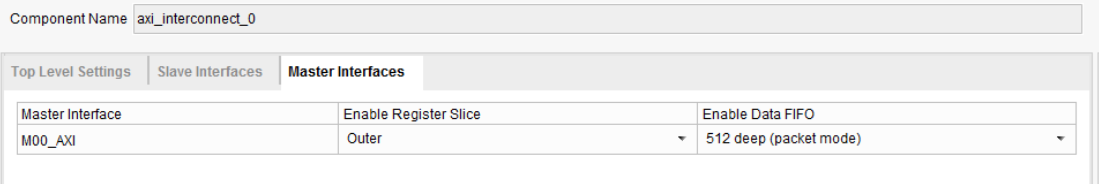

为了让AXI4总线效率最高,推荐进行如下设置

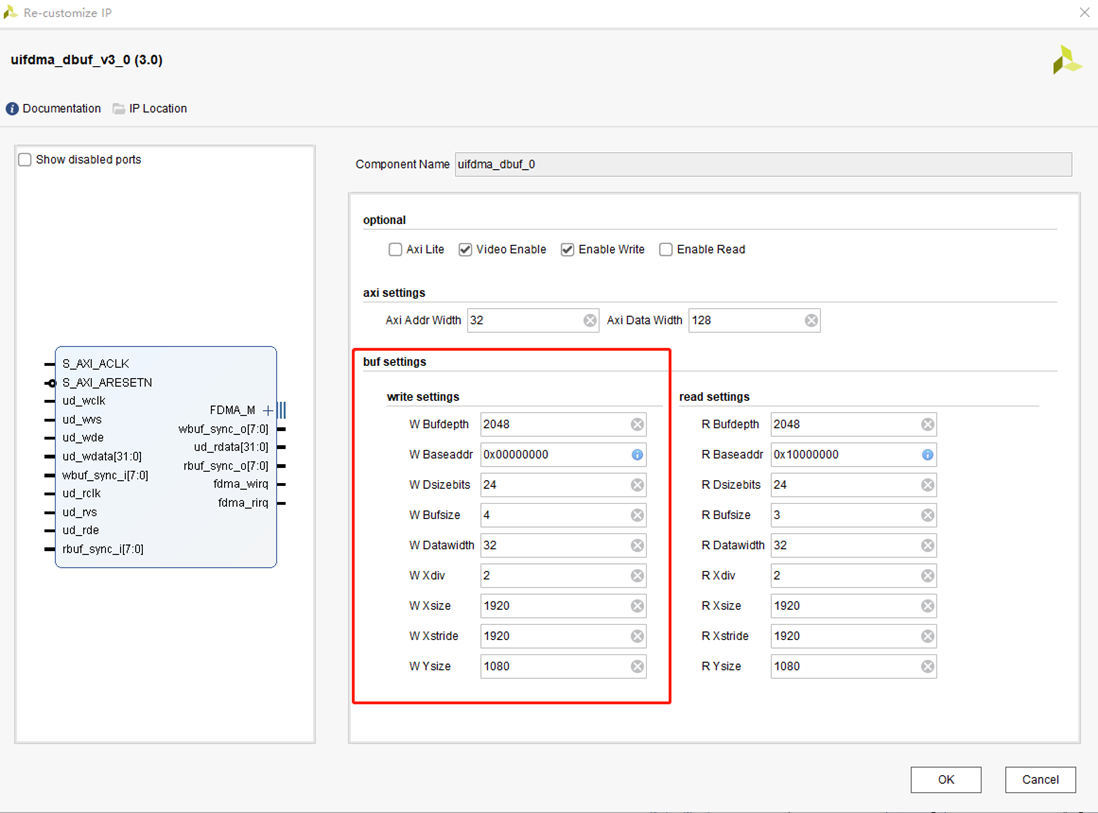

为了输出1920*1080的视频,还需要在模块调用中,设置缓存数量、视频视频分辨率等

uifdma_dbuf每完成一帧图像传输后会发出中断信号,为了让uixdmairq可以正确获取到中断请求,需要对中断做一些变换。

always @(posedge ui_clk)begin if(rstn_r3 == 1'b0)begin xdma_irq_req <= 8'd0; end else if((fdma_wirq_r == 1'b0 & fdma_wirq == 1'b1))begin xdma_irq_req <= 0; xdma_irq_req[rbuf_sync_o[7:0]] <= 1'b1; end end |

9.4上位机程序设计

设置分辨率为1920*1080,视频输入是60FPS,上位机中断也是60FPS但是QT的显示效率较低,以60FPS的中断去显示,会卡死,所以上位机只处理一半的中断,图像输出30FPS。

9.5硬件安装

注意先下载程序,调试阶段下载bit文件,然后再开电脑。这样才能正确识别和后续测试工作正常开展。对于部分没有HDMI输入的开发板需要使用HDMI输入卡完成此实验。

9.6实验结果

开发板的HDMI输入接口插入HDMI视频源(一般为显卡输出),右边屏幕为QT上位机显示采集的HDMI输入图像。