一、低功耗背景

在芯片设计中,常常提到PPA平衡,即POWER(功耗)、PERFORMANCE(性能,也叫速度)、AREA(面积)

而近年来随着移动电子设备的普及,功耗在评价芯片优劣时所占的比重越来越高,低功耗的设计也成为了许多芯片设计的必经之路。

低功耗设计的动机主要有以下几点:

- 功耗过大导致芯片寿命降低;

- 芯片散热成本增加;

- 芯片的可靠性和电路时序会受到影响;

- 电源网格设计难度增加;

- 产品竞争力降低。

二、芯片中功耗的种类

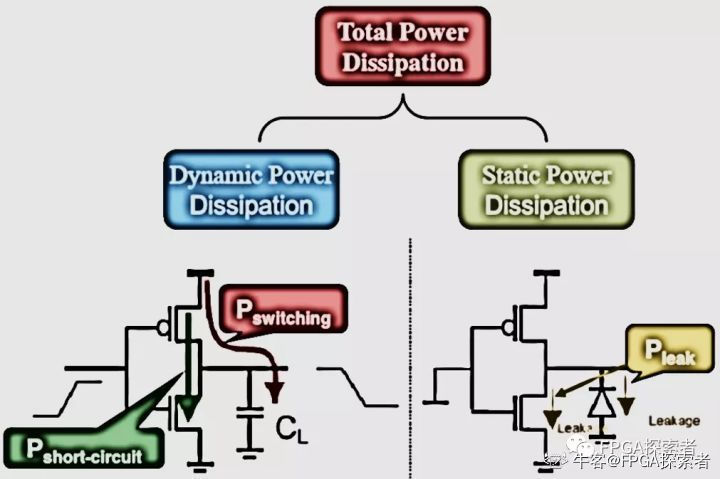

芯片中的功耗=静态功耗+动态功耗=静态功耗+开关功耗+短路功耗

其中,动态功耗占到电路功耗的80%左右,接下来将逐一介绍每一个功耗:

1.静态功耗

静态功耗是指芯片在待机(静态)时所产生的功率消耗,来源于mos管内部的泄漏电流,泄漏电流主要由以下四个部分组成:

IDS:亚阈值电流,mos管在还未导通时,在n+(源)-p(体)-n+(漏)之间形成了一个寄生的双极性晶体管。

Igate:栅氧化层隧穿电流,由于栅极氧化物隧穿和热载流子注入,从栅极直接通过氧化物流到衬底的电流。

Ireverse:反偏二极管电流,由少数载流子漂移和在耗尽区产生电子/空穴对引起。

IGIDL:漏极泄漏电流,在稳定工作状态下,总会有泄露电流流过位于晶体管源(或漏)与衬底之间的反相偏置的二极管结。

因此,静态功耗的计算公式为:

其中Ipeak为泄漏电流,是上述四种电流的加和。

2.动态功耗

动态功耗是由于负载电容在充电和放电期间,门电路输出切换时,逻辑转换所引起的功耗,具体可分为开关功耗和短路功耗。

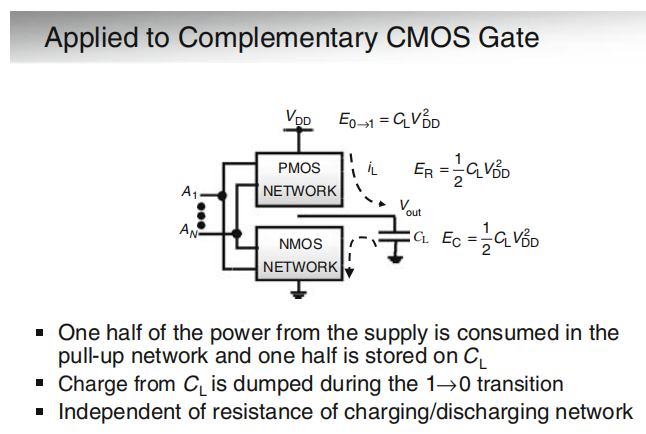

开关功耗是指coms电路输出发生翻转时对负载电容的充放电时所消耗的功耗。负载电容包括net电容和gate电容。

例如在一个反相器电路中,输出从低到高过程中,电源提供了CLVDD2的能量,通过积分运算,一半的能量被上拉pmos管所消耗,另一半能量1/2CLVDD2存储在电容中;在输出由高到低的过程中,电容放电,其存储的能量被消耗在nmos管中。并且,前后两个过程消耗的能量和mos管的本身的尺寸没有关系。

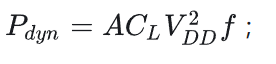

因此,在每一个开关周期(包括0->1和1->0两个过程),需要固定的能量 CLVDD2 ,结合器件的开关频率和面积,我们可以得出开关功耗为:

其中,A为电路翻转活动因子;CL为电路负载电荷和固有电容;f为电路的工作频率;VDD为供电电压。

时钟的A=1是因为每个周期都要上升和下降一次,而数据每个周期仅传输一次,所以数据的最大能量跃迁活动因子A=0.5。

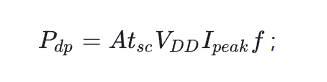

短路功耗是因为在输入信号进行翻转时,信号的翻转不可能瞬时完成,因此PMOS和NMOS不可能总是一个截止另外一个导通,总有那么一段时间是使PMOS和NMOS同时导通,那么从电源VDD到地VSS之间就有了通路,就形成了短路电流。

反相器输出电压曲线图

反相器输出电流曲线图

输入电压变化时短路电流变化图

根据以上几幅图可以看出,NMOS在Vin > VTnmos后开始导通;而PMOS在电压达到VDD – VTpmos之前一直导通,在VTnmos和VTpmos这段时间内PMOS和NMOS同时导通,此时就产生了短路电流;并且在输入电压达到1/2VDD时具有最大的短路电流。

短路功耗的计算公式如下:

其中tsc为短路时长,Ipeak为总的短路电流。

由于传输中短路持续的时间特别短,短路功耗相比开关功耗来说小很多。所以一般情况下会忽略短路功耗,把开关功耗就当作动态功耗。

资料参考:

[1]《低功耗设计精解》,Jan Rabaey

[2](数字IC)低功耗设计入门(一)——低功耗设计目的与功耗的类型 - IC_learner - 博客园 (cnblogs.com)

[4]FPGA数字IC笔试面试016—低功耗设计/静态/动态功耗_牛客网 (nowcoder.com)

[5]https://mp.weixin.qq.com/s/VxyXSDhW20EWNJXKrPazLw