本文记录自己在学习蜂鸟E203的过程。下面简单介绍一下仿真之路所遇到的困难和走过的坑。

1、环境开发 :一般选择ubuntu 18.04 这个版本,安装这个教程很多,可以自行学习。

2、在Linux中安装工具:

sudo apt-get install autoconf automake autotools-dev curl device-tree-compiler libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison flex texinfo gperf libtool patchutils bc zlib1g-dev git

3、下载 e203_hbirdv2 project 选择其中一种即可。

git clone https://github.com/riscv-mcu/e203_hbirdv2.git git clone https://gitee.com/riscv-mcu/e203_hbirdv2.git

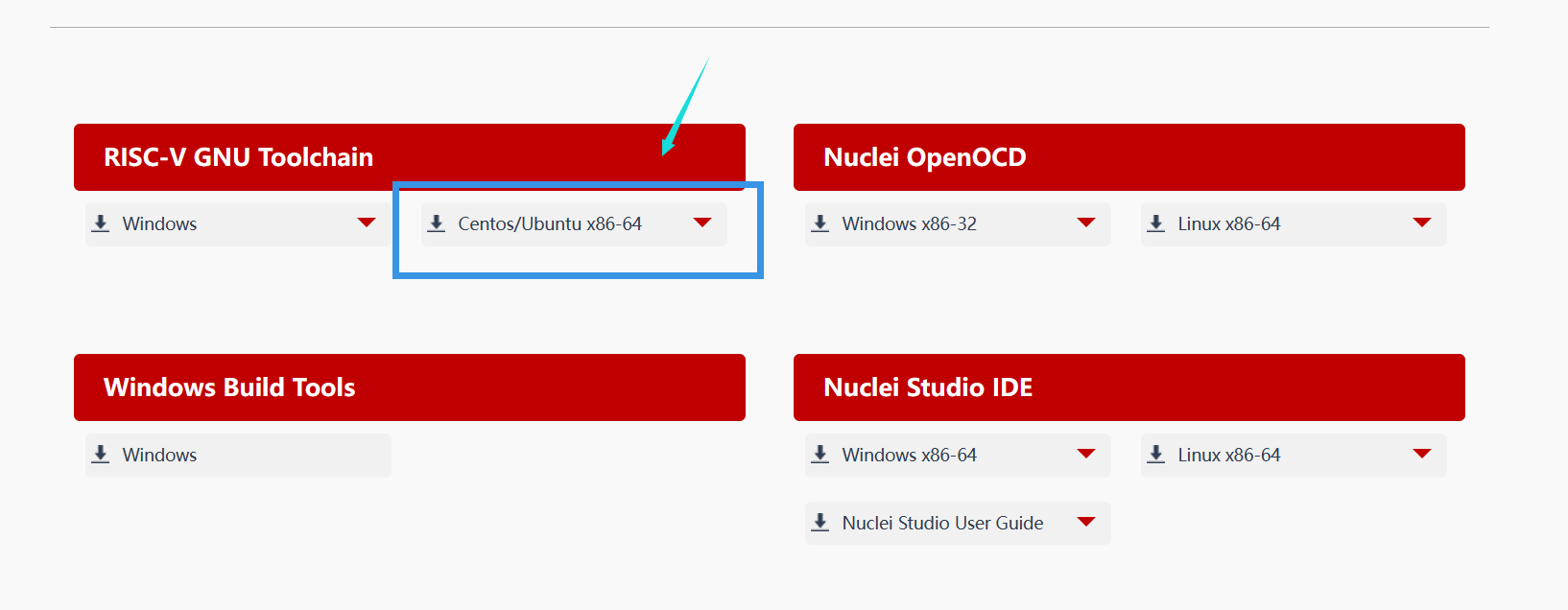

4、编译工程自带例程 ,下载芯来的工具链

芯来工具链官网:芯来工具链_专业RISC-V处理器IP及解决方案公司 (nucleisys.com)

下载好 RISC-V GNC toolchain 后,可以将压缩包直接拖进虚拟机中。可以看到如下:

接下开始配置riscv- tests。打开终端,在终端中操作如下命令:

cp nuclei_riscv_newlibc_prebuilt_linux64_2022.12.tar.bz2 ~/ cd ~/ tar -xjvf nuclei_riscv_newlibc_prebuilt_linux64_2022.12.tar.bz2 cd <your_e203_dir>/ mkdir -p ./riscv-tools/prebuilt_tools/prefix/bin cd ./riscv-tools/prebuilt_tools/prefix/bin/ ln -s ~/gcc/bin/* .

其中 两个地方需要注意:

nuclei_riscv_newlibc_prebuilt_linux64_2022.12.tar.bz2 这里是根据自己下载的工具版本而定。

your_e203_dir 是自己的E203存放目录。

注意最后一步有的是这样的命令:

ln -s ~/nuclei_riscv_newlibc_prebuilt_linux64_2022.12.tar.bz2/gcc/bin/\* .

完成之后,开始编译测试:

cd <your_e203_dir>/riscv-tools/riscv-tests/isa

source regen.sh

完成之后,进行跑仿真,需要安装两个软件 iverilog+gtkwave 或者 VCS+Verdi 。这里我们以iverilog+gtkwave 为说明。

注意:如果要使用iverilog为仿真工具,确保这个工具版本为12.0。

安装 iverilog 和gtkwave 命令如下:

# 从github下载 git clone https://github.com/steveicarus/iverilog.git #进入iverilog目录 cd iverilog #检测依赖文件、配置环境并编译 sh autoconf.sh ./configure make #运行测试demo检查是否编译成功 make check #安装iverilog sudo make install #查看iverilog的版本 iverilog –v #安装波形查看工具 sudo apt-get install gtkwave

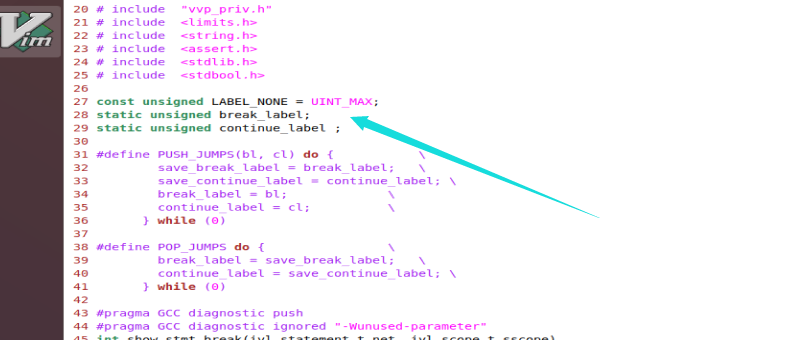

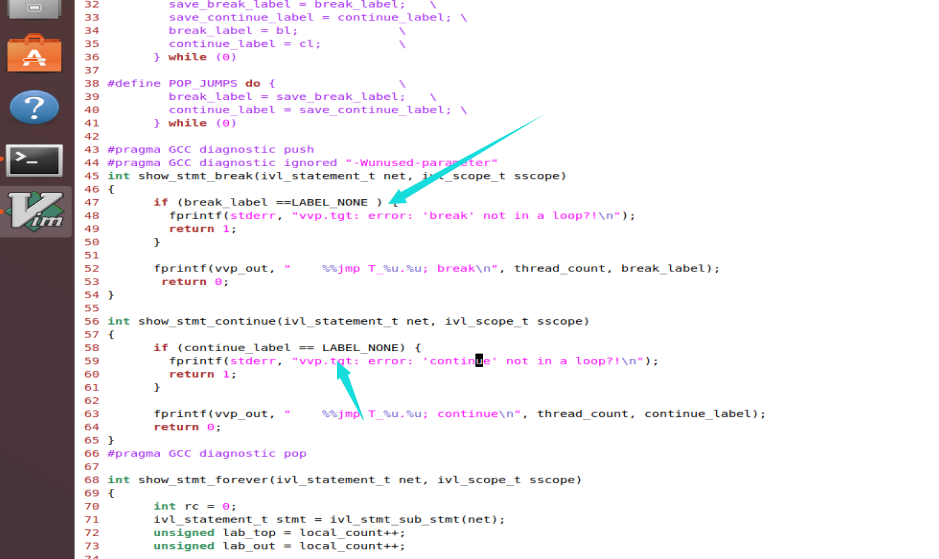

注意:安装iverilog12.0时vvp_proc_loops.c:28:31: error: initializer element is not constant static unsigned break_label = LABEL_NONE?这里会报错!

解决方案:找到这个c文件把这两个信号声明后面的“= LABEL_NONE”去掉,在之后的两个int()块里面再分别加上= LABEL_NONE赋值就行。

#找到该文件 cd ~/iverilog/tgt-vvp

#使用vim或者gvim 打开该文件 并修改。保存

gvim vvp_proc_loops.c

在安装好iverilog 和gtkwave 后,我们开始综合网表。

# cd ~/e203_hbirdv2/vsim 进入自己文件存放位置

cd ~/<your_e203_dir>/vsim

make clean

make install

make compile SIM=iverilog

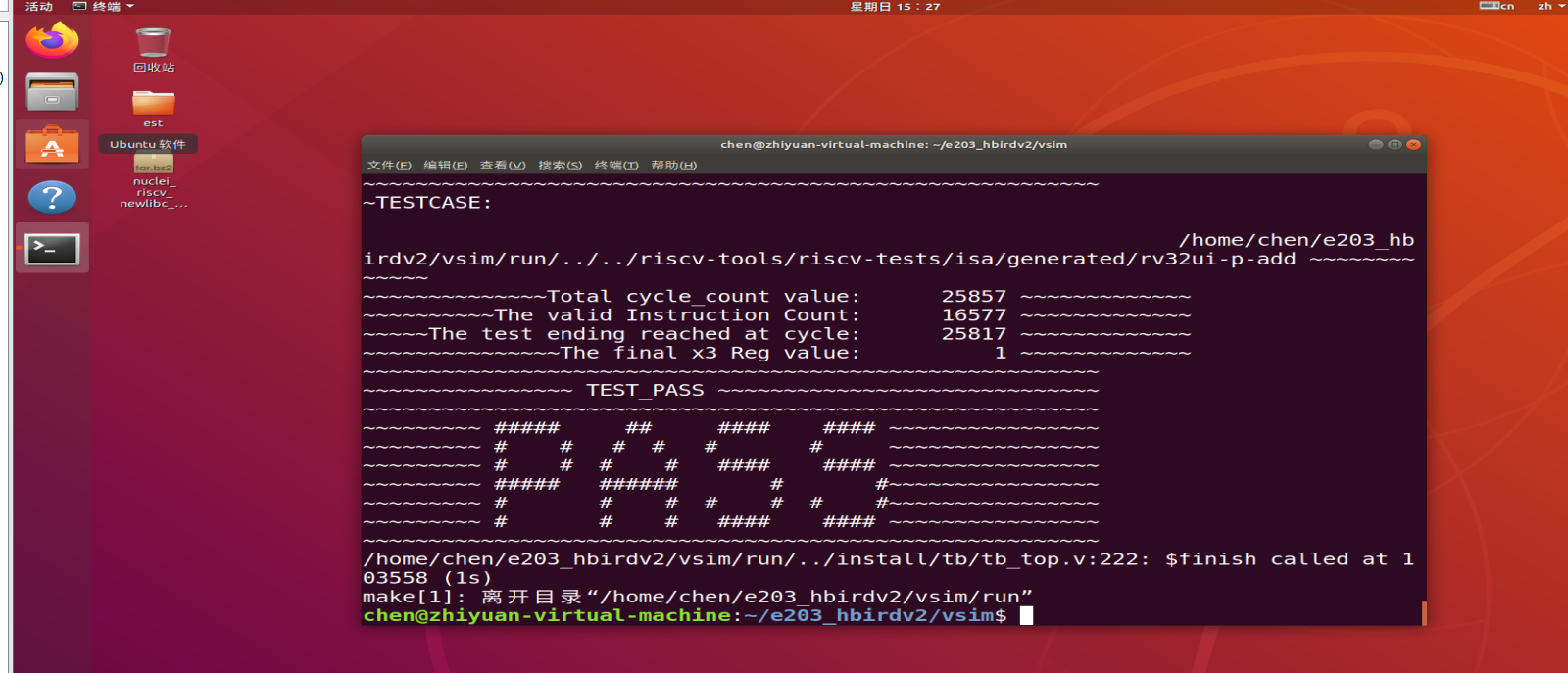

综合网表成功后,可以运行仿真。

make run_test SIM=iverilog

成功仿真界面:

注意:如果出现错误 /bin/sh: Syntax error: “&” unexpected,则需要转换shell类型为bash:

# 查看shell类型,需要将dash改成bash ls -l /bin/sh sudo dpkg-reconfigure dash #选择 no

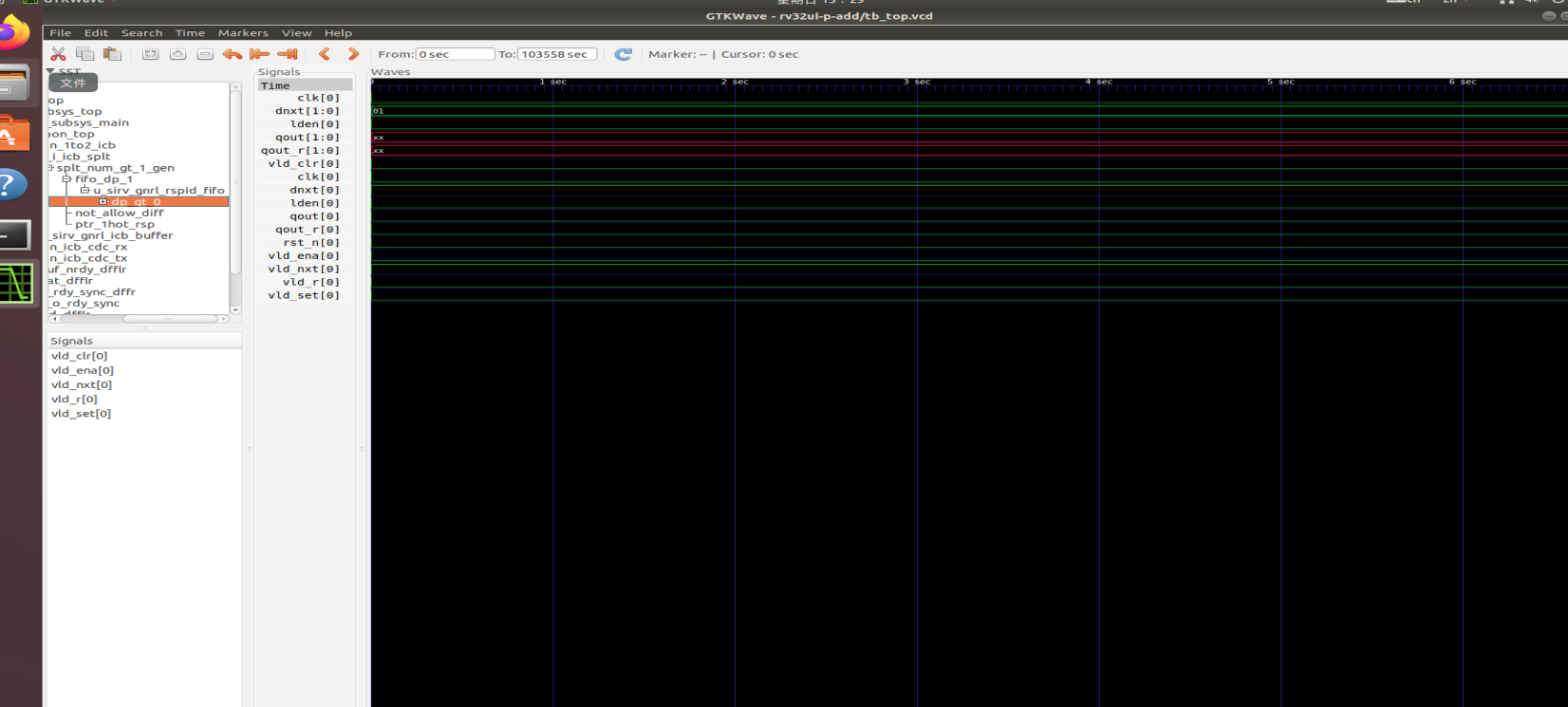

查看波形:

// Using Verdi: make wave SIM=vcs // Using GTKWave: make wave SIM=iverilog

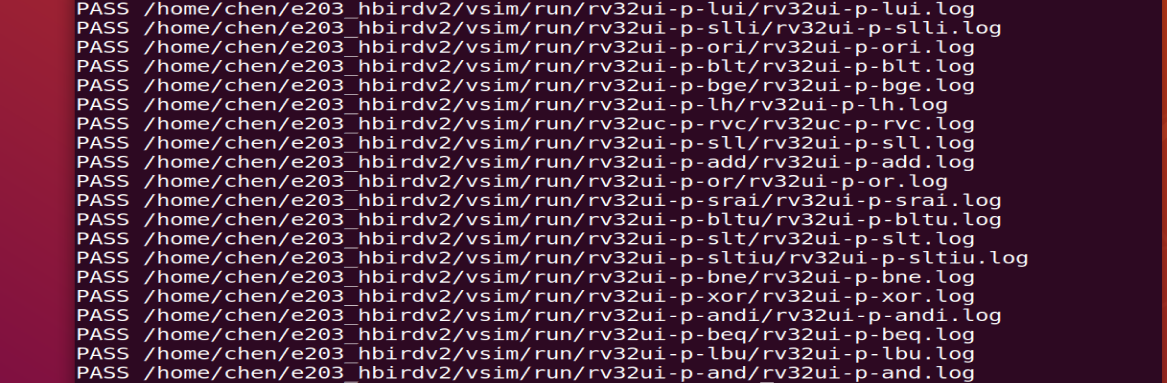

运行一下命令进行回归测试,并查看回归结果:

// For VCS:

make regress_run SIM=vcs

// For iVerilog:

make regress_run SIM=iverilog

make regress_collect

至此,仿真成功。

参考资料:

1、Hummingbirdv2 E203 仿真排坑之路 - 简书 (jianshu.com)

2、4.1. How to run simulation — Hummingbirdv2 E203 Core and SoC 0.2.1 documentation (nucleisys.com)