参考

对应于文档中高电平的低电平,小记中分别使用1和0指代

介绍

根据文档所说,AXI协议可以做到:

- 地址可以在数据之前传输,也就是先传地址,再传数据,emm...

- 支持多个未完成的传输(看了这个协议的文档才知道,outstanding还有未完成的意思)

- 支持乱序完成传输

接下来看看AXI抽象出来的五个传输通道

| 通道 | 信号命名前缀 |

|---|---|

| 读地址通道 | AR |

| 读数据通道 | R |

| 写地址通道 | AW |

| 写数据通道 | W |

| 写响应通道 | B |

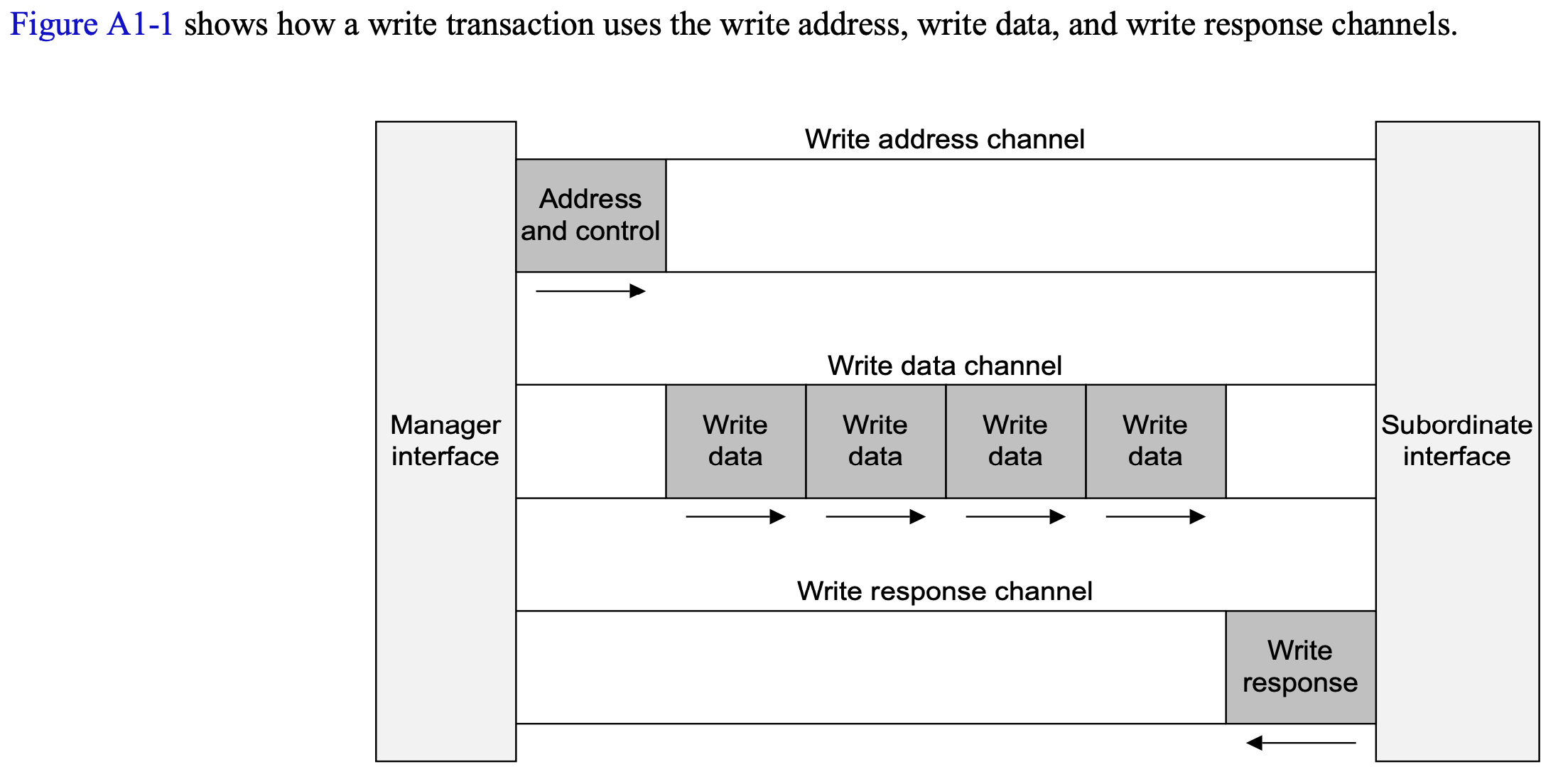

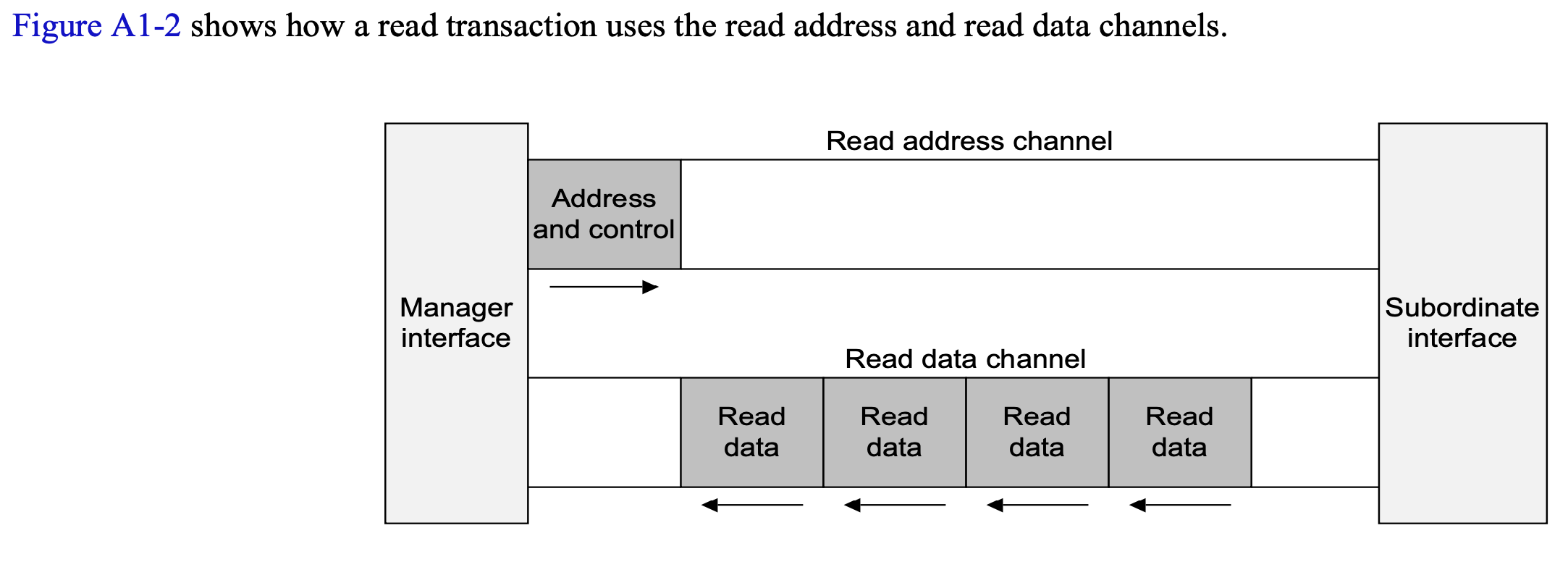

一图胜千言,文档中用几张图简单描述了上面几个通道所携带的数据以及时序关系:

ok,简单来说就是将一堆信号抽象成五个通道,在主从之间控制传输的行为,每个通道包含各自的信号。

Channel(通道)

五个通道的共同点

都由valid、ready和其他信号组成。其中valid和ready就如同字面意思,分别表示发送方数据是否有效,以及接收方是否准备好接收数据,这两个信号是握手的基础。另外还约定last信号来指示本次数据是否最后一个数据。

各自通道还有他们的不同点

ARC/AWC(读地址通道/写地址通道)

包含地址和控制信号

RC(读数据通道)

包含数据总线、用于指示本次读事务是否完成的读响应信号

WC(写数据通道)

包含数据总线、用于指示数据中有每个字节是否有效的strobe信号(strobe似乎是一个固有名词,大概作用就是指示接收者总线上的数据什么时候是有效的)

BC(写响应通道)

类似读响应信号,用于指示本次写事务是否完成的响应信号。为什么写响应需要单独一条通道是显而易见的,因为读响应信号可以与读数据合并在一次传输,而“写”这个操作本来是不需要响应的,因此单独用一条通道来传递写响应信号。

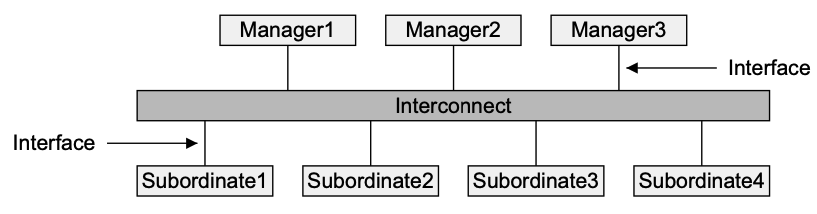

设备之间的连接

AXI给出了接口的定义。系统拓扑可以是:

- 共享地址线和数据线

- 共享地址线和多个数据线

- 多个地址线和数据线

多数情况下地址带宽比数据带宽小很多,因此可以选择第二种拓扑结构。

Register slice

不知道是什么,暂时不管

信号定义

信号不多且好理解,有的信号用于支持一些可选的特性。可以看一下,有个大致印象

全局信号

时钟信号ACLK和复位信号ARESETn,复位低电平有效。所有信号都是ACLK上升沿同步的

AWC信号

| 信号名称 | 信号源 | 说明 |

|---|---|---|

| AWID | M(Manager) | 写事务ID |

| AWADDR | M | 写事务起始地址 |

| AWLEN | M | 写事务中传输次数 |

| AWSIZE | M | 写事务中一次传输的数据大小 |

| AWBURST | M | 突发类型 |

| AWLOCK | M | 原子操作相关 |

| AWCACHE | M | 内存类型 |

| AWPROT | M | 访问控制:权限、安全级别等 |

| AWQOS | M | QoS相关 |

| AWREGION | M | region指示器 |

| AWUSER | M | 用户自定义信号 |

| AWVALID | M | 数据是否有效 |

| AWREADY | S(Subordinate) | 是否准备好接收数据 |

WC信号

| 信号名称 | 信号源 | 说明 |

|---|---|---|

| WID | M | 写传输ID |

| WDATA | M | 写数据 |

| WSTRB | M | 写strobe,指示数据中哪些字节有效 |

| WLAST | M | 指示是否写事务中最后一次传输 |

| WUSER | M | 用户自定义信号 |

| WVALID | M | 数据是否有效 |

| WREADY | S | 是否准备好接收数据 |

BC信号

| 信号名称 | 信号源 | 说明 |

|---|---|---|

| BID | S | 写响应ID |

| BRESP | S | 写响应 |

| BUSER | S | 用户自定义信号 |

| BVALID | S | 数据是否有效 |

| BREADY | S | 是否准备好接收数据 |

ARC信号

与AWC信号类似,只是从写操作换成读操作相关,并且信号以AR为前缀

RC信号

| 信号名称 | 信号源 | 说明 |

|---|---|---|

| RID | S | 读传输ID |

| RDATA | S | 读数据 |

| RREST | S | 读响应 |

| RLAST | S | 指示是否读事务的最后一次传输 |

| RUSER | S | 用户自定义信号 |

| RVALID | S | 数据是否有效 |

| RREADY | S | 是否准备好接收数据 |

一对一接口定义

这个小节介绍一对一主从事务中信号实现的要求和定义

时钟和复位

时钟ALCK

所有输入都是ACLK上升沿有效。

注意,主从接口之间的输入输出信号不能有组合电路

复位ARESETn

ARESETn异步低电平有效,但取消复位是同步的。复位使得:

- 主机接口置ARVALID、AWVALID、WVALID为0

- 从机接口置RVALID、BVALID为0

- 其他信号可以是任意电平

ARVALID、AWVALID、WVALID最早能置1的时刻为:ARESETn置1后的第一个ACLK上升沿

基础读/写事务

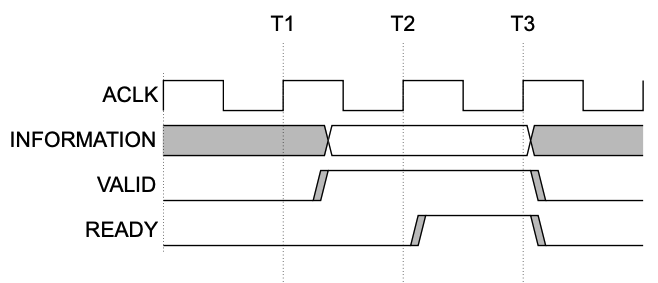

握手

当VALID和READY同时为1时才能开始传输数据,利用这点,发送方和接收方可以很方便地控制数据的传输速率。

注意,主从接口之间的输入输出信号不能有组合电路。

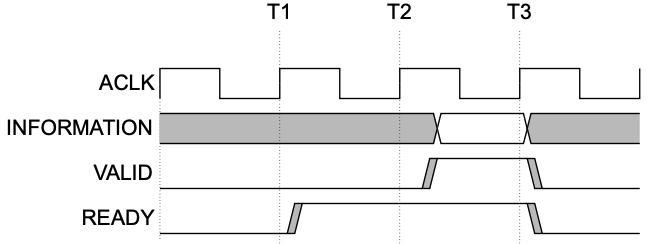

下图展示VALID在READY之前有效的一次握手:

文档中还提到:

A source is not permitted to wait until READY is asserted before asserting VALID

我一开始也不理解这句话,以为是VALID必须在READY有效之前就有效,但这样下面的「READY在VALID之前有效的握手」就不成立了。因此结合知乎大佬的文章,应该修正为:发送者不允许主动等待READY有效之后再置VALID有效,而是应该数据一旦有效就应当置VALID为有效

VALID一旦有效,就必须保持到握手完成,即VALID和READY均有效的上升沿。

下图展示READY在VALID之前有效的一次握手:

相应地,文档提到:

A destination is permitted to wait for VALID to be asserted before asserting the corresponding READY

也就是接收者可以等VALID有效之后再令READY有效,并且READY在有效之后,在VALID有效之前即握手完成之前将READY置无效。直观地看,接收者对于设置READY比发送者VALID的自由度更大。

各通道的握手信号及约定

各通道的xVALID和xREADY的共同规则同「握手」小节中的VALID和READY。

AWC

协议推荐AWREADY默认值为1,不推荐默认为0的原因是这样会使得传输需要至少两个周期,第一个周期置AWVALID有效,另一个周期置AWREADY有效。(???)

WC

WREADY的默认值可以是1。当事务中最后一次传输的时候,主机必须置WLAST有效。协议推荐WDATA无效字节置0

BC

BREADY的默认值可以是1

ARC

协议推荐ARREADY默认值为1,理由同AWREADY。

RC

从机只能在响应数据读取时才置RVALID有效。RREADY默认值可以是高电平。当事务中最后一次传输时,从机必须置RLAST有效。协议推荐RDATA无效字节置0

通道之间的关系

AXI协议对于通道之间的关系只作了如下规定:

- 写事务最后一次传输必须跟着写响应

- 读地址后必须跟着读数据

- 握手必须遵循下面的「握手信号间的依赖」规则

对于其他情况,通道间保持独立互不影响。

当主机发起写请求事务,所有写数据的提供不能依赖于该主机其他的事务

握手信号之间的依赖

再次总结VALID和READY的关系如下:

- VALID不能依赖于READY

- READY可以依赖VALID

其中第二点有利于设计更高效的通信。

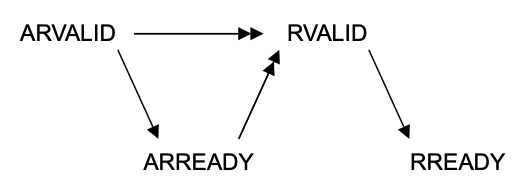

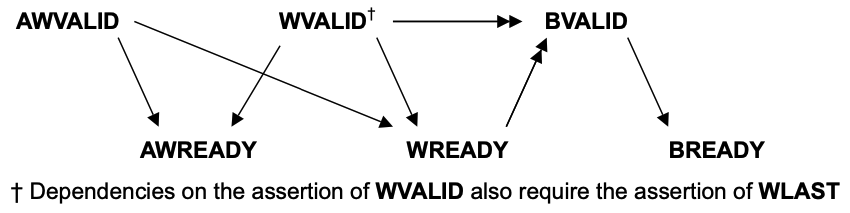

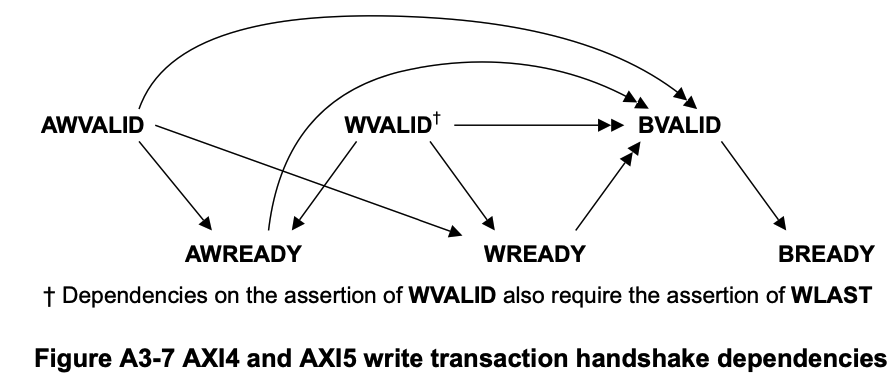

对于不同通道,上述的两个规则有不同的具体表现,并用依赖图表示。在依赖图中:

- 单箭头:被指的信号不依赖于起始端信号,即可以在箭头起始端信号置有效前或置有效后置有效。

- 双箭头:被指的信号依赖于箭头起始端信号,即必须在箭头起始端信号置有效后再置有效。

起始端信号这里有点疑惑,起始端信号是依赖于被指信号还是不依赖?其实是起始端信号不能主动等待被指信号的有效而置有效,即起始端信号不能依赖于被指信号,比如读事务依赖中,ARVALID不能依赖于ARREADY,而ARREADY可以依赖于VALID也可以不依赖。

读事务依赖

依赖图如下,可以看到RVALID必须在ARVALID有效之后有效,对应了「通道之间的关系」中的读地址后必须跟着读数据

写事务依赖(AXI3)

依赖图如下,可以看到

由于写数据通道与写地址通道没有依赖关系,因此可以看到WREADY并不依赖于AWVALID。另外手册中图 A3-6 即上图中的注释部分似乎将 BVALID 误写为 WVALID,因为主机置起 WVALID 似乎与本次传输的 WLAST 无关,而且文本中也提到 BVALID 依赖于 WLAST(摘自参考链接)

写事务依赖(AXI4 & AXI5)

这个版本协议的新增内容是,BVALID依赖于AWVAID、AWREADY、WVALID、WREADY,即地址和数据握手都成功的情况下才能响应。这个新增的依赖补充了当只有数据而没提供地址的时候,数据是不会被写入的,因此从机自然也不应该响应。

事务结构

地址结构

AXI是基于突发传输的,也就是主机向从机发送控制信息+起始地址,就可以一次性传输多个数据单元,并且后面的地址都由从机自行给出。

一个突发传输地址不能跨越 4KB 边界,之所以这样规定是为了避免访问两个subordinate(每个subordinate的地址空间是4K/1K对齐的)。