20200120 Add XXX的PCB Layout布线评审

1、初级的网口走线以及GND和初级抽头之间有间距要求,一般至少20mil;(待确认)

2、初级抽头的泄放路径先经过RC电路,再过压敏;(待确认) 压敏和75ohmRC位置调整,RC调整到靠近抽头。

3、层叠考虑时,在考虑高速走线的情况下,适当关注小电压大电流(一般是CORE电压)的铺铜需求;

4、给Layout时一定要事先把关键信号列出来设定布线规则,比如I2C、SMI、UART、SPI等;

5、DDR颗粒以及CPU的DDR_VREF电压。

摘录文档:DDR4 SDRAM MICRON MT40A2G4/MT40A1G8/MT40A512M16

20191126 Add 一搏武汉研讨会

1、常规层叠,无非就是看长度吃饭。长度决定我们要的板材级别,PP尽量选好的,尽量不要选单张106或者1080

PP介质厚度>19mil,需要在其中塞光板,这也是假八层产生的原因。(一搏案例:8层做成假12层、12层做成假20层)

2、一般的PCB投板文件分成三种:(1)Gerber,包括RS-274X(new)和RS-274-D(old)两种;(2)ODB++,该文件提供的内容过于丰富,会被“反推”;(3)PCB源文件。最后给板厂时,最好使用IPC356(设计工程师的守护神)

3、板材与成本:M4、M6、M7、M8、RO4350,M7NE+HVLP2,M6G+RTF(HVLP)

4、一般28层,板厚差不多3.2mm;一般控制板厚3.2~4mm以内;太厚的板厚,有个参数:厚径比,要提前询问板厂是否能做。背板大多比较厚,一般全部是压接件。

5、高速板材、走线太短更需要关注阻抗的一致性,不然反射会更严重。

6、高速走线中,过孔、AC耦合电容不优化,会导致阻抗偏低、偏容性,阻抗不连续,信号反射,太短的走线反射更严重。

7、按键、ICT等需要选择沉金工艺,不要选择OSP,OSP有一层氧化膜。

8、高速走线中,要注意stub的控制,使高速线能有更长的走线长度。

9、微孔:常用的PCB微孔技术,二氧化碳钻孔以及激光钻孔之外,还有机械钻孔式、感光成孔、雷射钻孔、电浆蚀孔及化学蚀孔等(百度所得)

10、TP点选取在中间测试会有信号反射。

11、U-Turn via stub mitigation,通过两个过孔,减小Stub。

12、如果表面光铜,没有绿油,表面处理有镍,镍对信号衰减影响较大。

13、一个实验,标签纸、静电防护带(都有磁性),贴表面对阻抗影响很大。

14、焊接:a.锡膏的选用;b.钢网优化;c.锡膏厚度检测(测厚仪)。

15、密间距、01005封装器件的加工能力。

16、拼版:V-CUT(走直线)、邮票孔

17、PCB设计时,要考虑制板工厂可加工PCB的最大尺寸。

18、IPC-A-6012C表3-2中,金手指金厚的要求:1级和2级0.8um[31.5uin],3级1.25um[49.21uin]

注:微英寸(uin)通常用“u”表示。

19、为改善多层PCB板内层残铜率低,铜箔密度分布不均匀,而引起的压合中胶体流动和外层铜箔铺设分布不均匀造成的电镀厚度不一致等相关制造工艺问题,在PCB各层面上添加相应的孤立铜块。根据铜块添加的层面和位置不同区分如下:如果添加在内层,叫阻流块;如果添加在外层,叫电镀块,也叫平衡铜。

20、10G以内不需要圆弧走线。(高速先生第16期)

21、一对好的差分线应有的特质,差分线P和N的一致性,所谓一致性就主要由阻抗和延时这两个因素决定。

22、常规的两种差分结构:GSG、GSSG

23、在实际生产中,同一个浸润层最多可以使用3个半固化片,且最大厚度不能超过20mil。超过此数据需要考虑增加芯板来制作,可以把芯板两面的铜箔蚀刻掉或者直接用光板,再在两面用半固化片粘连,这样可以实现较厚的浸润层。最少可以只用一个半固化片。但有的时候因内层铜箔分布稀疏,或者成品铜厚太厚。需要大面积填胶,厂家出于产品的可靠性考虑,要求必须至少使用两张PP。

咨询了下,并没有说一定不能走表底层,主要出于串扰(表层只有一个参考面,内层有两个参考面)、损耗(表面铜的损耗会大点)、阻抗(在加工上,表层阻抗不平整)的考虑。

以下的解答说的更详细点,请查收。

走外层最佳的考虑是不需要打过孔,而走内层需要打孔,且过孔阻抗不好控制,需要额外的优化。

另外走外层的缺陷也有以下几点:

1、从加工的角度考虑,外层有电镀,阻抗波动较大,生产加工性不好控(针对阻抗来说)。 阻抗不好控制

2、外层一般使用的普通铜箔,铜表面粗糙度较大,铜损较大。 损耗较大

3、外层的串扰较大,需要更大的隔离空间。 串扰较大

从相反的角度看内层:

1、内层的阻抗平整度会好很多,阻抗加工上好控制。

2、内层可以采用低表面粗糙度的铜箔,铜损小。

3、内层串扰相对小。

4、过孔需要特殊优化,尤其是针对较高速如25G信号,尽量避免过孔带来的不利影响。

2019.2.1 Add

内层有两层参考平面,没有远端串扰;

高速线走内层 远端串扰比表层小很多;

信号是以电磁场的形式向前传输,高速线尤为明显,能量主要集中在表面,用带状线来布的话可以将电磁场屏蔽在两个平面之间,减小电磁场的损耗,也就是减少信号的损耗;

带状线可以更好的抑制走线EMI EMC效应;

1.高速线走内层 远端串扰比表层小很多

2.微带线上面是空气 下面是介质 还覆盖绿油 阻抗比带状线难控制

3.微带线在表层 速率越高产生的电磁辐射越强 容易干扰其他的线和器件 而且也容易被其他的干扰源干扰 带状线两边都是屏蔽层会比微带线受干扰程度好很多

减小串扰的方法:

2、减少耦合长度

3、使用介电常数较低的层叠;

4、在带状线层走线;

5、合理选用防护地线(打孔有风险,包地需谨慎);

6、尽量采用平面作为返回路径;

7、在封装和接插件中不要共用返回引脚;

8、满足时序的前提下,增大信号上升时间。

串扰歌

世人都道怕串扰,惟有“成本”忘不了,

密密匝匝小间距,容性感性增烦恼。

世人都道怕串扰,饱和长度却忘了,

平行走线飞天际,近端远端全喂饱。

世人都道怕串扰,返回平面却忘了,

难舍难分相邻线,信号耦合入歧道。

世人都道怕串扰,收发分层却忘了,

线穿孔复孔穿线,高速通道纷扰扰。

传输线中有电流通过时,电磁场能量分布类似正态分布,约70%地能量集中在导线周围3H范围内。如果两导线距离大于3H,两导线之间的互感会急剧下降,能有效降低的串扰量。这就是PCB设计工程师3H/W经验法则的由来。根据经验法则,两线间距3W情况下,近端串扰约在1.9%,远端串扰约-2.2%(仅微带线,带状线几乎没有远端串扰,这也是我们建议高速传输线在内层布线的原因)。H是指走线到参考层的高度,因为常用50欧姆阻抗线线宽W接近H,为了量化通常用W表述,实际设计中W通常都大于H。另外减小H能加强与GND平面的耦合,使能量集中在更小的范围,相同间距下串扰更小。由于H减小,阻抗线线宽也会减小,不需要额外空间就增加了间距,再次减少串扰。这个技能你get到了吗?(下面是3W经验法则的示意图)

高速链路中我们通常使用均匀传输线以保证阻抗连续性,使信号在传输过程中没有反射。

如果在传输线中途有感性突变,信号会受到怎样的影响?小陈自己脑补了一波:由于传输线中有额外的L,根据阻抗公式

(1)一搏:低于8G的信号不用挖空,作用不大,但是要求也会做。(挖空,阻抗匹配)

(3)实心的是动态 Dynamic fill →Smooth 动态铜会自动避让 静态不会

(4)DDR 一般规律:时钟线>控制和地址线>数据线

(5)PS_12VLS网络实际上是普通信号线,而不是电源。电源厂商建议我们PS_12VLS以地为参考,尽量干净,所以走粗线就可以了,不需要布成电源平面。

(6)过孔的常规选用:整板过孔选用大小为10mil的过孔22mil的盘的过孔,0.8mmBGA过孔选用8mil的过孔18mil的盘,0.65mmBGA过孔选用8mil的过孔16mil的盘。请确认是否按常规选用。

常规的孔的大小:8MIL的孔16mil的盘(塞孔,用于0.65BGA/散热盘)

8MIL的孔18mil的盘(塞孔,用于0.8BGA/散热盘)

10MIL的孔22mil的盘(塞孔/开阻焊,塞孔用于1.0BGA/散热盘/整板,开阻焊的用于BGA以外,也就是整板)

12MIL的孔25mil的盘(塞孔/开阻焊,散热盘,开阻焊的用于BGA以外,也就是整板)

16MIL的孔30mil的盘(开阻焊)

8mil的孔都是塞孔,用于不同的BGA,10mil、12mil的孔,既有开阻焊的也有塞孔形式的,10mil的塞孔用于整板也有BGA,12mil都是整板的不适用于BGA,但是BGA只用塞孔。12mil以上的孔都是开阻焊的孔。

(8)东莞生益背钻:一般背钻钻头比一钻钻头大8mil。VIA孔如果取负公差,一般一钻钻头比完成孔径大2mil,其它PTH孔,一般一钻钻头比完成孔径中值大4mil;线到背钻背头间距保证最小7mil;特殊情况可做到5mil,但需采用特殊控制,效率和成本会有所影响。

20180313 XXX:背钻常规是会预留8-10mil安全距离。

(9)VCUT角度设定范围要求:板厚≤1.0mm时,VCUT角度A为30°±5°;1.0mm<板厚≤2.5mm时,VCUT角度A为45°±5°;板厚>2.5mm时,VCUT角度A为60°±5°

(12)XX科技常规计算1oz铜厚40mil过流1A,2oz铜厚20mil过流1A。

20180316补充:一搏的一种电源通流标准:外层可以30mil/1A,一般内外层都会按照1A/40mil计算。

(13)不同速率允许的stub,例如8G:300/8=37.5mil;25G:300/25=12mil;300/16=18.75mil。

(14)在PCB层叠确定之后,控阻抗的主要手段为调节线宽。

(15)在实际计算的时候,不管是表层还是内层,都不会写1.4mil(表层除非你跟你的板厂说基铜+电镀的总铜厚是1OZ)表层基铜铜厚1OZ+电镀(一般是0.5OZ),铜厚会在1.6mil到1.8mil左右,内层1OZ铜厚因为蚀刻的影响,通常在1.2mil(xxx中间是1.1mil)左右。

(16)高速信号换层处走线尽量保证对称出线。

(19)特征阻抗概念:

这是一个特征阻抗近似计算公式,式中L为分布电感,C为分布电容。

特征阻抗:这是使用频率非常高的一个专业术语,在各种定义中,笔者最喜欢的描述是:特征阻抗是沿线上分布电容和电感的等效,它的物理意义是,入射波的电压与电流的比值,或反射波的电压与电流的比值的负值。这个定义方式直观明了地解释了很多高速设计问题,方便设计工程师去理解阻抗控制的概念。

上一篇文章提到了微带线与带状线,以及他们分别代表的电磁场意义,现在我们简单看一下两种传输线结构的阻抗计算公式:

微带线阻抗:

带状线阻抗:

还是一样的原则,我们不需要记公式,只需要记住各个元素和阻抗的比例关系,然后能在工作中灵活运用就好了:

介电常数Er:材料性质的一种, 决定当单位电压下, 单位容量內材料可存储的静电能。介电常数增大,阻抗减小。

线路到参考平面距离H:距离增加阻抗增大

线宽W:线宽增加阻抗变小.

铜厚T:铜厚增加阻抗变小.

相邻线间距(针对差分):间距增大阻抗增大

绿油厚度:厚度增加阻抗变小

(20)厚径比,结论:通用要求单板的厚径比≤8:1,最大不能超过12:1

(22)anti-etch

用于负片的分割,把负片分割成两个或者多个部分,是负片层用来画分割线的一个层面。

俗称墨线,当出Gerber时,如果内层出负片,则只出墨线,pcb板厂在曝光时,只曝光墨线部分。

在xsection里面先要设置成plane,negative然后在出geber时选negative。

加anti etch是为了方便plane层分割。正片层不需要anti etch。

etch指allegro软件中的走线及shape,综合指铜皮。

etch在正片的走线层,是指画的线和shape等,即看到的有铜地方。

在负片层,allegro软件中用anti etch线作为shape和shape间的分割线,负片层铺好铜后,有anti etch线的地方是没有铜的,而无anti etch线即是有铜的区域。

(23)2019.5.25 Add

查看XX反馈意见:

1.GND和12V之间保证20mil的间距;

2.POE信号和GND至少隔开1mm(相当于40mil);

3.初级侧(网线侧)网口MDI走线建议走8mil以上;

4.PSE侧的I2C信号不要去参考低压侧的电压。

(24)来源于高速先生《揭开一个等长不等时的“骗局”》

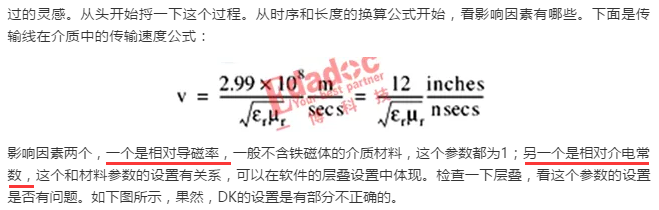

layout工程师也知道,按照常规操作来讲,普通FR4级别的板材,时序和长度换算的经验公式是1ps≈6mil。