数模混合设计的LVS流程

1. 前言

最近项目到了验证环节,在做LVS碰到了一些问题。网络上也没有文章给出完整的解决方案,自己试了一下,踩了一些坑之后基本上搞定了这个问题,现记录流程供学习交流。

整体流程包括:数字模块单独LVS,模拟模块单独过LVS,数字网表反提原理图,顶层数字symbol处理,原理图提取cdl,大网表merge,大图LVS这7个步骤。

2. 数字模块单独LVS

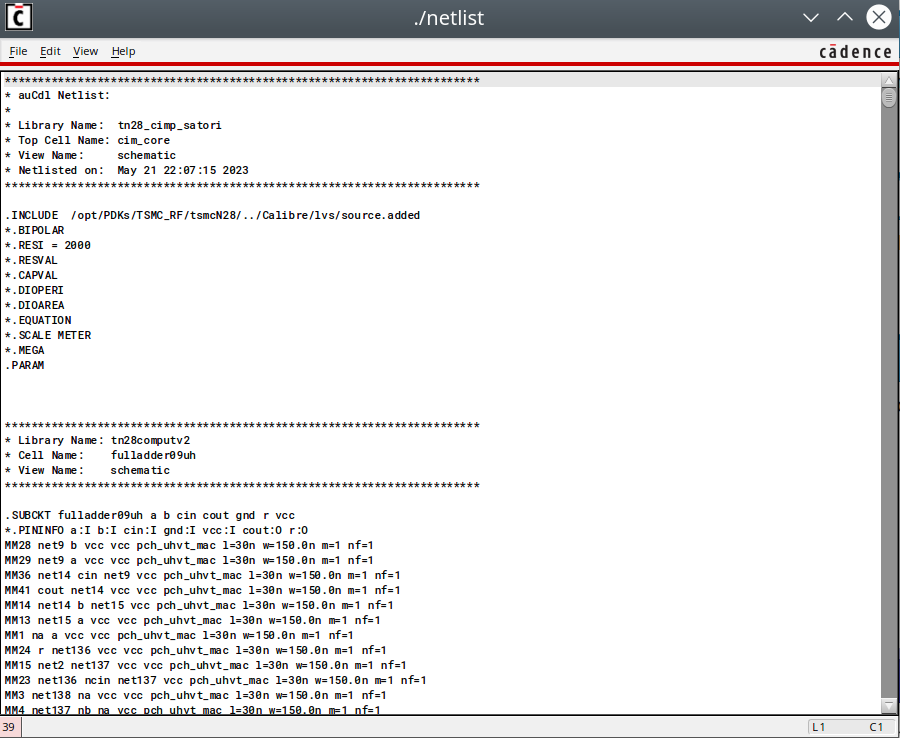

数字后端结束后会提供gds的版图和用于过LVS的verilog门级网表,使用calibre LVS工具做LVS前需要将门级网表转换成cdl网表。这需要使用v2lvs工具。这里有一个教程可以参考:

https://wenku.baidu.com/view/8abaab0503d8ce2f0066233f.html?wkts=1683594986827

主要需要准备几个东西:

- verilog标准单元库

- spice标准单元网表库

以我自己的情况为例,将cim_core_syn.lvs.v的门级网表转换成cdl网表,因为用到了svt和lvt两类单元,所以要把svt和lvt的verilog标准单元库tcbn28hpcplusbwp7t40p140_pwr.v和tcbn28hpcplusbwp7t40p140lvt_pwr.v和spice标准单元网表库tcbn28hpcplusbwp7t40p140_110a.spi和tcbn28hpcplusbwp7t40p140lvt_110a.spi都吃进来。

-v参数跟输入的门级网表,-l参数跟verilog的库,-s参数跟spice库,-o是要输出的cdl

v2lvs -v cim_core_syn.lvs.v -l tcbn28hpcplusbwp7t40p140_pwr.v -l tcbn28hpcplusbwp7t40p140lvt_pwr.v -s tcbn28hpcplusbwp7t40p140_110a.spi -s tcbn28hpcplusbwp7t40p140lvt_110a.spi -o cim_core_syn.cdl

这样就获得了门级网表转换出的cdl网表了。需要注意使用这个cdl网表时需要保证tcbn28hpcplusbwp7t40p140_110a.spi和tcbn28hpcplusbwp7t40p140lvt_110a.spi两个spice标准单元库也在路径下,因为打开cdl网表可以看到,它会去调用这两个spice。

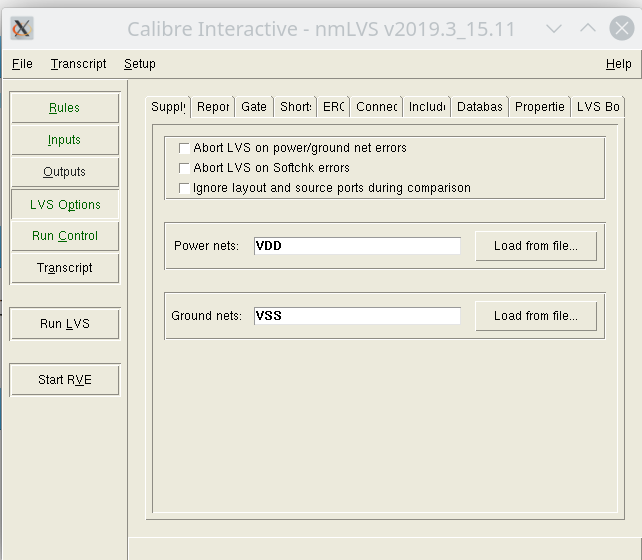

这个cdl文件就可以去和数字模块进行LVS了。在进行LVS时还有一个小坑是可能会出现找不到POWER&GROUND导致LVS出现abortion(因为子模块没有定义Global PG),出现报错:

WARNING: Invalid PATHCHK request "GROUND && ! POWER": no POWER nets present, operation aborted

https://bbs.eetop.cn/thread-305649-1-1.html

解决方案是在Setup->LVS Options中打开LVS Options的选项,在Supply标签页下勾掉Abort LVS on power/ground net errors,并在底下填写Power nets和Ground nets的标签名:

然后就能顺利LVS了。

3. 模拟模块单独LVS

模拟模块的LVS相对简单,这里不做赘述了,可以参考前面写过的这个博客:https://www.cnblogs.com/sasasatori/p/16041328.html

4. 数字网表反提取原理图

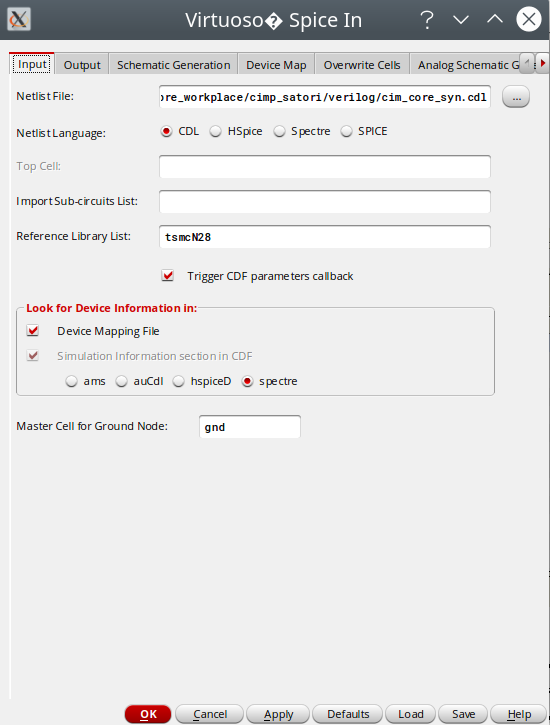

数字部分和模拟部分的拼版环节,首先需要制作原理大图,需要在virtuoso下完成,将数字cdl给转换到原理图的方法可以参考下面的博客。

https://blog.csdn.net/weixin_43277020/article/details/127897221

主要是在Virtuoso下通过File->Import->Spice,打开导入界面,在Input标签页下,Netlist File选择转换好的数字cdl网表,Netlist Language选择cdl,Reference Library List中填写自己使用的工艺库。并且勾选Device Mapping File选项。

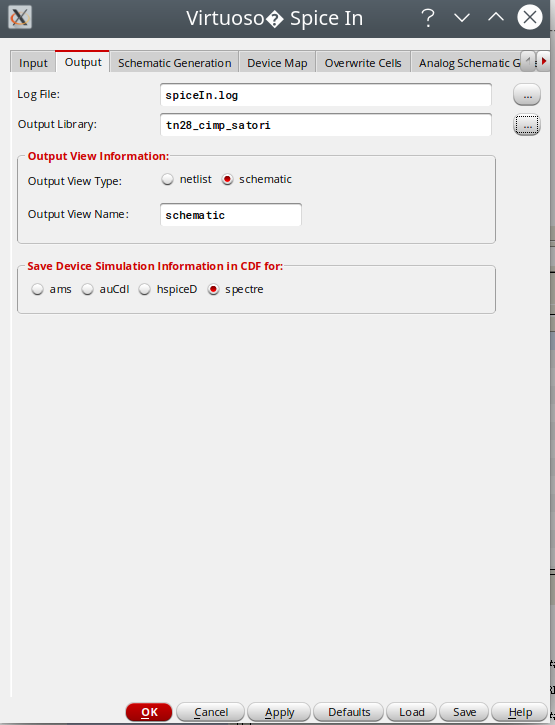

Output标签页下,Output Library选择要输出到的Library。

转的过程中报错:

Spice In did not find the symbol view of the master cell 'nfet' of the instance

解决方式:

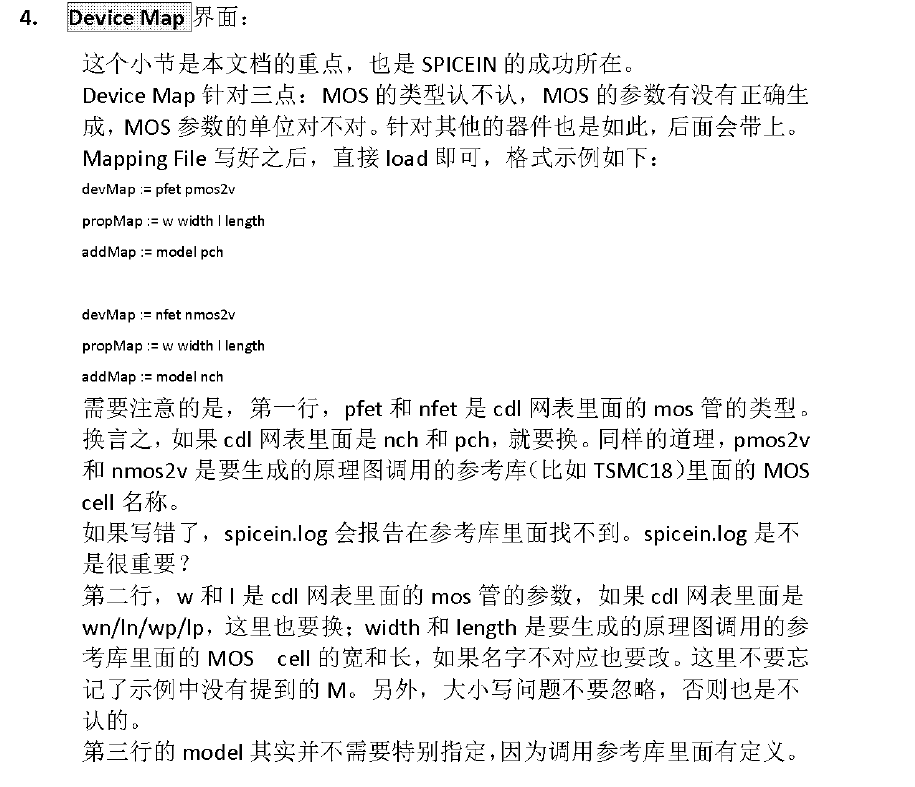

在Device Map标签页下创建一个Device Map,填写要映射的器件,把pfet,nfet,diode等spice网表中的器件名给映射到库里对应的器件名:

Device Map的介绍:

https://bbs.eetop.cn/thread-358413-1-1.html

对于我这里用了多种器件的情况,MappedTo里选择一种器件就行,最后转出来的schematic里的管子的Cell Name可能不对,但是model还是对的。

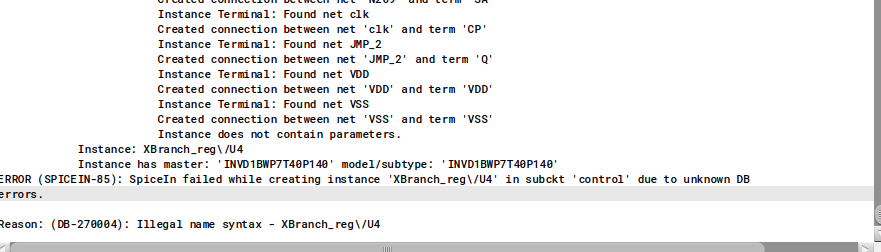

转的过程中还有报错:

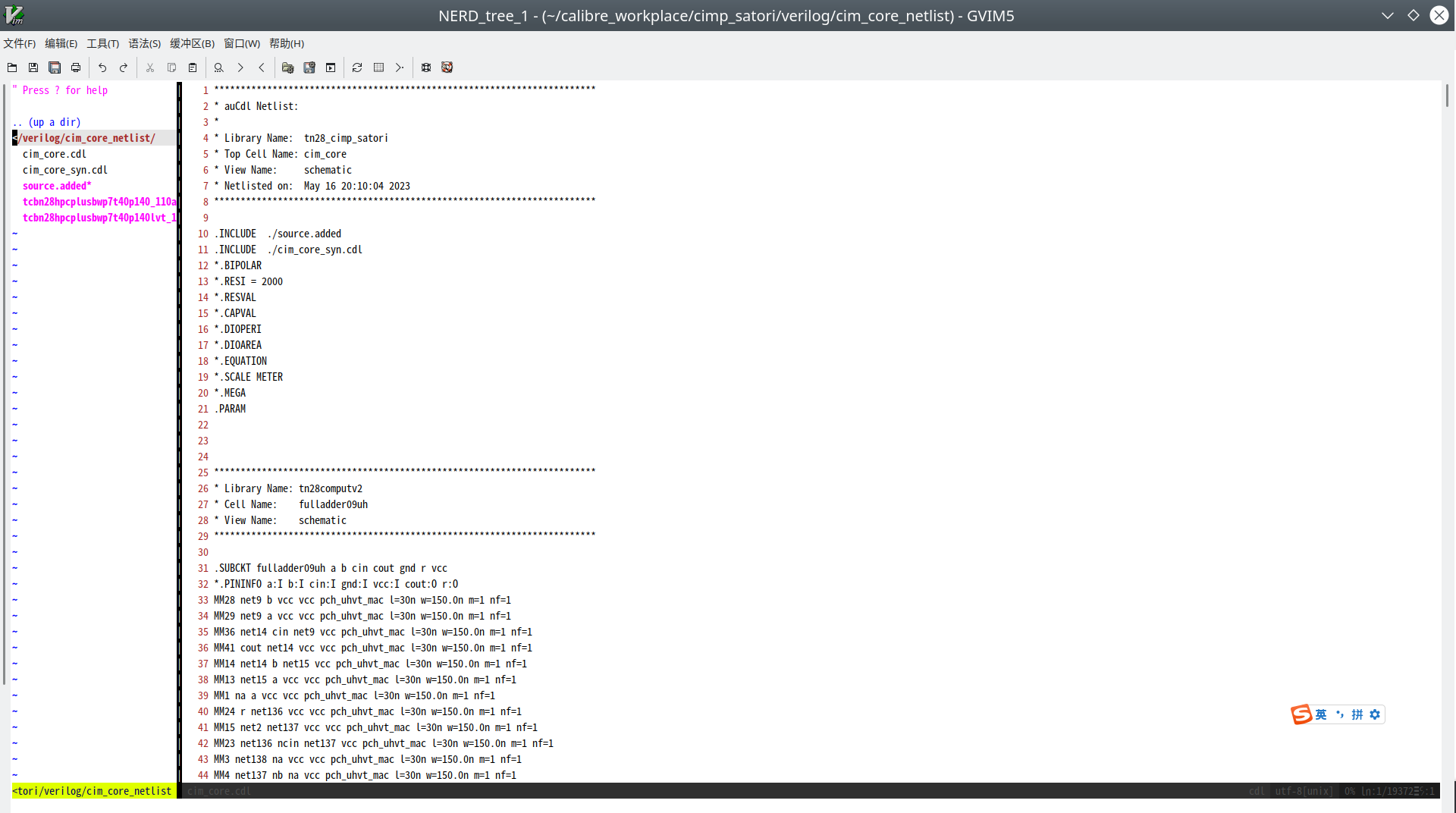

解决方式:到cdl网表中找到名字里带有斜杠/的Instance,把斜杠给全部删掉,我这里用vim直接批量搜索斜杠/然后全部替换成空。

:%s/\///g

全部处理好之后就可以点OK或者Apply进行转换了,最后获得转换好的大原理图。

用这个schematic再制作symbol,然后再去和模拟的部分一起去merge大图,就可以了。

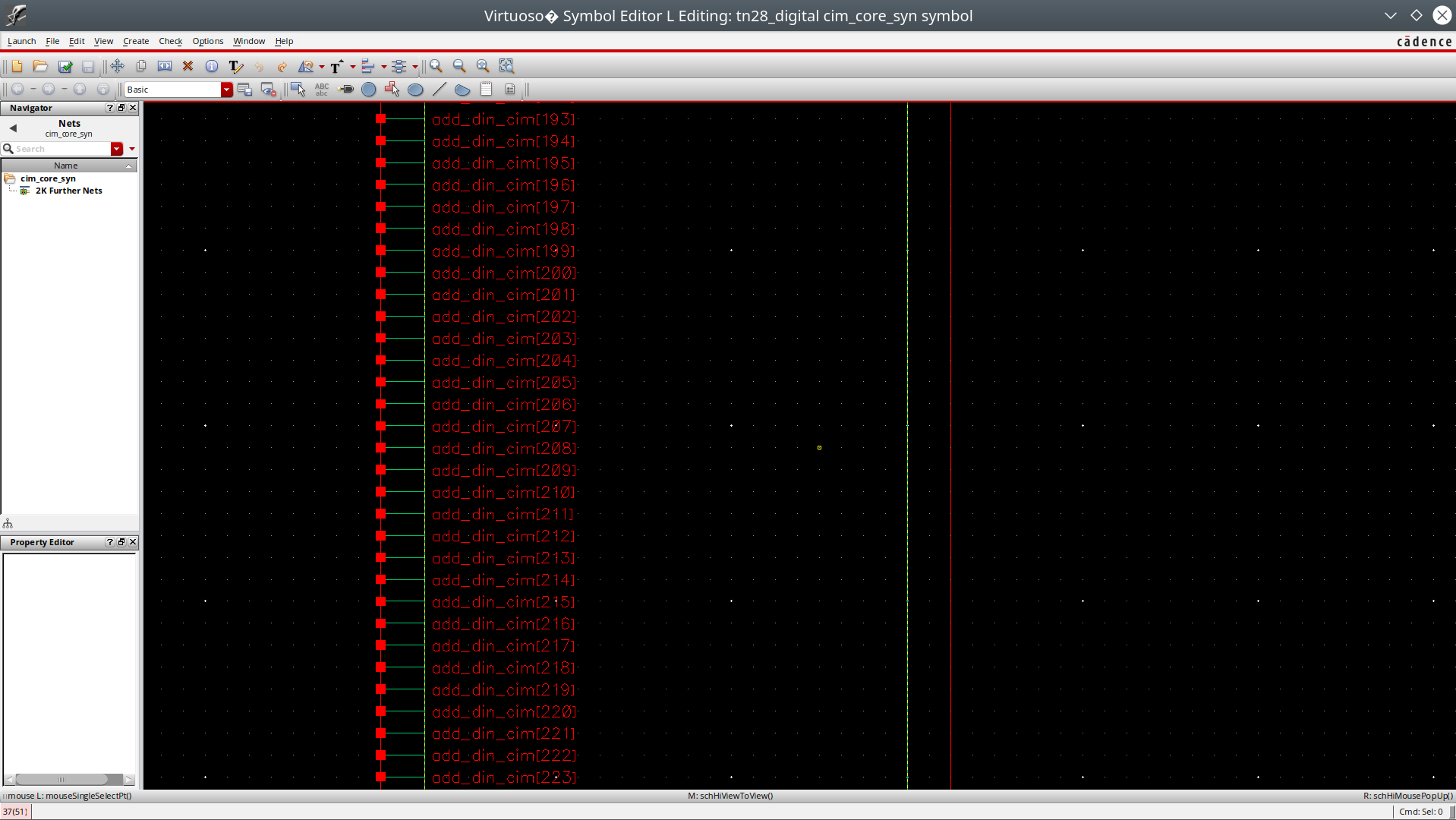

5. 顶层数字symbol处理

虽然已经获得了数字网表对应的schematic,但是如果用它再去导出cdl网表去做LVS就会出现错误,这里主要是工具的问题。

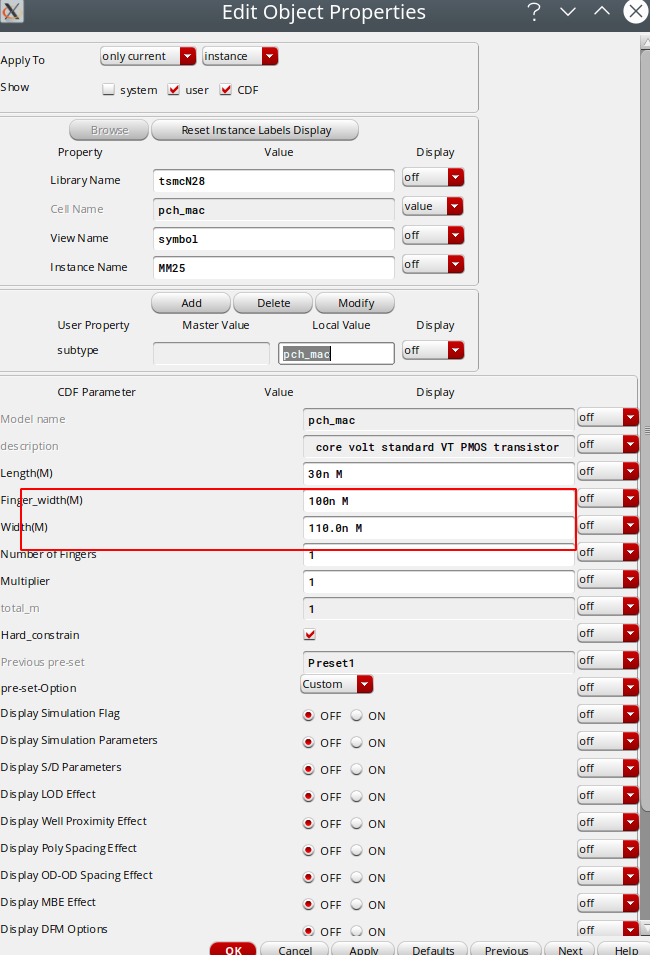

查看tsmc28的spice库发现所有的模型都没有定义finger width这个属性,原理图里的这个finger width属性是由width和finger number在一起计算出来的。只是由于virtuoso软件的bug所以在直接用cdl网表转换出来的原理图里finger width的值是不对的。所有的LVS错误也是由其引发的。

上面这个是用cdl->原理图->网表后做lvs的结果,结果发现这样抽取的w的值和原始网表中的w对应的width不一致了,也是这里导致的lvs中的错误。并且可以发现原理图中出现了finger width和width不一致的问题。

这边也尝试过这个链接里通过skill脚本批量改正finger width的方法。

https://bbs.eetop.cn/thread-469052-1-1.html

编辑这个skill脚本执行后确实可以改正所有的finger width使其在原理图和width一致,但是最后LVS再次导出的网表里的属性仍然是错误的。

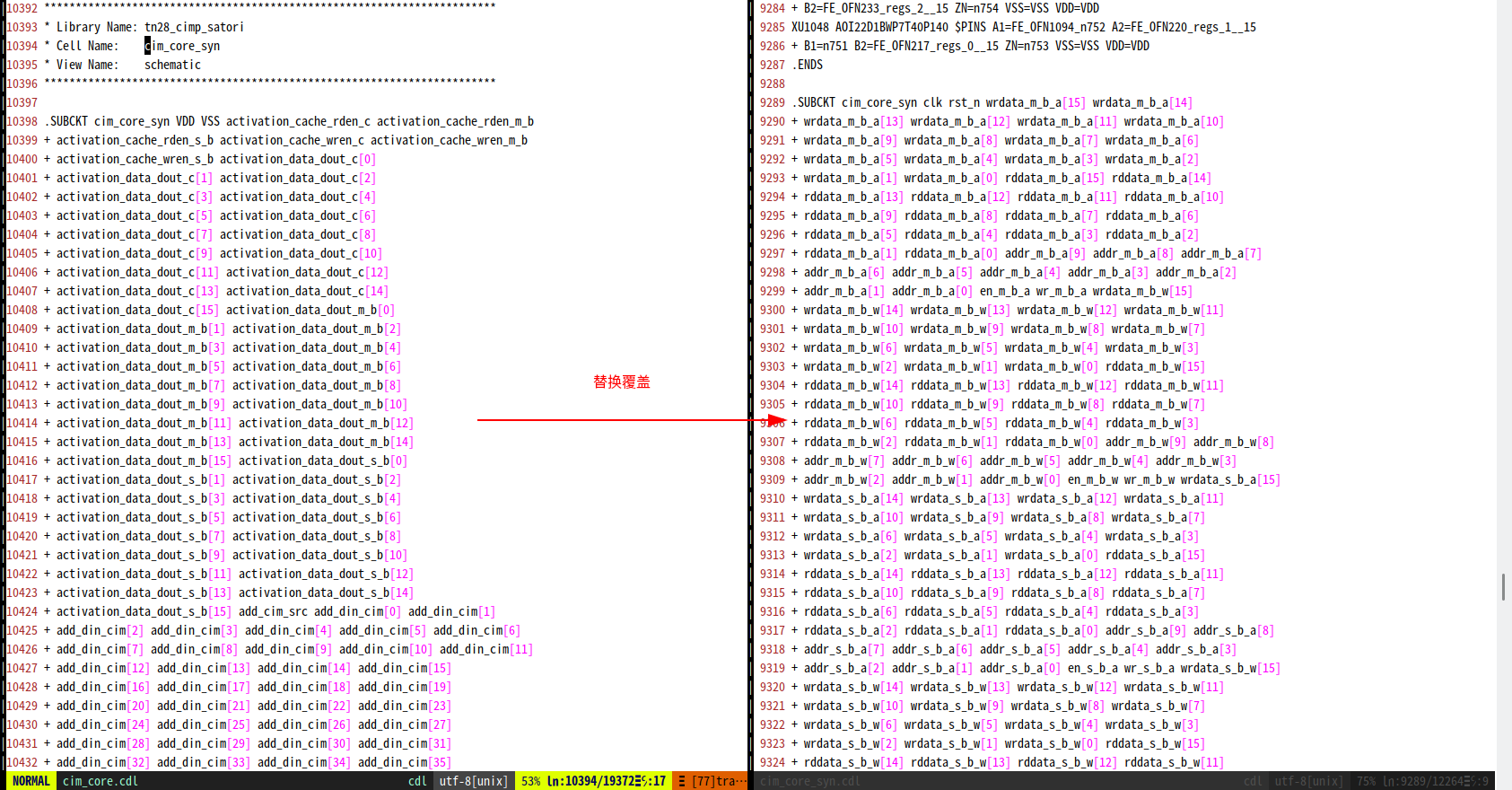

所以进行LVS时绝对不能采取把数字cdl导入到原理图后再从原理图抽取cdl的方法,而是应该直接将原始的数字cdl覆盖掉大图里数字部分的cdl。

为了便利这个覆盖操作,需要再做一个只有pin info的空的数字symbol替换之前schematic提取的symbol,可以直接在原来的schematic下全选所有的instance和wire然后删掉,然后将大的原理图的symbol替换成这个只有pin的空schematic所对应的symbol即可.

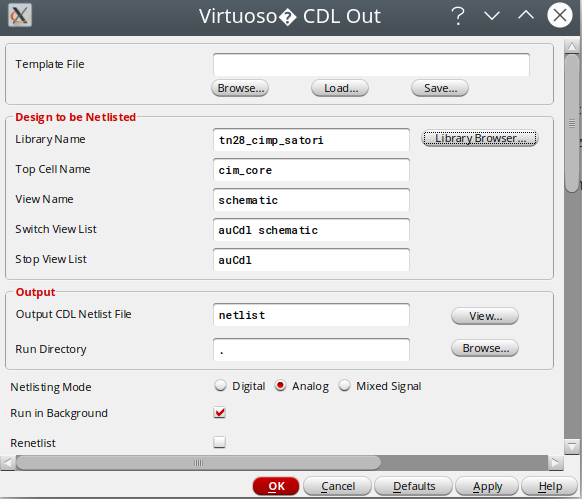

6. 原理图提取cdl

在virtuoso中File->Export->CDL,然后选择要导出的大图原理图即可。运行成功后会弹出一个Netlist的界面,然后File->Save As进行保存。

7. 大网表merge

接下来需要进行大网表的merge,一共是三个步骤:

- 首先复制顶层原理图cdl中数字网表的port部分,对数字网表cdl中的对应数字顶层的port进行覆盖替换(这个原因是因为在进行调用时对于port的顺序是有要求的,不替换会造成线序的错配)

- 在顶层原理图cdl中INCLUDE数字网表cdl

- 删除掉顶层原理图cdl中的数字顶层网表部分

这样就完成了大图网表的merge操作。

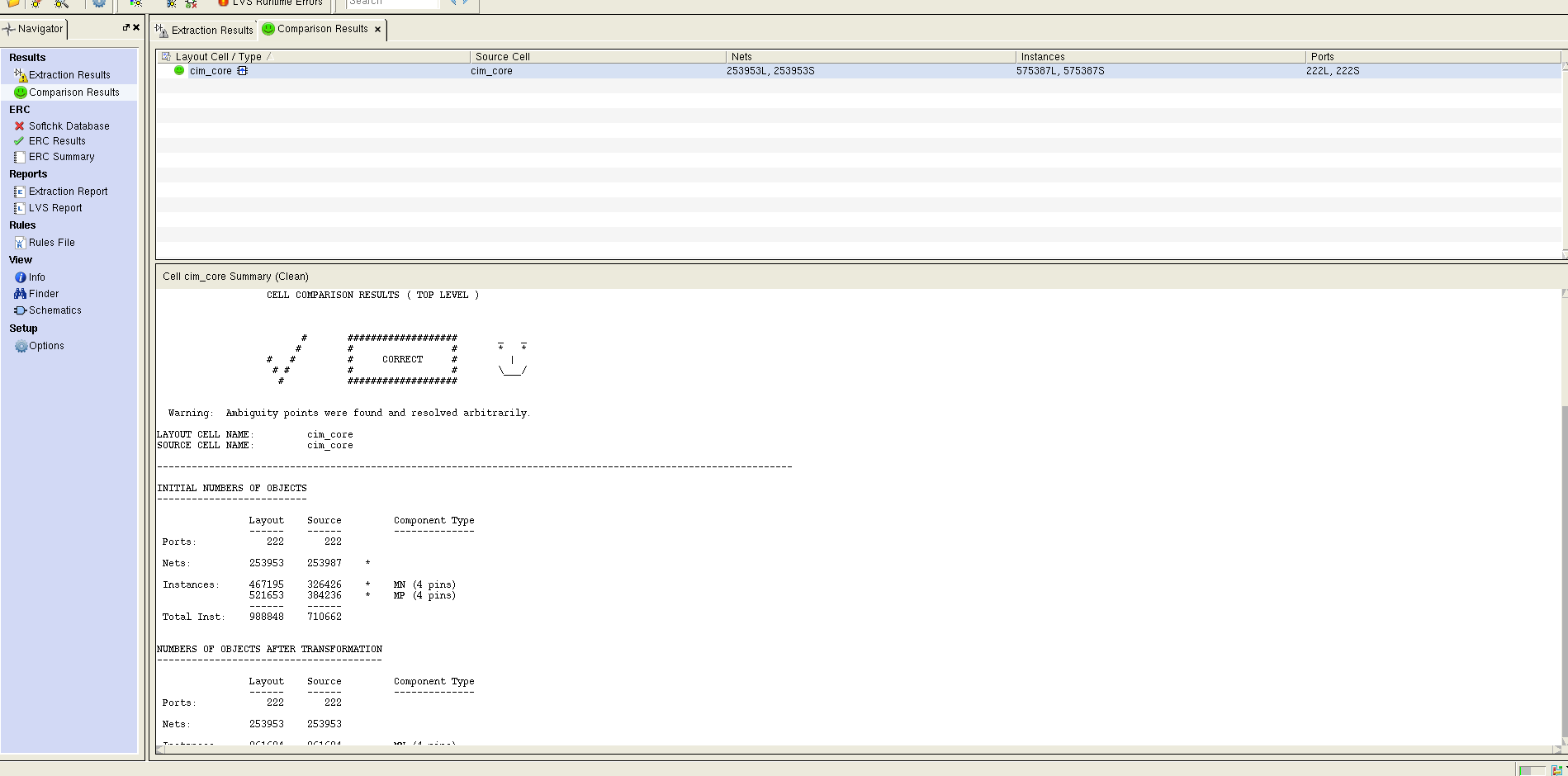

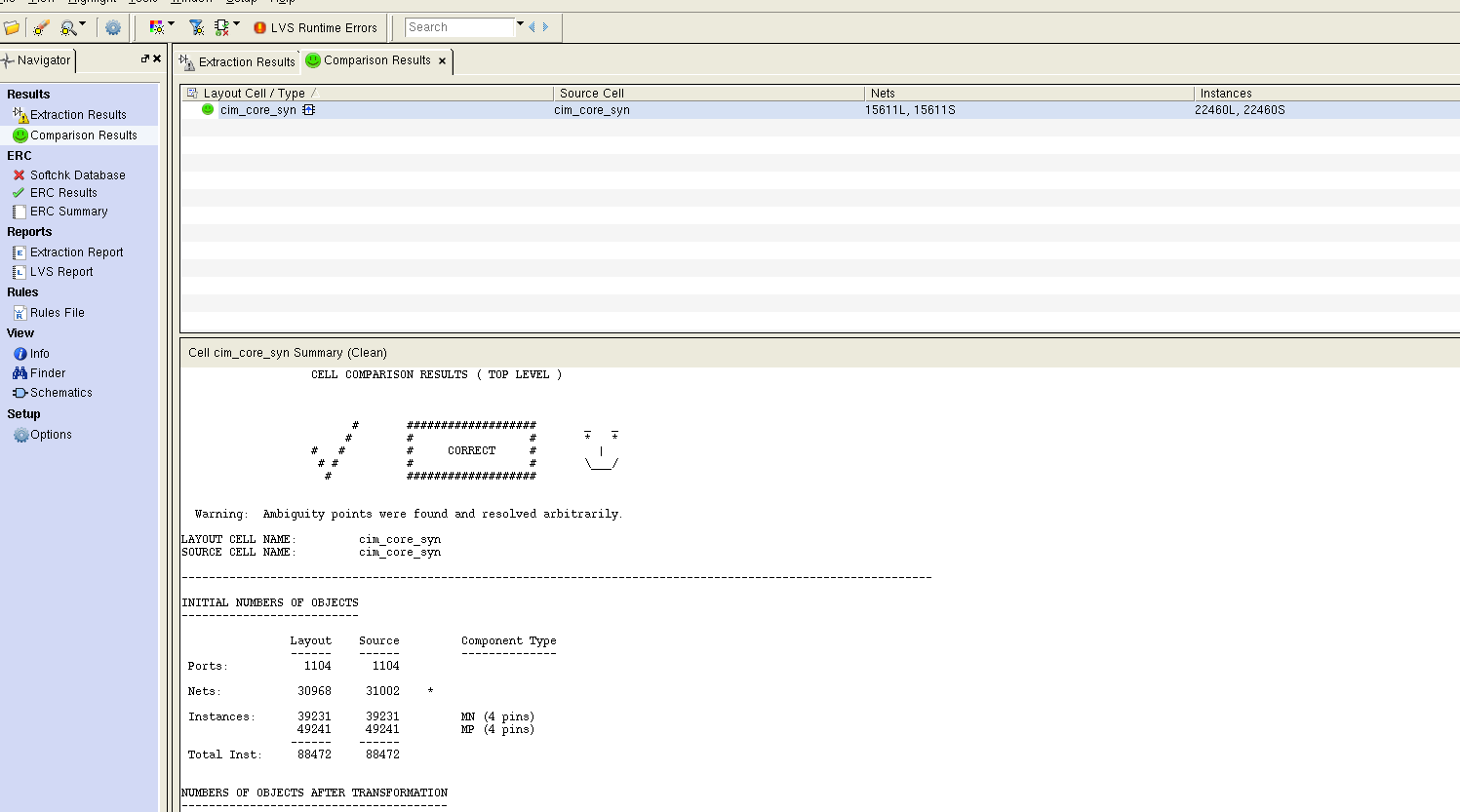

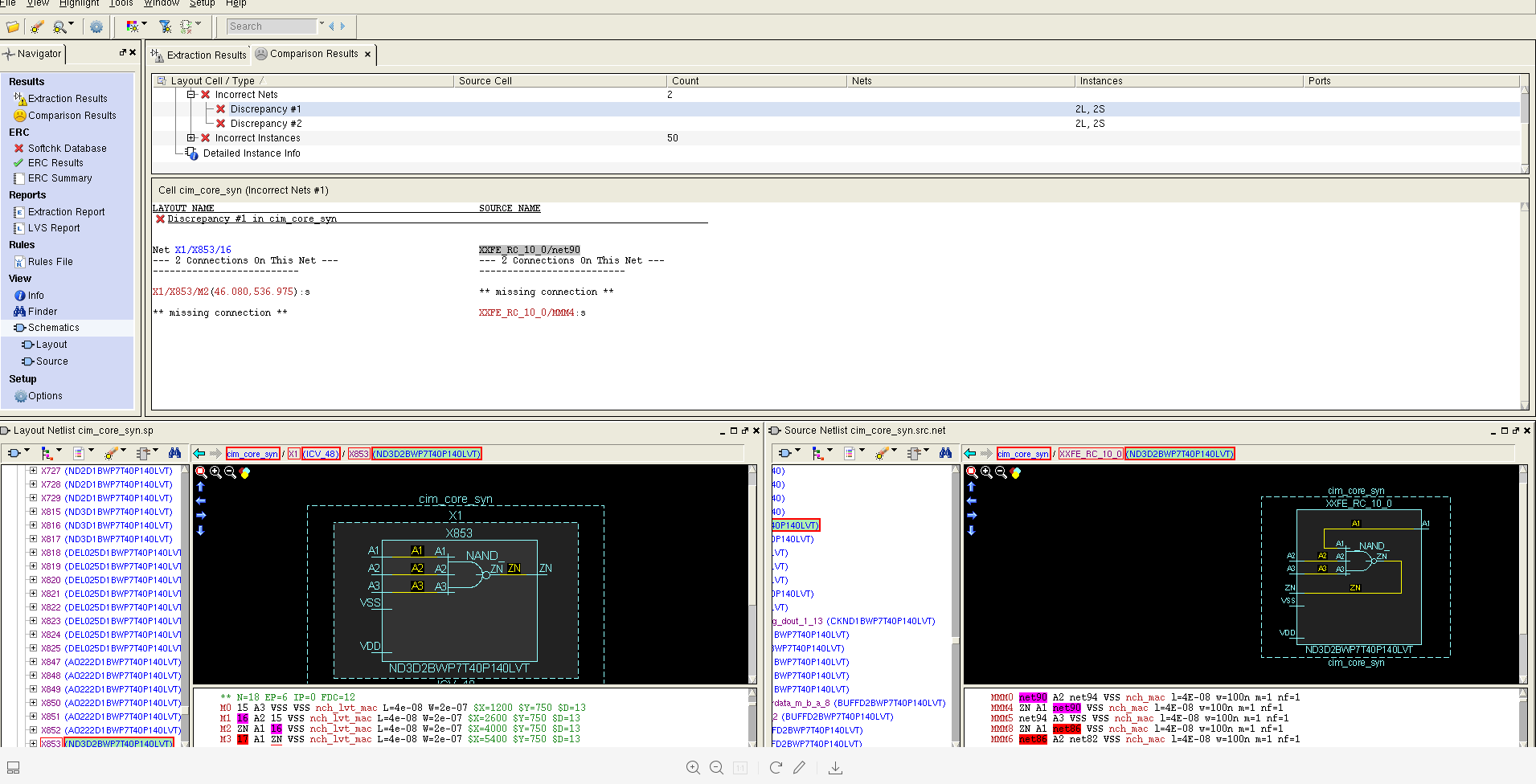

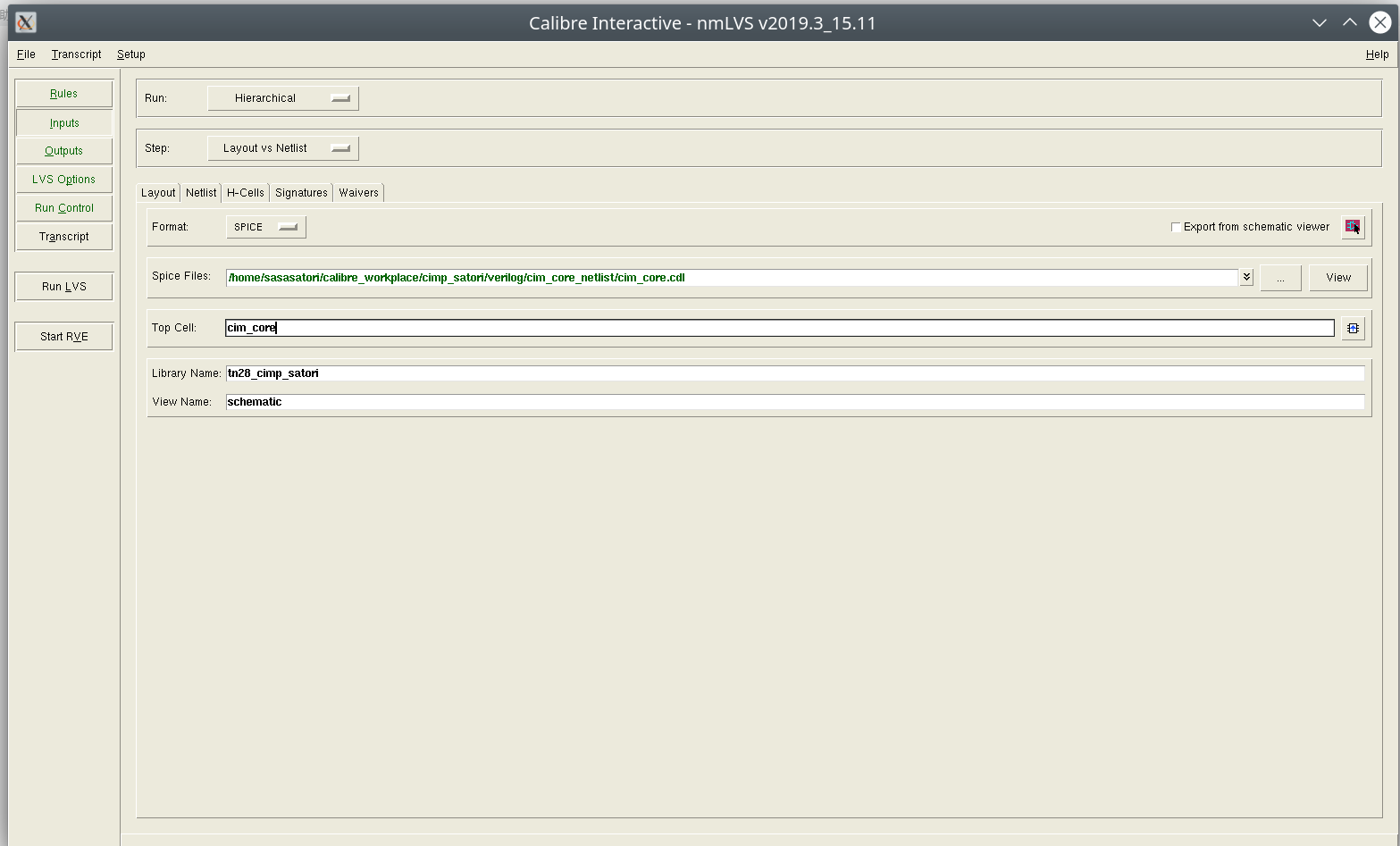

8. 大图LVS

与正常的LVS过程基本没有区别,主要在Inputs->Spice Files下选择上一步中merge好的大图cdl网表即可。

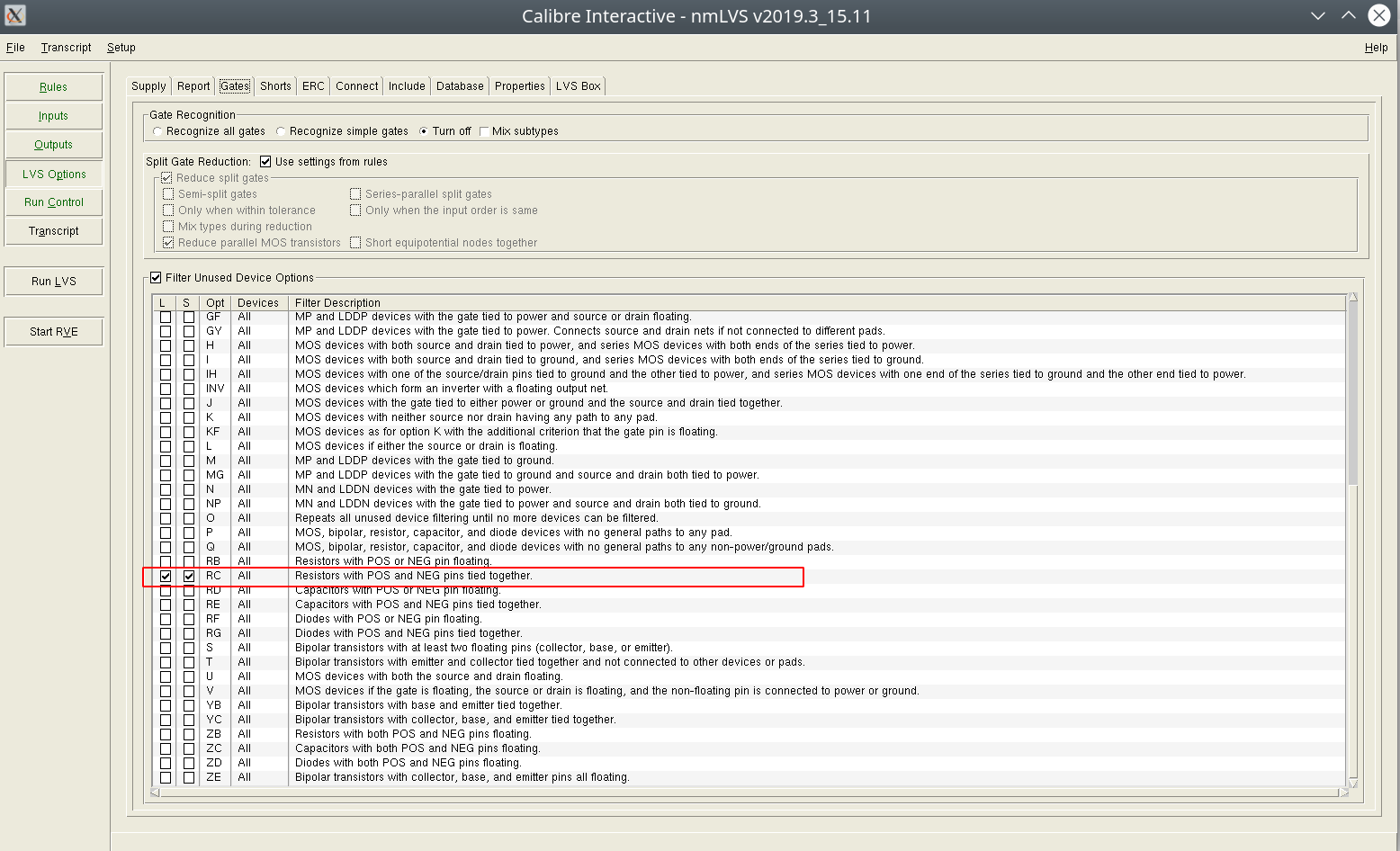

在LVS Options中可以进行一下设置,否则会因为dummy导致一些问题,参考下面这篇:

https://zhuanlan.zhihu.com/p/576365775

然后Run LVS,根据LVS的报告清理掉一些Port,Net的问题,最后clean就可以了。