1.1.4 Wilson电流镜

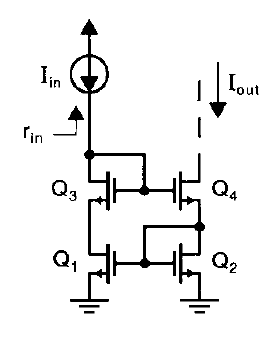

另一种高输出阻抗的电流镜是Wilson电流镜,如下图所示:

这是一个使用串联-分流反馈来提升输出阻抗的例子,\(Q_2\)获得输出电流将其镜像给\(I_{D1}\),其反过头来与\(I_{in}\)相减。注意\(I_{D1}\)必须精确等于\(I_{in}\),否则\(Q_3\)和\(Q_4\)的栅压将会增加或减少,负反馈就会强制使其相等(假定\(I_{out}\)突然增大,那么由于\(I_{D2}\)等于\(I_{out}\),\(V_{GS2}\)会增大,进而引起\(V_{GS1}\)的增大,但由于\(I_{D1}\)需要严格等于\(I_{in}\),因此\(V_{DS1}\)必须减小,进而使得\(V_{G3}\)下降,那么\(V_{GS4}\)也就会下降,从而\(I_{out}\)被抑制,完成了一个负反馈循环)。这种反馈结构将输出阻抗增大了1加回路增益倍。

运用反馈或者小信号模型分析,都可以推导出Wilson电流镜的输出阻抗在不考虑体效应的情况下为:

这个输出阻抗与Cascode基本一致。

关于输出电压摆幅,在\(Q_4\)进入线性区前,最小的输出电压是\(2V_{eff}+V_{tn}\),和Cascode电流镜一致。

最后,需要注意的是\(Q_3\)在Wilson电流源中实际上是可以不要的,它用来给予\(Q_1\)和\(Q_2\)相同的源漏偏置电压,从而最小化晶体管大信号输出阻抗导致的不精确。去掉这个晶体管,由于\(V_{DS1}\)比\(V_{DS2}\)更大,输出电流会稍微小于输入电流。然而小信号输出阻抗仍然保持一致。

写这一节时碰到的一个有趣的问题是在Johns&Martin的《Analog Integrated Circuit Design Edition 1》中,他使用反馈推导出来的\(r_{out}\)只有\((1.1.26)\)的一半,即\(r_{out}\approx g_{m4}r_{ds1}r_{ds4}/2\),而同样是改进型Wilson电流镜,Gray和Sansen的书里却是和\((1.1.26)\)一致。我去网上搜索了一些推导视频和国外大学的课件,发现也是挺乱套的,不管是用小信号分析还是用反馈分析的,有推出来一半的有推出来不是一半的。仔细分辨之后我发现推出一半的要么是存在计算错误,要么是小信号模型分析错了,要么是对反馈分析的有问题。而《Analog Integrated Circuit Design Edition 2》 中没有对Wilson电流镜的推导做出任何勘误,直接把这个结构从书中删去了,可能是作者认为Wilson电流镜相比Cascode没有什么优势,在工程中也并不常用吧。我自己主要参考了以下两个资料进行了一遍基于小信号模型的手推,得到的结果和\((1.1.26)\)一致。

Analog Circuit Lecture - 67 / MOSFET Wilson Current Mirror Output Resistance - YouTube

【新提醒】关于威尔逊电流镜的问题 - Analog/RF IC 设计讨论 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

还有一个使用反馈分析的参考: