1. 什么是SPI

SPI全拼Serial Peripheral interface(串行外围设备接口),是由Motorola(摩托罗拉)在MC68HCXX系列处理器上定义的,主要应用于EEPROM(带电可擦可编程只读存储器),FLASH,RTC(实时时钟),AD转换器,还有数字信号处理器和数字信号解码器。

SPI,是一种高速的,全双工,同步的通信总线,且只需要四根引脚线,与I2C一样都大大简化了PCB板子的布局空间,SPI依然是一种世界级的流行标准,大多数板子都内置了SPI的接口。

Motorola设计它的初衷也是为了节约排版空间。

2. SPI优与缺点

优点

- 支持全双工通信

- 通信简单

- 数据传输速率块

缺点

- 没有指定的读写方向控制

- 没有应答机制确认是否接收到数据

- 跟I2C总线协议比较在数据,可靠性上有一定的缺陷

3. SPI组成原理

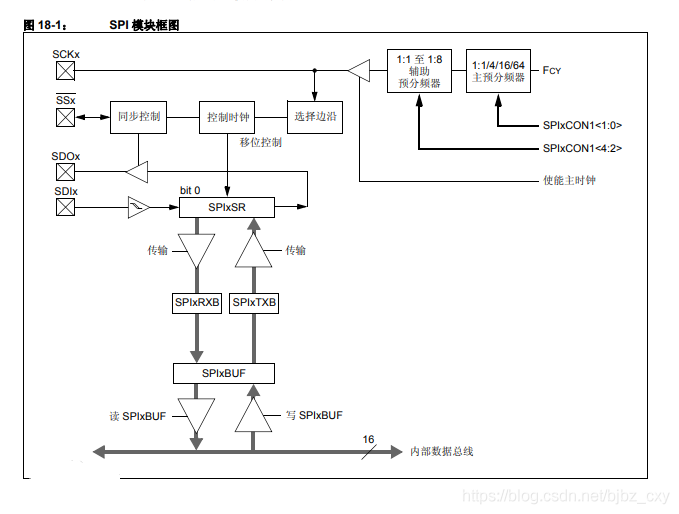

SPI模块框架图

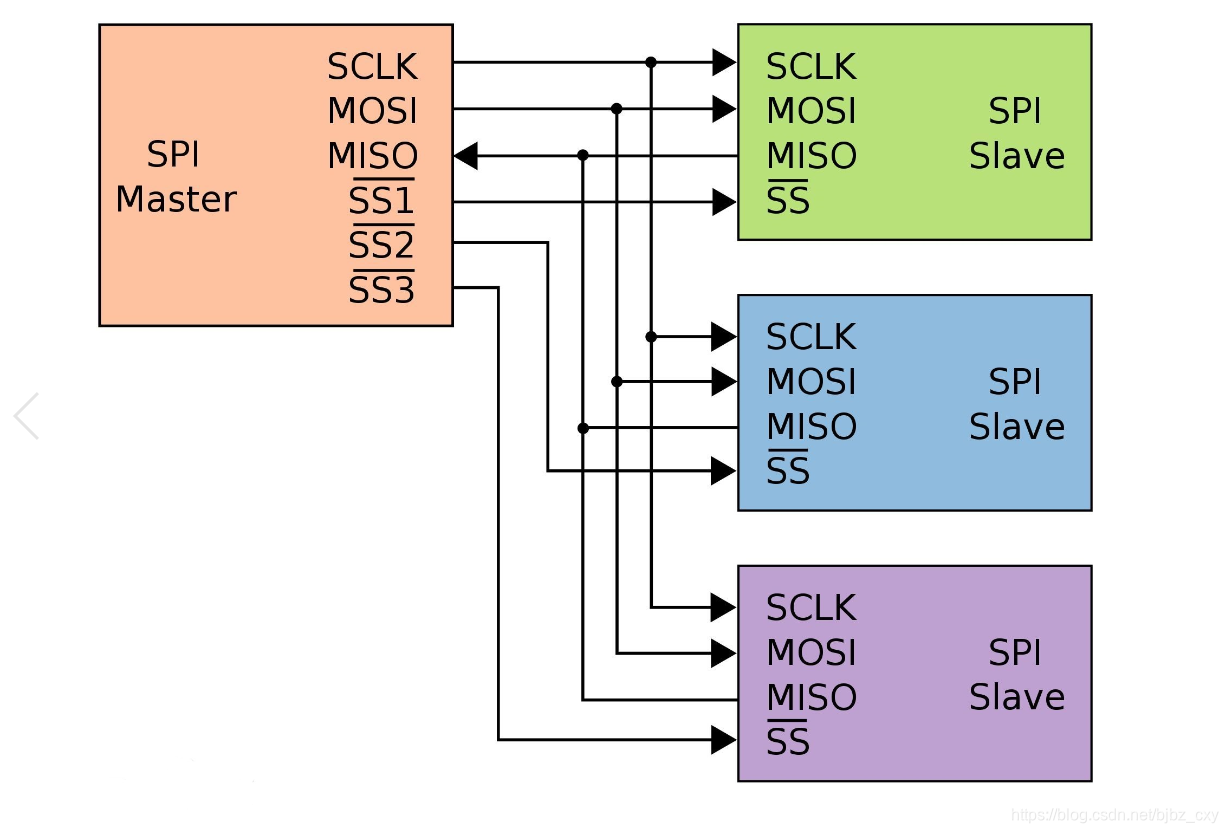

SPI结构

上图结构中的SCK、SS、MISO、MOSI是比较重要的几根线,其作用如下:

| 名称 | 作用 |

|---|---|

| SCK | 串行时钟信号,主设备产生 |

| SS | 片选线,主要用于发送片选CS信号,即选择从设备 |

| MISO | 主设备输入,从设备输出 |

| MOSI | 主设备输出,从设备输入 |

对于SS片选信号这里在多解释一下,在SPI中可能存在许多设备,但是只能有一个主设备,主设备通过SS线来控制选择哪个设备,默认情况下SS线是低电平状态,主设备通过选择连接在对应SS线下的设备,然后使其发送高电平,当连接在对应SS线上的设备收到高电平时就会做出响应,开始接收MISO或MOSI的数据,SS线会有多个,可以外接许多设备,SCK与MISO、MOSI只有一个,其它设备都接在上面。

其内部是有DR寄存器与位移寄存器,用来存数据与写数据

4. SPI通讯模式

SPI有四种通讯模式,分别是:

- Mode0

- Mode1

- Mode2

- Mode3

SPI官方没有给定名字,只给了模式0-3,其作用如下:

| 模式 | 作用 |

|---|---|

| Mode0 | SCLK输出数字信号0时处于空闲状态,SCLK输出数字信号为1时则代表有效状态 |

| Mode1 | SCLK输出数字信号0时处于空闲状态,SCLK输出数字信号为1时则代表有效状态,数据采样是在第2个边沿,数据发送在第1个边沿 |

| Mode2 | SCLK输出数字信号0时处于有效状态,SCLK输出数字信号1时处于空闲状态 |

| Mode3 | SCLK输出数字信号0时处于有效状态,SCLK输出数字信号1时处于空闲状态,数据采样是在第1个边沿,数据发送在第2个边沿 |

这些模式我们需要通过设置SCLK的”CPOL(时钟极性)和CPHA(时钟相位)”模式来完成,你可以把CPOL与CPHA理解为一个标志位,它们标志位不同会使SCLK的输出电平状态不同,也会改变数据输出的边沿

SPI工作模式与CPOL和CPHA的对应关系以及它俩的作用:

| 模式 | CPOL | CPHA |

|---|---|---|

| Mode0 | 0 | 0 |

| Mode1 | 0 | 1 |

| Mode2 | 1 | 0 |

| Mode3 | 1 | 1 |

边沿

这里说一下在SPI中什么是边沿,这里的第1个边沿与第2个边沿表示的是电平变化

边沿表示的是上升沿或下降沿

上升沿:即在一定周期时由低电平变化到高电平,然后此时在进行数据采样,即电平信号到数字信号转换

下降沿:即在一定周期时由高电平变化到低电平,然后此时在进行数据采样,即电平信号到数字信号转换

CPOL

用来决定SCL空闲时应该是怎样的电平状态,若为0,SCLK空闲时输出低电平,若为1空闲时输出高电平

CPHA

它用来表示该MOSI有效还是MISO有效,若它的值为0则代表第0个边沿数据采样,即MOSI上可以进行数据采样,若它为1时则MISO数据可以进行采样

同时它与CPOL是关联的:

若CPHA为0,CPOL为0时:

若CPOL为0,则第一个边沿有效,即SCLK空闲时是低电平,那么边沿就等于上升沿,同时MOSI输出信号,MISO可以采样了

若CPHA为0,CPOL为1时:

若CPOL为1,则第一个边沿有效,即SCLK空闲时是高电平,那么边沿就等于下降沿,同时MISO输出信号,MOSI可以采样了

MOSI与MISO线对主设备和从设备方向不同,MOSI线在主设备上是输出,从设备上是输入,所以它们是相反的,所以当MOSI输出信号时,对于从设备来说,它就可以读数据了所以主设备与从设备两根线MISO与MOSI两根线作用是不一样的,所以上面的状态对于不同的设备是相反的,也就是刚好实现了主设备写时,从设备读,主设备读时,从设备写,采样意思是设备可以去某个线上去读数据了

SPI是没有控制信号的,只能通过SCLK时钟的状态来告诉从设备现在的流方向,从设备需要实时检测当前的SCLK状态

工作时需要保证从设备与主设备一致的工作模式,其次许多从设备在出厂时就已经设定好了工作模式,是无法修改的,有些从设备是可以修改的。

5. 通讯过程

- 首先拉高对应设备的SS线,选择对应的从设备

- 通过SLCk产生时钟边沿变化,来告诉从设备读写

- 主设备里的控制逻辑通过位移寄存器从高到低的方式移动给MOSI总线上

- 从设备接收到之后也通过位移寄存器的方式按照顺序移到DR寄存器中

- 这里给大家看一下SCLK产生时钟周期时做了什么

- 如下图,当SCLK周期开始变成低电平时则代表数据有输出了,当变成高电平时则代表数据可以采样(读)了,即输出→输出完成,这是整个周期做的事情,下位机只需要等待周期变化完成之后根据当前模式去到指定的线上读或写数据就可以了

- SPI是双向的,主机发的时候一样可以收从机的数据,在一个周期里完成数据交换,但是只有一个DR寄存器,所以SPI的方法是位移,主机高到低,从机低到高的交换,当主机高位移出去,低位就空一个出来,而从机低位移出一位,高位就空出一位

* *

*

在通讯之前需要保证双方时钟频率是一致的,一般情况下从设备是无法修改时钟频率的,只有主设备能够修改时钟频率,将主设备的时钟频率修改与从设备一致,默认情况下是不需要修改这些的,这个可以根据芯片手册中SPI上的使能时钟接的是谁,如果提供了GPIO口进行修改那么就支持可编程时钟,若没有则代表当前的MCU不支持编程SPI的时钟频率

原文链接:https://blog.csdn.net/bjbz_cxy/article/details/119925257