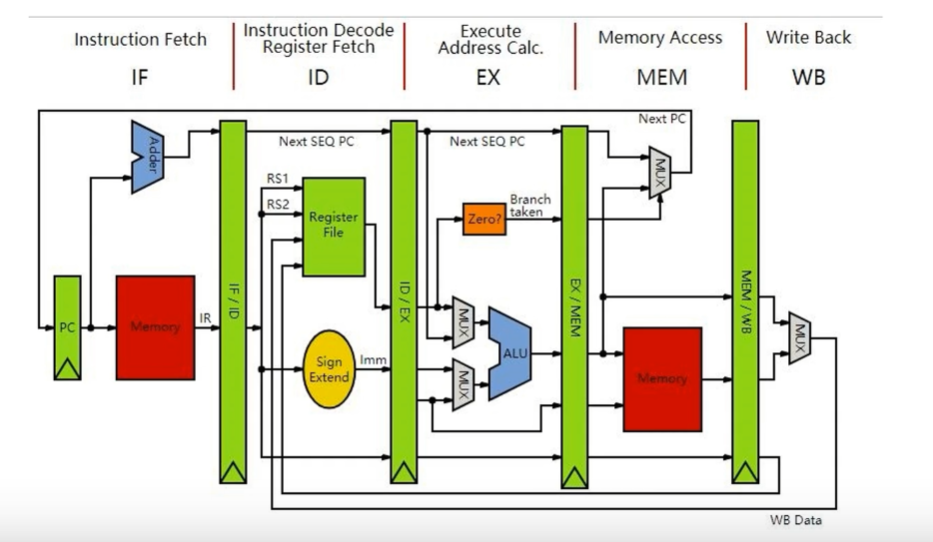

riscv实际上是一种ISA的指令集,而处理器的设计的基本结构是不变的(如下所示),其区别在于所选用的指令集的类型,一般有ARM、RISCV、MIPS等,采用了不同的引擎,那么车的外观、系统等也会随之发生变化。

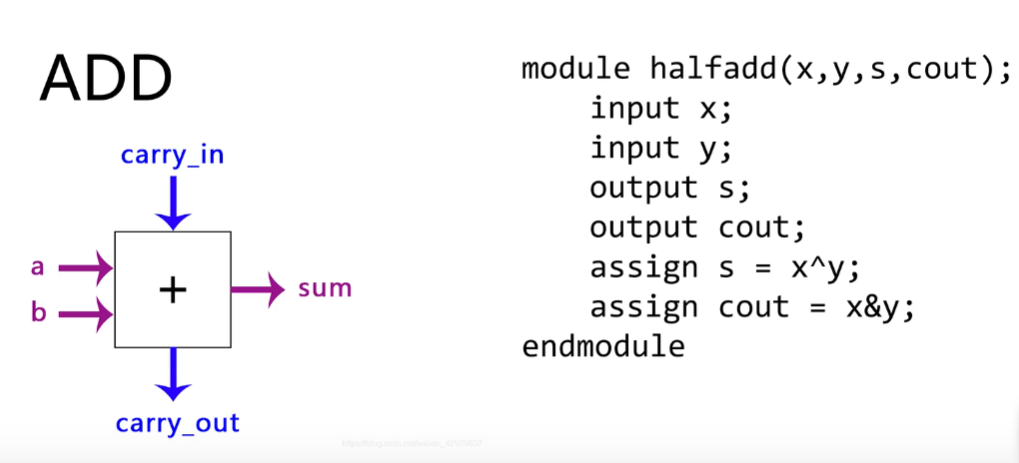

采用RISCV,是因为它简洁、开源、明了,确定处理器设计的指令集后,我们还要对其进行硬件设计,因为指令又不是虚空的,不可能凭空就执行某一项操作,例如我们要进行加法运算,那就必须要有一个加法器来实现,而加法器的实现,就需要用到我们之前所学的硬件描述语言。

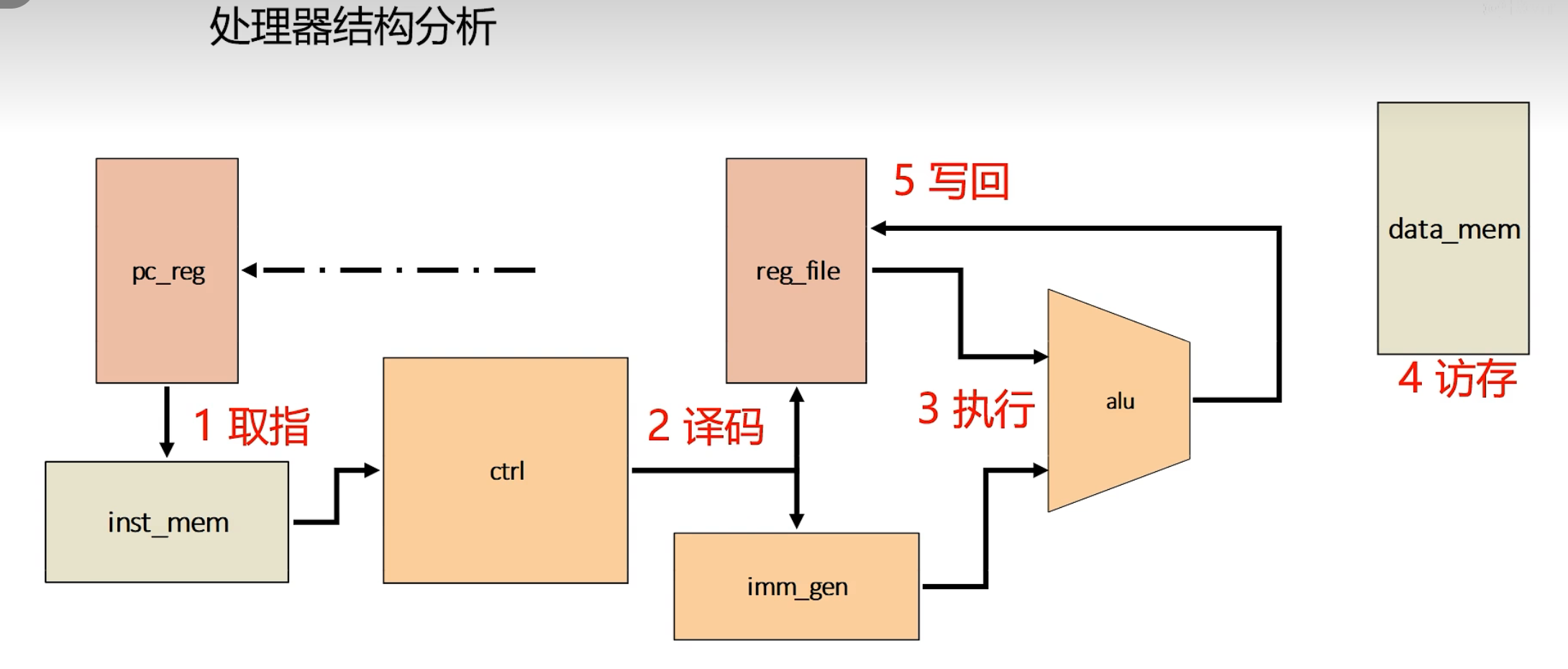

要设计一款处理器,最重要是理解处理器的结构,同时理解每一个模块的作用,因此,本项目设计的处理器是单周期、单指令(add)的非常简单的处理器。

开始设计处理器之前,首先对指令集进行讲解:RV32/64代表它是32位/64位的指令集,后面加上的IEMFDACQ代表每一种模块,其中RV32I是最简单、最基本的整数指令集,

之前我们说的,设计的处理器只是单指令(add)的,而要通过add的指令测试,我们其实需要总共设计五个指令,分别是:

1.ADD:R型,寄存器加法,将两个寄存器值相加;

2.ADDI:I型,立即数加法,将一个寄存器值和一个立即数相加;

3.BNE:B型,分支跳转,如果两个数不相等则进行一个指令的跳转;

4.JAL:J型,跳转和链接,跳转指令,同时将下一个指令的地址存储下来;

5.LUI:U型,高位立即数加载,将一个立即数作为高位存在寄存器中。

在了解了指令后,我们需要了解处理器的结构,RISCV处理器是典型的哈弗结构:特征是指令存储和数据存储分离

该项目实现的处理器结构如下:

其中:

1.inst_mem和data_mem分别代表指令存储器和数据存储器,由于该项目没有设计数据的存储,因此data_mem暂时没有用上;

2.pc_reg:决定读哪一条指令;

3.ctrl:分析指令,进行译码;给其他模块提供控制信号、地址信号和立即数值;

4.reg_file:存储器堆;

5.imm_gen:立即数扩展;从指令中取出的立即数不能直接用,需要根据指令结构的不同扩展为不同的32位立即数值,这个才是我们真正运算的数;

6.ALU(arithmetic and logic unit):运算模块,使用寄存器值和立即数值进行相应的算数运算;

5.由于不涉及数据存储,因此ALU计算结果会写会寄存器堆中;

6.运算结束后还会有一些信号流回pc_reg中,从而确定下一条执行的指令。