3.4.3 低压降稳压器

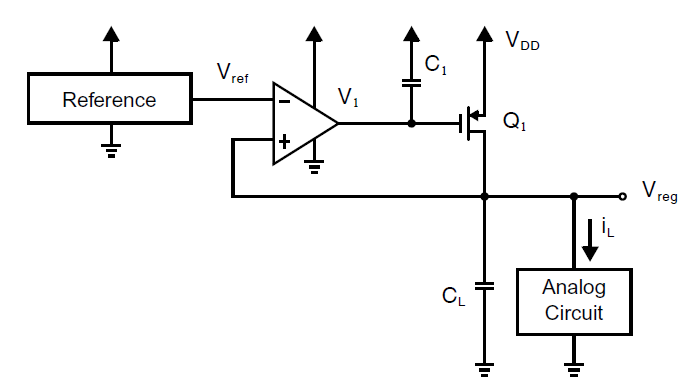

当稳压器输出必须要仅比\(V_{DD}\)低\(200-400mV\),并且无法低阈值电压(\(V_t\)接近零)的NMOS器件时,有必要使用一个PMOS器件作为\(Q_1\)。如下图所示,在这个例子中,栅电压\(V_1\)低于\(V_{DD}\),稳压器压只受到\(V_{eff,1}\)限制,这个电路被称为低压降稳压器(LDO),是电路能效比较关键时的一个常见选择。注意放大器的极性与之前的NMOS电路相反,因为现在从\(V_1\)到\(V_{reg}\)是一个负的小信号增益。由于与之前的电路相比,从\(Q_1\)看入的阻抗从\(1/g_{m,1}\)增大到了\(r_{ds,1}\),环路增益也增大了\(g_{m,1}r_{ds,1}\)倍,稳压器的闭环输出阻抗基本不变。

使用PMOS的一个缺点是其降低了电源抑制比,当一个小信号施加在\(V_{DD}\)上时,\(Q_1\)作为表现为一个共栅放大器,其增益很可观。在低频下,闭环环路能够跟踪并抵消\(V_{reg}\)上的变化,在高频处偏差可以被\(C_L\)滤除,但在中频处很难在LDO上实现一个好的电源抑制比。

LDO的闭环分析近似于一个两级放大器,其中上图中使用的放大器被认为只有一个增益级,而导通晶体管\(Q_1\)构成一个共源放大器作为第二级。忽略掉\(C_{gd1}\),显然系统开环频率响应中存在两个极点。

放大器输出的极点(\(Q_1\)的栅极)为:

其中\(C_1^{'}=C_1+C_{gs1}\),LDO输出处的极点为:

与之前一样,任意一个极点都可以用于主极点补偿,使用输出处极点作为主极点,即\(\omega_{pL}<<\omega_{pa}\)需要放大器有更高的功耗来使得\(R_{oa}\)降低,但好处是在中频处提供了一个低的输出阻抗使得电源抑制比能够有所改进。这在LDO中非常重要,因为如上所述,PMOS导通晶体管在中频处会起到放大噪声的作用。

例题1:

本节中的LDO的电源抑制比为多少?

解答:

下图的小信号等效电路在\(V_{DD}\)处增加了一个小信号源,当环路断开时,从\(v_{dd}\)到\(v_{reg}\)的响应可以简化视作一个以\(R_L||(1/sC_L)\)为负载的共栅放大器。

当环路闭环后,一阶低通响应会再乘以闭环整形因子\(1/(1+L(s))\),得到的从电源到输出的小信号频率响应是电源抑制比的导数,即:

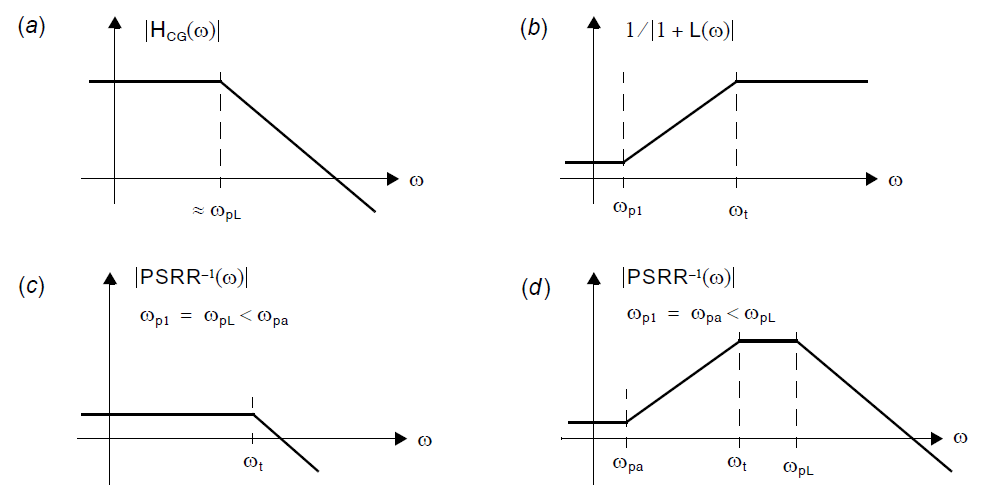

下图的频率响应图分别为(a) 电源抑制比的开环响应,(b) 闭环整形因子,(c) \(\omega_{pL}<\omega_{pa}\)时电源抑制比倒数的频率响应,(d) \(\omega_{pL}>\omega_{pa}\)时电源抑制比倒数的频率响应。在(c)(d)两种情况下,电源抑制比的倒数都可以表示为:

如果环路增益在越过其主极点频率\(\omega_{p1}\)后仍旧增长,电源抑制比会恶化。在(c)情况中,这在输出极点开始滤除电源噪声的同时发生,因此电源抑制比仍然很大。在(d)情况中,放大器极点\(\omega_{pa}\)首先出现在负载电容还不能够滤除电源噪声的频点上,因此电源抑制比持续恶化,直到负载极点开始发挥作用。不幸的是,为了稳定性,极点\(\omega_{pa}\)和\(\omega_{pL}\)必须放置的间隔很远,因此这个恶化情况非常显著。这种情况一般发生在几百MHz的频段,此时由于数字电路引发的电源噪声可能非常高,因此成为了一个主要的挑战。