分析:

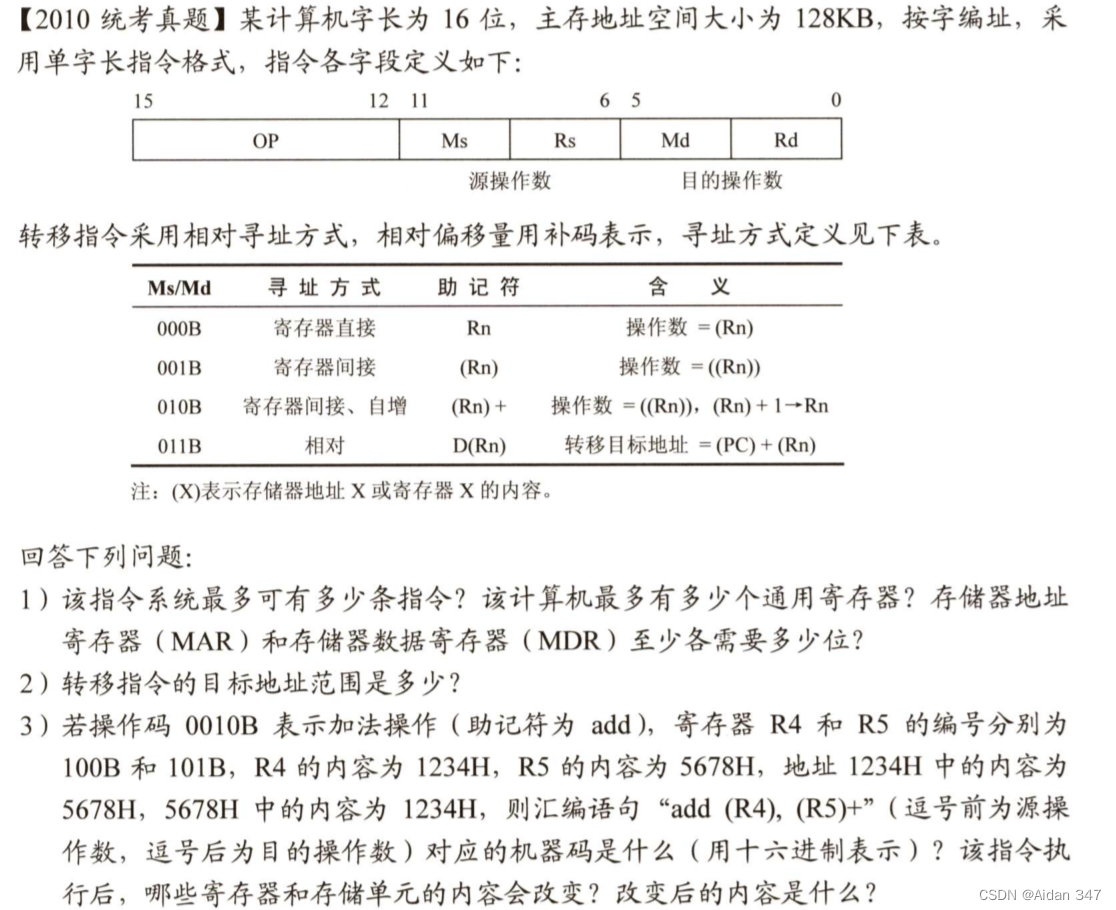

- 由题目可知操作码占4位,所以支持的操作指令为\(2^4\)种指令

- 操作数占6位,其中寻址3位,寄存器编号3位,所以最多有\(2^3\)个通用寄存器

- 主存大小为128KB,机器字长为16位,且按字编址,所以有\(\frac{128KB}{2B} \quad = 2^{16}\)个存储单元,即MAR至少16位

- 机器字长为16为,那么MDR至少也是16位

- 存器字长为16 位,PC 可表示的地址范围为\([0, 2^{16}-1]\),Rn可表示的相对偏移量为\([-2^{15} ,2^{15}-1]\),而主存地址空间为\(2^{16}\),因此转移指令的目标地址范围为[0000H, FFFH]\(([0, 2^{16}-1])\)

- add:0010,寄存器间接寻址:001,R4:100,寄存器间接寻址且自增:010,R5:101,0010 0011 0001 0101B = 2315H

- 指令的功能是将 R4 的内容所指的存储单元的数据与 R5的内容所指的存储单元的数据相 加,并将结果送入 R5的内容所指的存储单元中。(R4)=1234H,(1234H)=5678H;(R5)= 5678H,(5678H)=1234H;执行加法操作5678H+1234H=68ACH。之后R5自增;

该指令执行后,R5和存储单元5678H的内容会改变,R5的内容从5678H变为5679H,存 储单元 5678H中的内容变为该指令的计算结果68ACH

分析:

1.由题意,执行周期内有间址和执行指令两种微操作

2.\(C_1到C_4为取指令和指令译码,C_5到C_7为间址,C_8到C_{10}为执行阶段\)

\[\begin{array}{c|c|c}

时钟&功能&有效控制信号\\

\hline C_1&(PC)->MAR&PC_{out},MAR_{in}\\

\hline C_2&(MAR)->MDR,PC + 1&MDR_{in},MemR,PC + 1\\

\hline C_3&MDR->IR&MDR_{out}, IR_{in}\\

\hline C_4&指令译码&--\\

\hline C_5&(R_1)->MAR&R1_{out},MAR_{in}\\

\hline C_6&M(MAR)->MDR&MemR,MDR_{in}E\\

\hline C_7&M(MDR)->A&MDR_{out},A_{in}\\

\hline C_8&(A) + (R_1)->AC&R0_{out},AC_{in},CU向ALU发送ADD信号\\

\hline C_9&(AC)->MDR&AC_{out},MDR_{in}\\

\hline C_{10}&(MDR)->M(MAR)&MDR_{out},MemW

\end{array}

\]