引言

处理器的实现方式决定了时钟周期长度和CPI。实现方式有单周期与流水线,本篇谈谈单周期处理器。

目前CPU的频率一般是3GHZ/4GHZ,但是频率是有极限值的,受cycletime影响

基本的RISC-V实现

- 存储指令:ld,sd

- 算术逻辑指令 :add ,sub,and,or

- 条件分支指令:beq

实现每条指令的前两个步骤是一样的:

- 程序计数器发送到指令所在的存储单元,并从其中取出指令

- 根据指令的某些字段选择要读的一个或两个寄存器

所有类型的指令在读取后都用ALU(存储器访问,算术逻辑,条件分支比较)

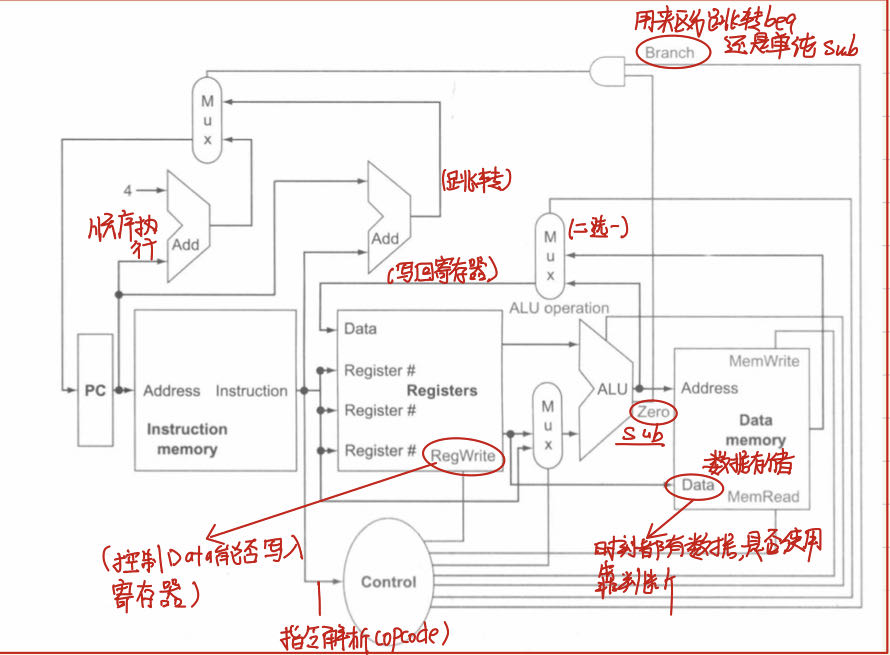

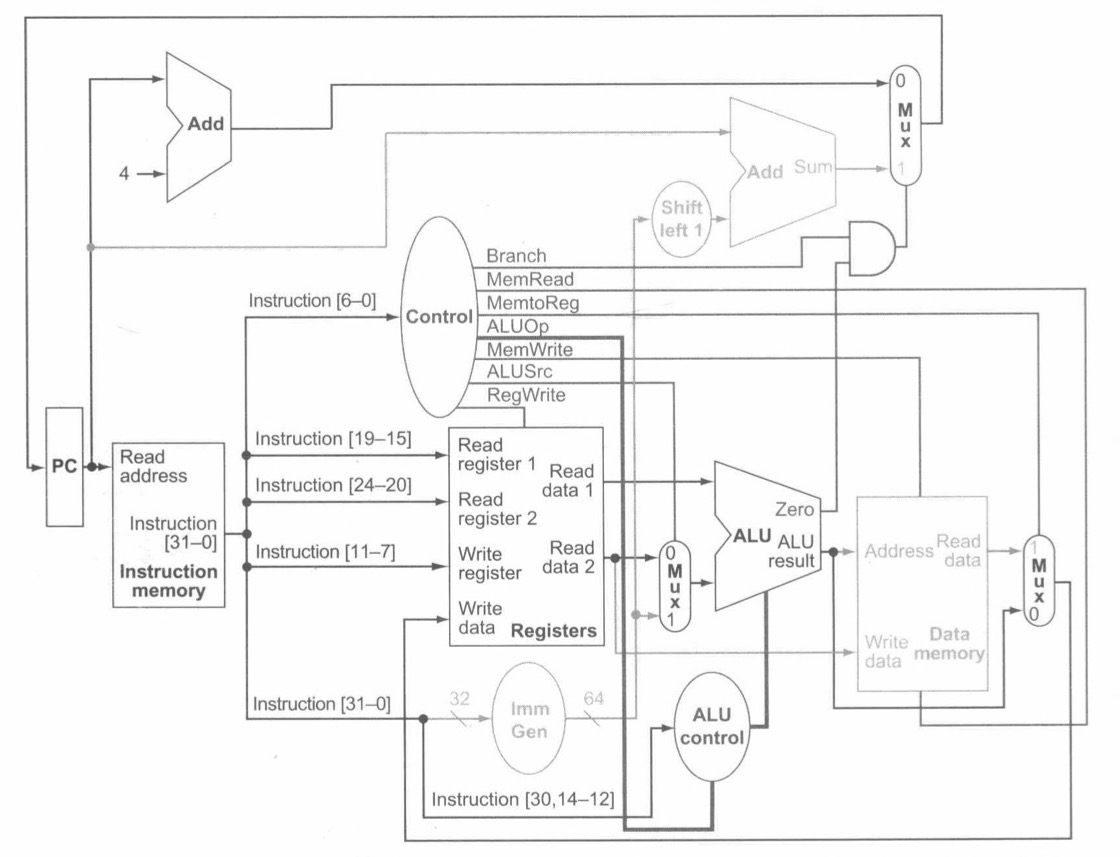

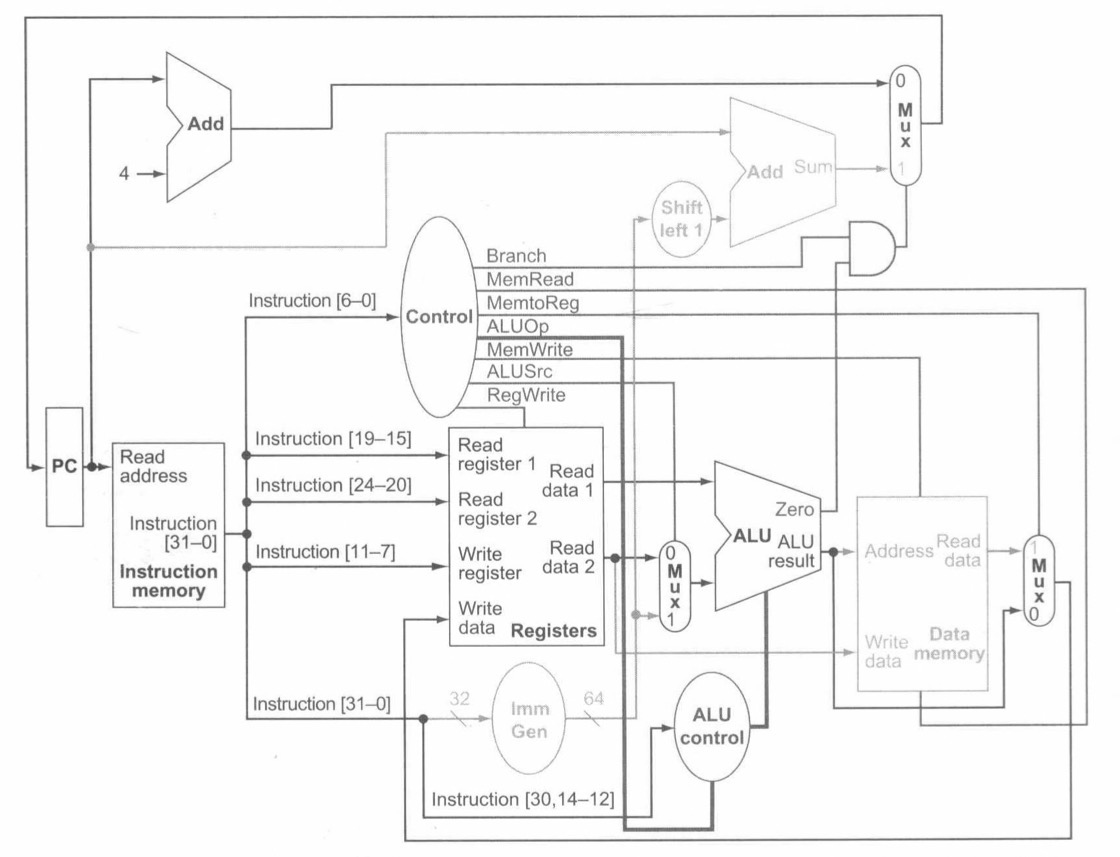

单周期CPU概览

流程介绍

所有的指令都用程序计数器获得指令在指令存储器中的地址。

- 取到指令后,指令的对应字段知道要使用的寄存器操作数。

- 寄存器操作数一被取出,即可用于计算存储器地址(load指令或store指令)、计算算术运算结果(定点算术逻辑指令)或进行相等检验(分支指令)。

- 如果是算术指令,ALU的结果要写回寄存器。

- 如果是存取操作,ALU的结果黄作为存储器地址以及存储来自寄存器的值,或将存储器数据加载到寄存器中。

- 对于分支指令ALU的输出来觉得下一条指令的地址,这个地址可能来自PC和分支偏量相加的加法器,也可能来自PC+4的加法器。

时钟同步方法

一般用边沿触发来到达时钟同步的目的。这也决定了要在一个时钟周期内读出寄存器的值。

建立数据通路

数据通路单元

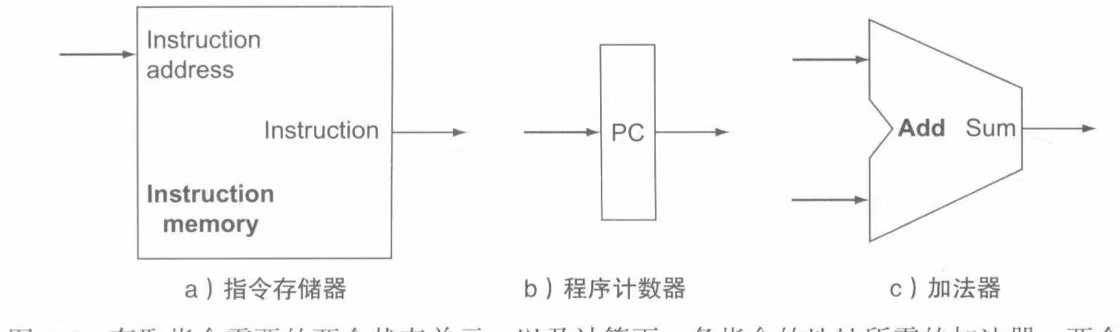

数据通路单元是一个用来操作或保存处理器中数据的单元。在RISC-V实现中,数据通路单元包括指令存储器、数据存储器、ALU和加法器。

如果一个单元内部有存储功能,它就包含状态,称为状态单元

程序计数器

包含当前程序正在执行指令地址的寄存器,是一个64位的寄存器,在每个周期结束后被写入。

存储单元

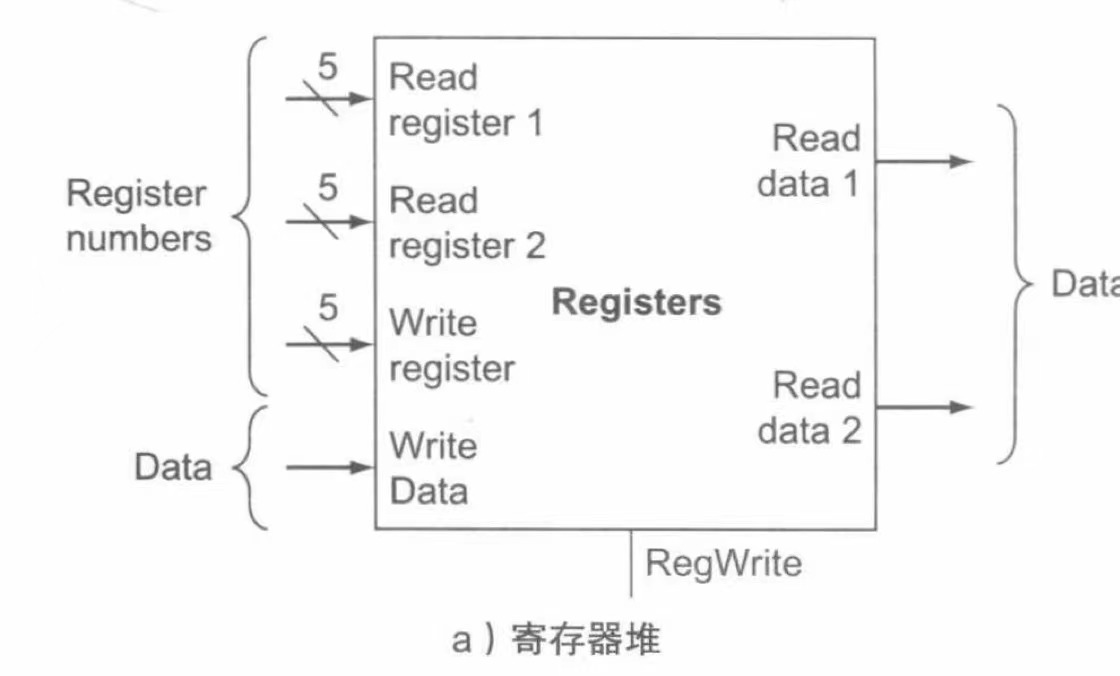

寄存器堆

处理器的32个通用寄存器位于寄存器堆(register-file)的结构中

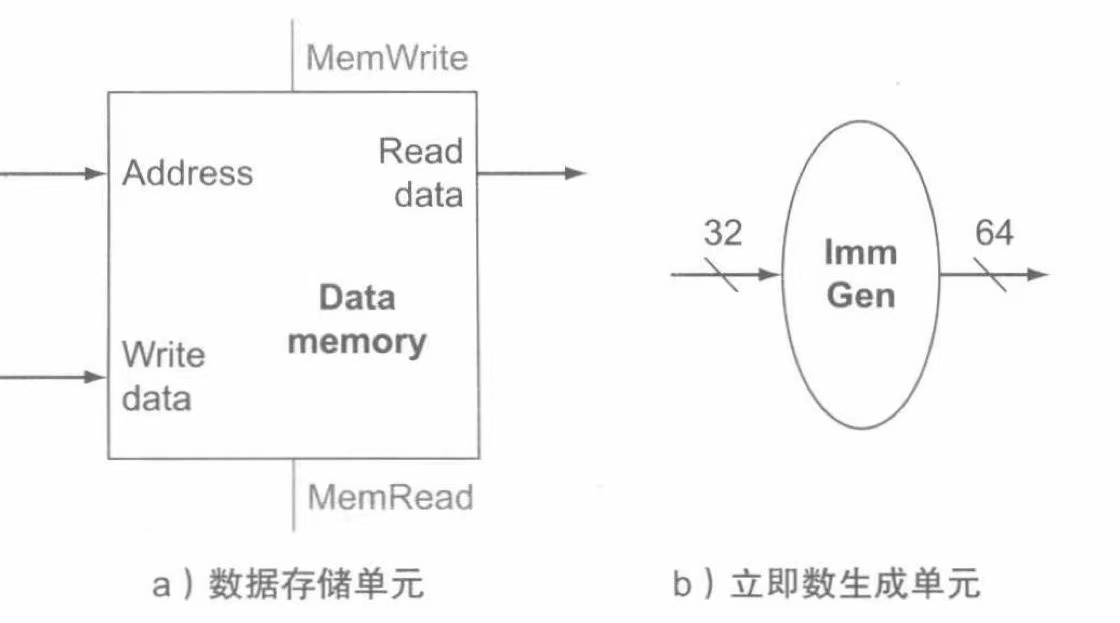

数据存储单元

读写信号是相互独立的,但仅有一个可以在任意给定的时钟上有效

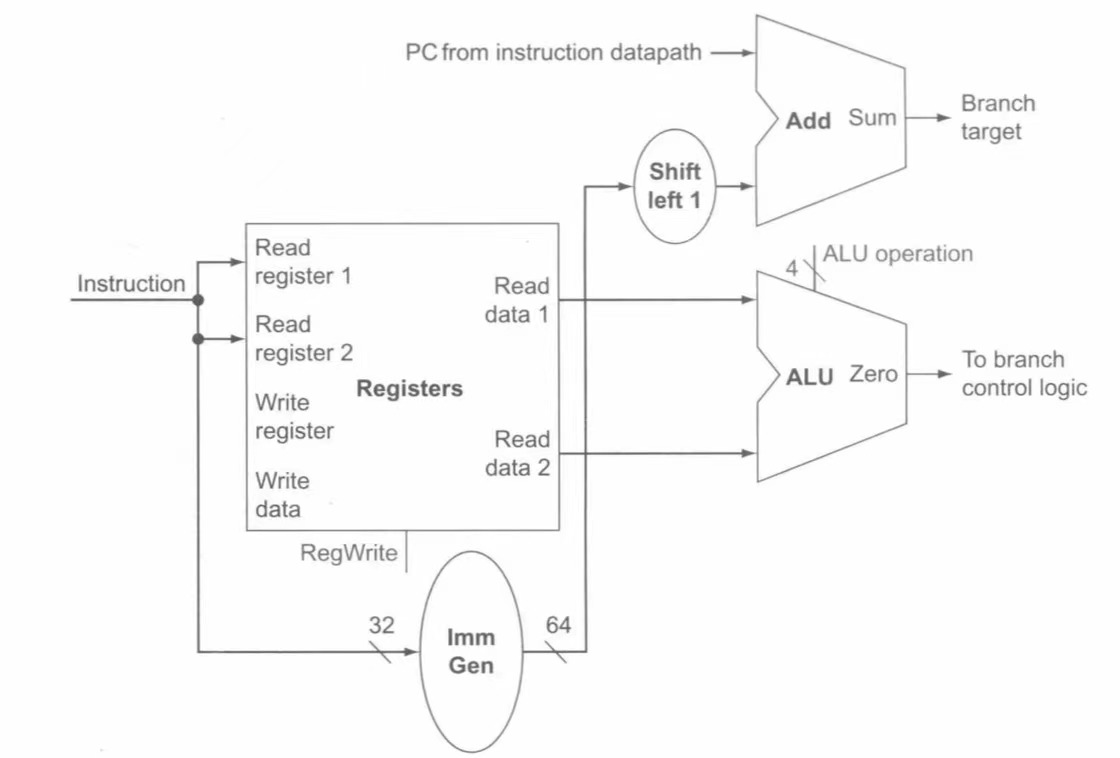

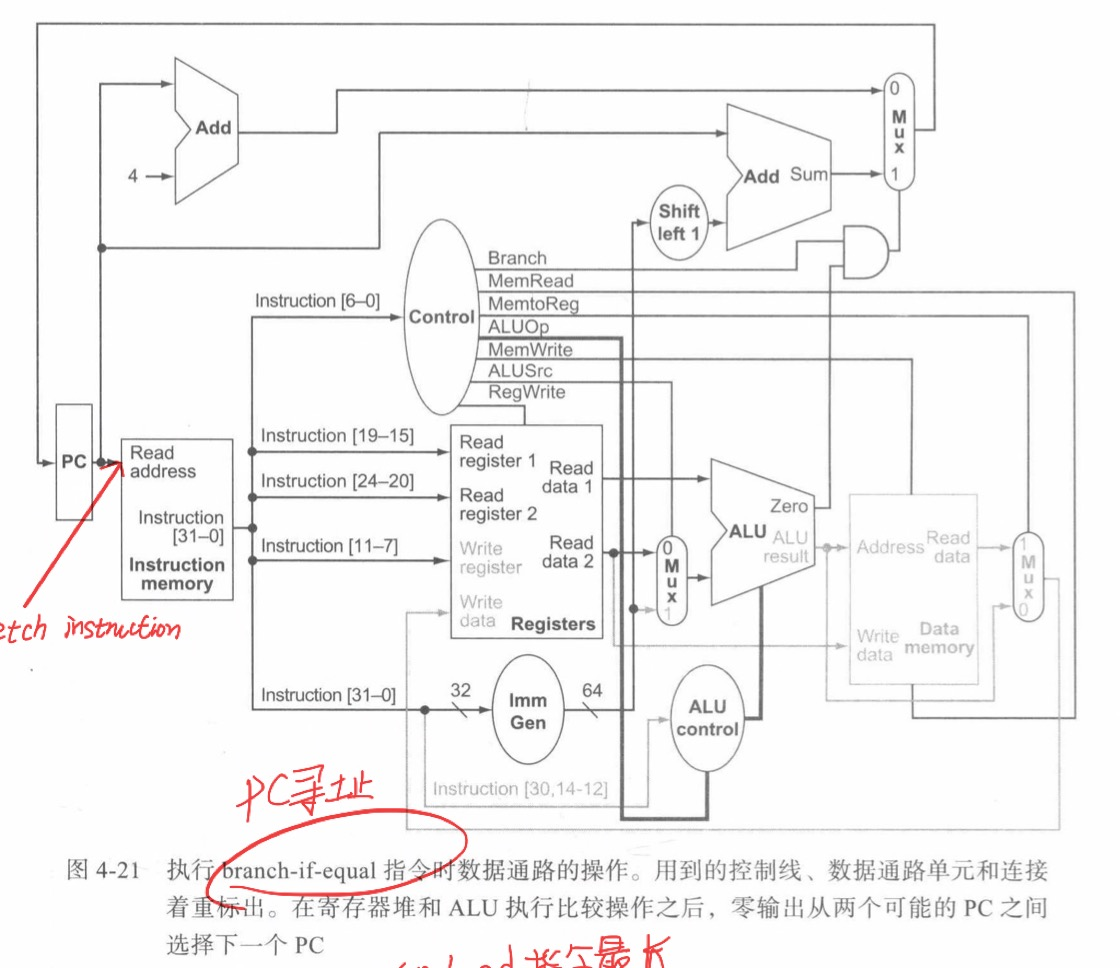

为实现beq指令,需要将PC值与符号扩展后的指令偏移量相加得到分支地址

分支指令

- 指令系统结构规定了计算分支目标地址的基址分支是所在地址

- 将偏移量左移以为以表示板子为单位的偏移量,这样的偏移有效范围扩大两位

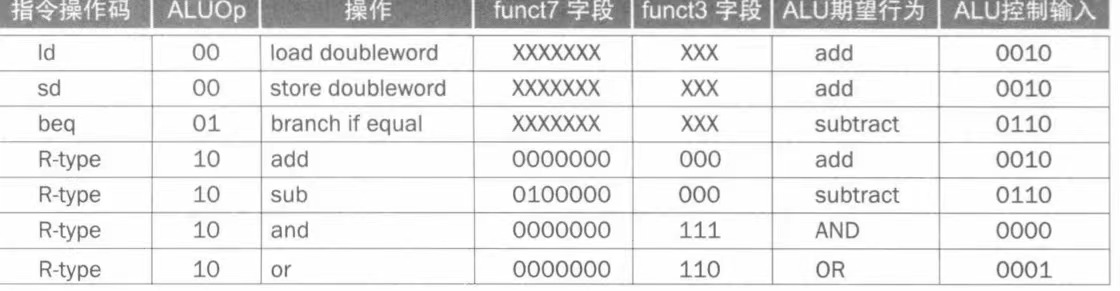

ALU控制

”load/store = add“ “branch = sub" "R type ~ depend on opcode"

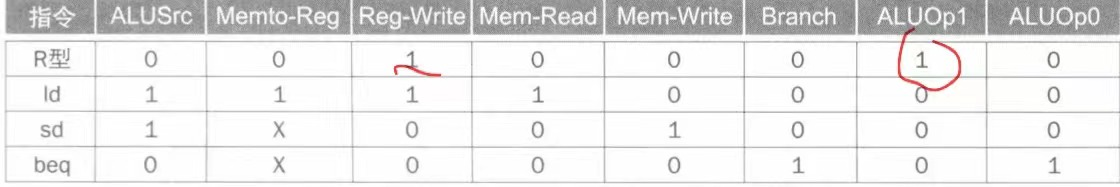

控制信号

数据通路操作

R型

- 取出指令,PC自增

- 从寄存器堆读两个寄存器,对从寄存器堆读出的数据进行操作

- 根据部分操作码确定ALU的功能,对寄存器堆读出的数据进行操作

- 将ALU的结果写入寄存器堆中的目标寄存器

load指令

步骤:

- 从指令存储器中取出指令,PC自增

- 从寄存器堆中读出对应一个寄存器的值

- ALU将从寄存器堆中读出的值和符号扩展后的12位(偏移量)相加

- 将ALU的结果用作数据存储器的地址

- 将从寄存器读出的数据写入寄存器堆

beq指令

- 从指令存储器中取出指令,PC自增

- 从寄存器堆中读出两个寄存器x1和x2

- ALU将寄存器堆读出的两数相减。PC与左移一位、符号扩展的指令中的12位相加,结果是分支目标地址

- ALU的零数超出决定将哪个加法器的结果写入PC

本文由博客一文多发平台 OpenWrite 发布!