Cache与主存讨论

Cache与主存的性质区别实际上就是SRAM与DRAM的不同。

SRAM用于Cache,DRAM用于主存

结构

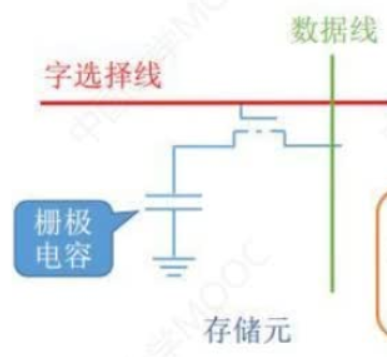

DRAM的存储元结构(栅极电容):

写入:当MOS管接通后,给电容输入电荷或不输入电荷就对应了1和0两个信息;

读出:当MOS管接通后,数据线产生电流=1,数据线无电流=0;

特性:

- 读出的时候会导致电荷流失也就是信息丢失;

- 电容会自发移动电荷,导致信息丢失;

- 单位体积小,集成度高;

- 造价偏低

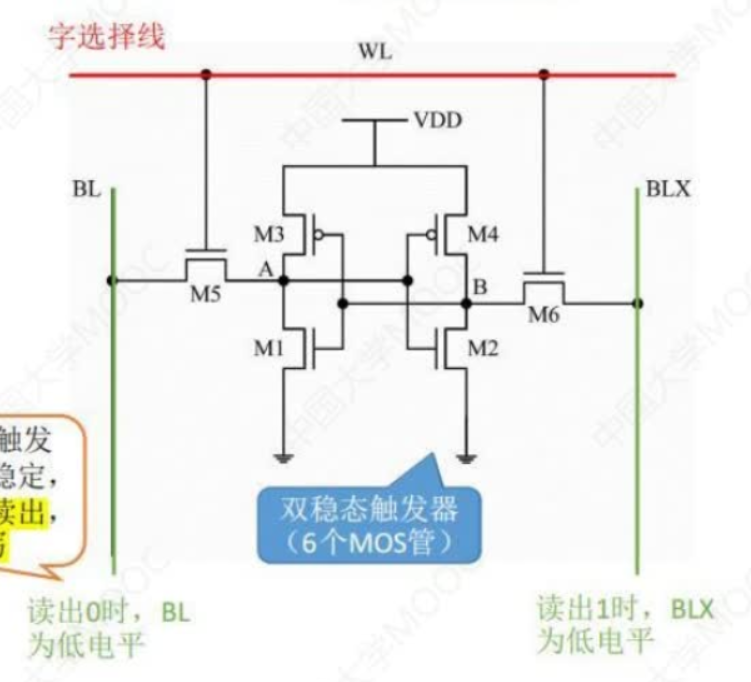

SRAM的存储元结构(双稳态触发器):

写入,读出:不了解

特性:

- 读出不会导致信息丢失

- 状态稳定,不会自发丢失信息

- 单位体积大,集成度低

- 造价偏高

特性对比

我们都知道Cache对于主存而言,读写速度快,容量小,造价高,从结构特性便可以解释:

- 主存所采用的DRAM在读出后会信息丢失(破坏性读出),因此需要重写信息,并且其会自发得丢失信息,因此需要刷新操作。而Cache所采用的SRAM是状态稳定的,无需上述操作,因此Cache消耗的时间比主存少,也就读写速度更快了。

- 由于DRAM集成度比SRAM高,因此单位面积内能集成更多存储元;故主存容量比Cache大。

- 单个存储元中,SRAM所使用的电子元件比DRAM多许多,因此造价更高,这也导致了Cache比较贵。

主存的深入探究

上述提到了DRAM的重写,刷新等,其实主存还有更多内容需要了解,以下将采取从细到广的视角探究。

DRAM的重写

重写就是DRAM在读出后需要一段时间重新写入信息,保持信息不被破坏。

DRAM的刷新

为了解决由于电容特性导致的信息流失,我们需要对DRAM进行刷新,就是重新写入信息。也引出了如下几个问题:

-

多久刷新一次?答:刷新周期一般为2ms

-

怎么刷新?答:有硬件支持,读出信息后重新写入,需要一个读/写周期

-

每次刷新多少存储单元?答:这个后面说

-

在什么时刻刷新?假设计算机读/写周期为0.5us,答:

-

分散刷新:每次读/写都顺便刷新,因此计算机存取周期为2个读写周期,即1us

-

集中刷新:上面提到刷新周期是2ms,因此在2ms内集中安排一段时间进行刷新,此时称为访存“死区”

-

异步刷新:假设需要128次刷新请求,将其分散在2ms内,因此每(2ms/128)=15.6us内就有0.5us的“死区”

-

存储器芯片

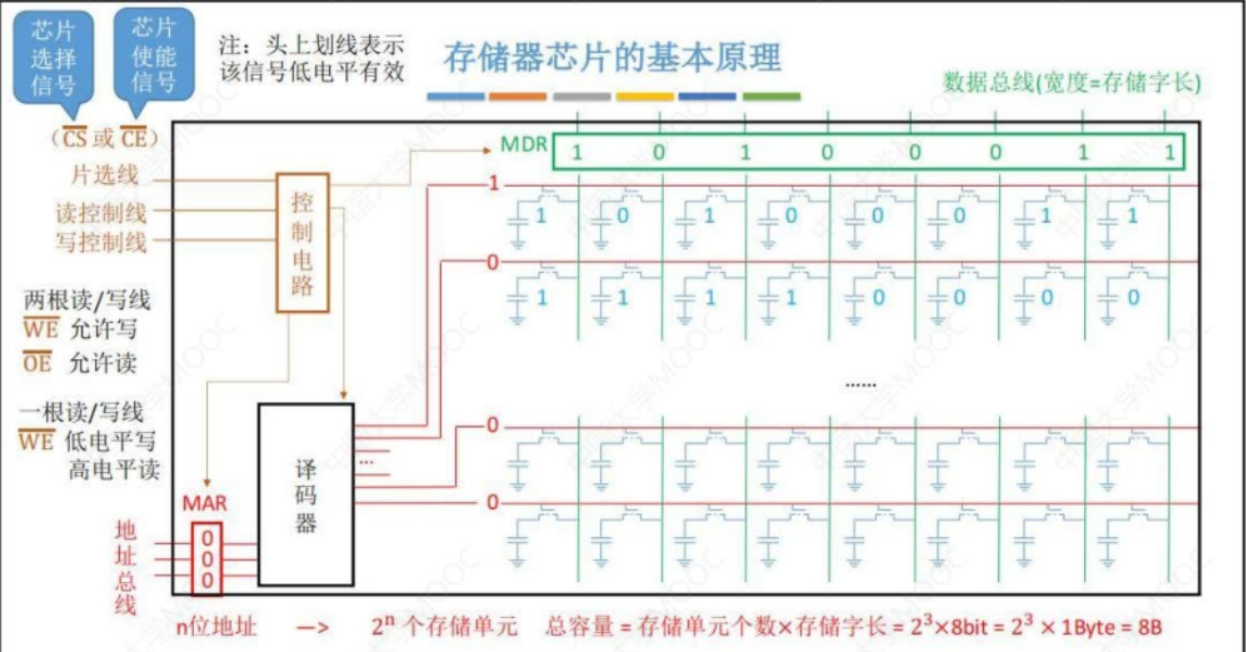

前面讨论了主存的存储元,现在看到存储器芯片的层面。

之前提到主存储体中是一个个存储单元,而每个存储单元又由若干个存储元构成,如上图。

对于控制电路的解释:其中读/写控制线是控制本次操作是读还是写,而片选线是判断是否使用当前芯片,具体可以看主存与cpu连接中字扩展法的片选法。

讨论译码器

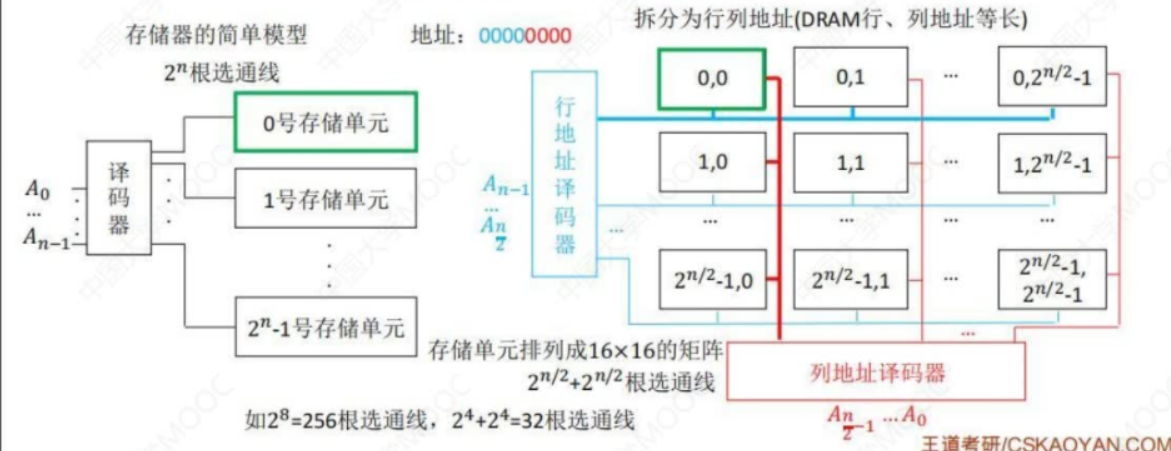

由之前的知识结合上图,可以知道:\(n\)条地址线即MAR为\(n\)位可以推算出有\(2^n\)条选通线,故可以有\(2^n\)个存储单元。而为了减少地址总线的线路数,我们可以采用地址线复用技术,如下图:

将原本线性排列的存储单元改为矩阵式排列即\(2^\frac{n}{2}\cdot2^\frac{n}{2}\)个存储单元,分别使用行地址译码器和列地址译码器寻址。

地址线复用技术:行、列地址分两次送,故地址总线的数目可以减半

这里要说明一下:并不是只有DRAM采用这种矩阵式设计,SRAM也同样是这样,但SRAM不采用地址线复用技术,即它的行、列地址是同时送入的。

总结

对于Cache和主存结构特性的讨论就差不多这样了,而进一步的探讨,例如主存与cpu的连接或者主存优化技术不涉及到硬件电路,这里就不继续说明了。