Verdi

生成FSDB波形

Synopsys+Verdi

两大方法:

1.Verilog系统函数

在testbench中添加:

initial begin `ifdef DUMP_FSDB $fsdbDumpfile("top_tb.fsdb"); //产生fsdb文件 $fsdbDumpvars(0,counter_tb); //第一个参数为0,表示Dump所有层次,非0表示最大层次;第二个参数Dump模块名 `endif end

日志中查找生成记录:/Verdi

2.Ucli/Tcl接口(基于脚本实现) 优点:修改dump参数,不需要重新编译;使用高级语言,支持正则表达式,容易完成复杂处理

编写脚本:

global env fsdbDumpfile "$env(demo_name).fsdb" fsdbDumpvars 0 "tb_top" run

make sim时添加指令:

-ucli -i ../scripts/dump_fsdb_vcs.tcl

便于实现交互式控制:在ucli接口输入命令

更改脚本:

global env fsdbDumpfile "$env(demo_name).fsdb" fsdbDumpvars 0 "tb_top" run 100ns #fsdbDumpoff #run 200ns #fsdbDumpon #run

通过run,fsdbDumpon/off在ucli控制仿真

Cadence+Verdi

Makefile:

run_irun: irun \ -R \ -input ../scripts/dump_fsdb_irun.tcl \ +fsdb+autoflush \ -licqueue \ -l sim.log

dump_fsdb_irun.tcl:

global env call fsdbDumpfile "$env(demo_name).fsdb" call fsdbDumpvars 0 "tb_top" run quit

Questa+Verdi

Makefile:

comp_questa: vlib work vmap work work vlog \ -64 \ -sv \ +acc \ -f ../${demo_name}/tb_top.f \ -l compile.log

run_questa:

vsim \ -64 \ -batch \ -novopt \ -pli ${VERDI_HOME}/share/PLI/MODELSIM/${PLATFORM}/novas_fil.so \ work.tb_top -do ../scripts/dump_fsdb_questa.tcl \ +fsdb+autoflush \ -l sim.log

脚本dump_fsdb_questa.tcl:

global env fsdbDumpfile "$env(demo_name).fsdb" fsdbDumpvars 0 "tb_top" run -all quit -sim

加载和设计波形:

verdi加载设计脚本:

dgb:

verdi \ -sv \ -f ../${demo_name}/tb_top.f \ -top tb_top \ -nologo \

自动加载 -ssf *.fsdb

重复加载设计和波形:

重新加载设计

nTrace-->File->Reload Design

重新加载波形

nWave->File ->Reload

选择信号两种方式

nTace:左键拖选,Ctrl+w

nWave:可使用通配符,可方便选择输入,输出,input,wire,reg信号

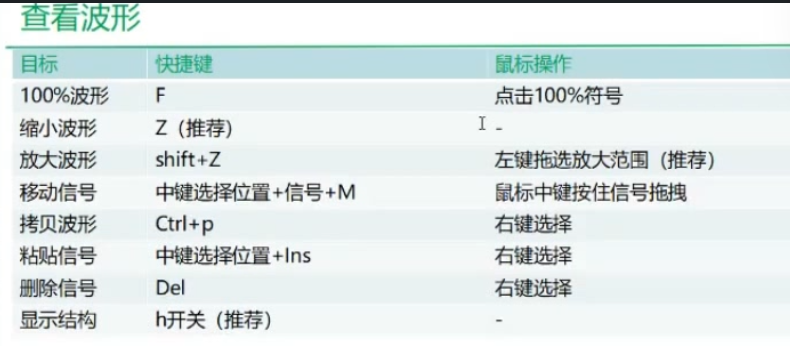

查看波形

追踪设计

通过拓扑结构,Trace/Load快速熟悉设计

快速找到应用示例

nTrace中获取当前时刻信号值