Cache - 直接映射缓存

发布时间 2023-06-09 14:26:07作者: 可达达鸭

1. Cache line

- cache size:cache可以缓存最大数据的大小。

- 将cache均分相等的块,每一块称为cache line,现在的硬件设计中,一般cache line的大小为4-128字节,cache line做的太小会导致tag资源占用过大。

- cache line 是 cache 和主存之间数据传输的最小单位。

- 在cache缺失时,即使CPU只需要从主存中读1个字节的数据出来,但是还是会直接load出8(该值为设定的cache line大小)个字节填充整个cache line。

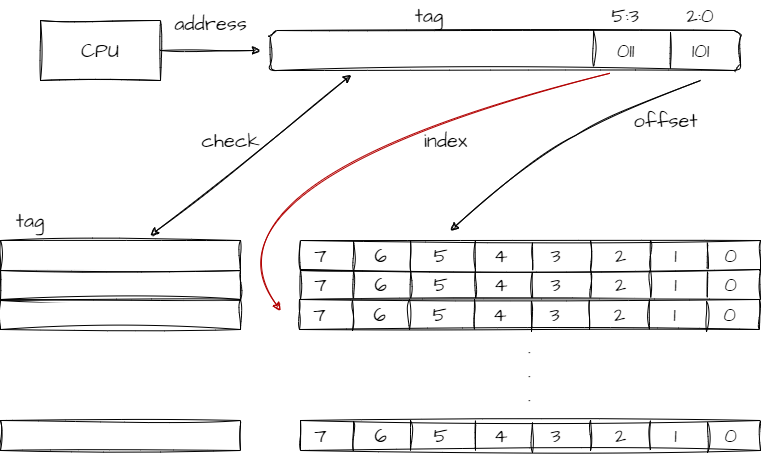

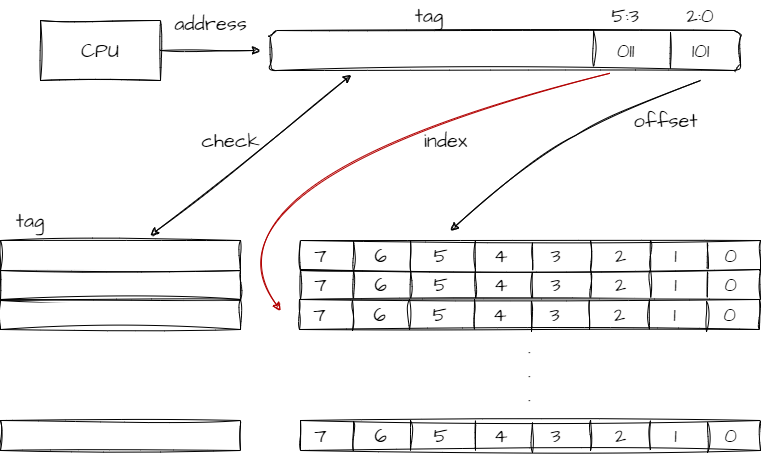

2. Cache控制器怎么确定是否命中

- 首先假设cache 大小为64Bytes,cache line大小为8Bytes。假设CPU想从地址为0x0654地址取一个字节数据。

- 考虑cache line大小为8Bytes,使用地址低3bit来寻址其中的一个字节。(offset[2:0])

- 计算可得有8个cache line,可以使用3bit地址来寻址是哪个cacheline。(index[5:3])

- 对于一个地址,即使确定了[5:3]bit,也不能就确信找到了正确的地址,还有更高位数信息。

- cache将高位信息用tag表示, tag、index、offset可以确定唯一的那个地址。

- 检查是否命中:首先根据index找到cacheline,然后将cache的tag与地址的tag比对,如果相等,说明命中,如果不等,说明缺失。

- tag 前面还加了一位valid bit,首先判断该位,判断缓存中的数据是否有效,若无效不用判断是否命中,直接缺失。

3.直接映射缓存的优缺点

- 优点:硬件设计更简单、成本低。

- 缺点:cache thrashing(cache 颠簸)

- 与上面假设相同,此时cpu想依次访问0x00,0x40,0x80地址的数据,这三个对应的index和offset都是一个,唯一区别是tag值。

- 访问0x00时,cache缺失,cpu从主存中load出8个字节大小的数据填充cache line。

- 访问0x40时,索引到第0行cacheline,但这里存的是0x00对应的数据,仍缺失,再加载0x40地址的数据。

- 依次类推,0x80也要经过刚才两步:缺失+从主存中load。

- 这样cache对性能没什么提升。

- 为了解决这个问题,引入了多路组相连缓存,见这篇博客