- 逻辑综合:代码转变为网表

- FPGA:代码转变为FPGA内部的数字单元

- 在进行综合的时候往往会使用一些脚本工具

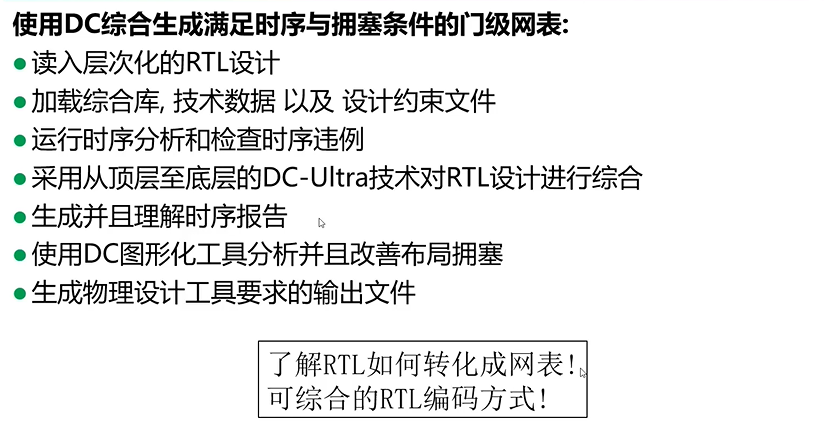

1.目标

- RTL -- 书写完成后,输入到DC,复杂的RTL设计,通常是层次化设计

- 综合库 -- 使用的工艺库,比如台积电5nm工艺,设计约束和技术文件

- 了解命令,掌握分析报告的方法

2.必备知识

- 门级 -- 将RTL转变为门级电路(或门\寄存器\与门\与非门)实现的网表

- idea -- 需求 -- 架构 -- 微架构设计 -- RTL -- Netlist -- 版图 -- Fab -- 芯片 -- 封装测试 -- 集成到PCB上

2.1 综合逻辑

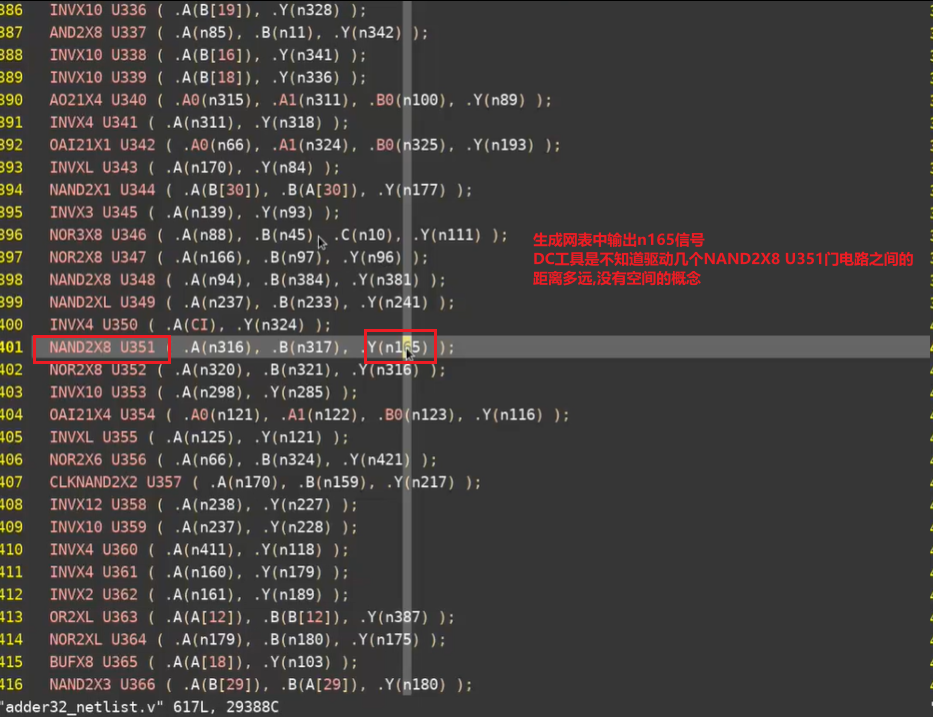

- 第一遍综合的时候,输入的是代码,没有物理信息,综合结果可能不是很理想

- 往往在第一遍综合之后还可能进行第二遍综合

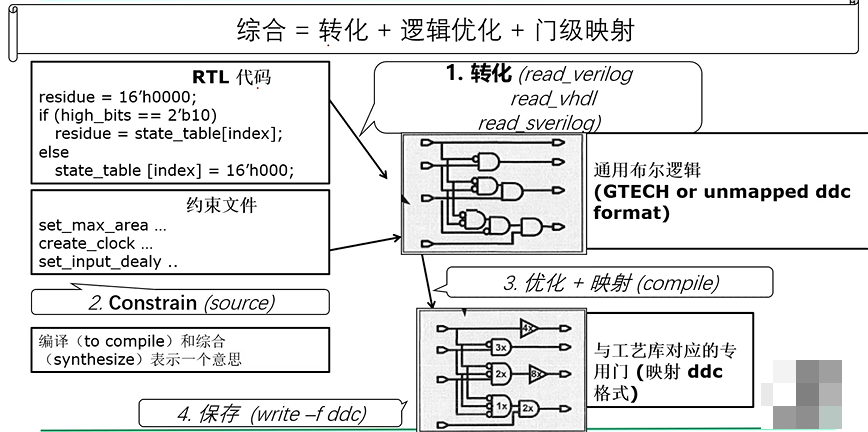

2.2 综合流程

- 转化:先将RTL代码转变为一种GTECH格式的通用网表(和使用的具体工艺库是不对应的)

3.综合示例

3.1 RTL

module (

input wire [31:0] a_in,

input wire [31:0] b_in,

input wire [0:0] c_in,

output wire [31:0] sum_out,

output wire [0:0] c_out

);

assign {c_out,sum_out} = a_in + b_in + c_in;

endmodule

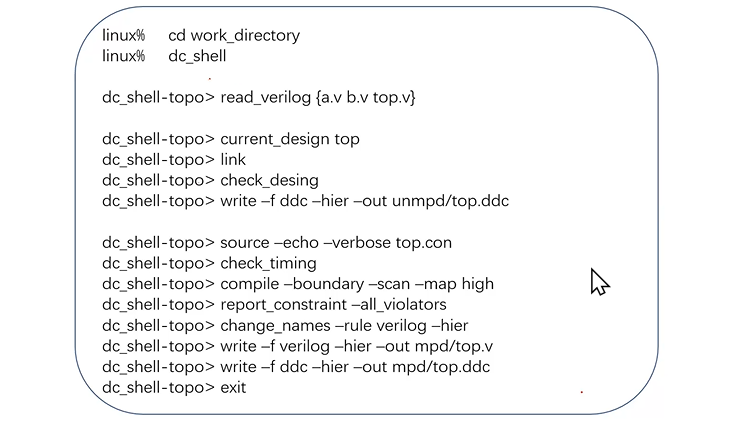

3.2 综合过程

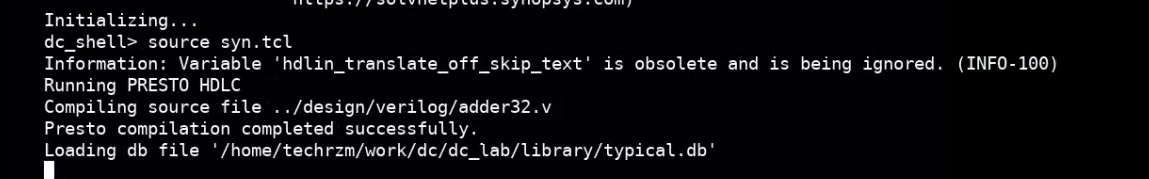

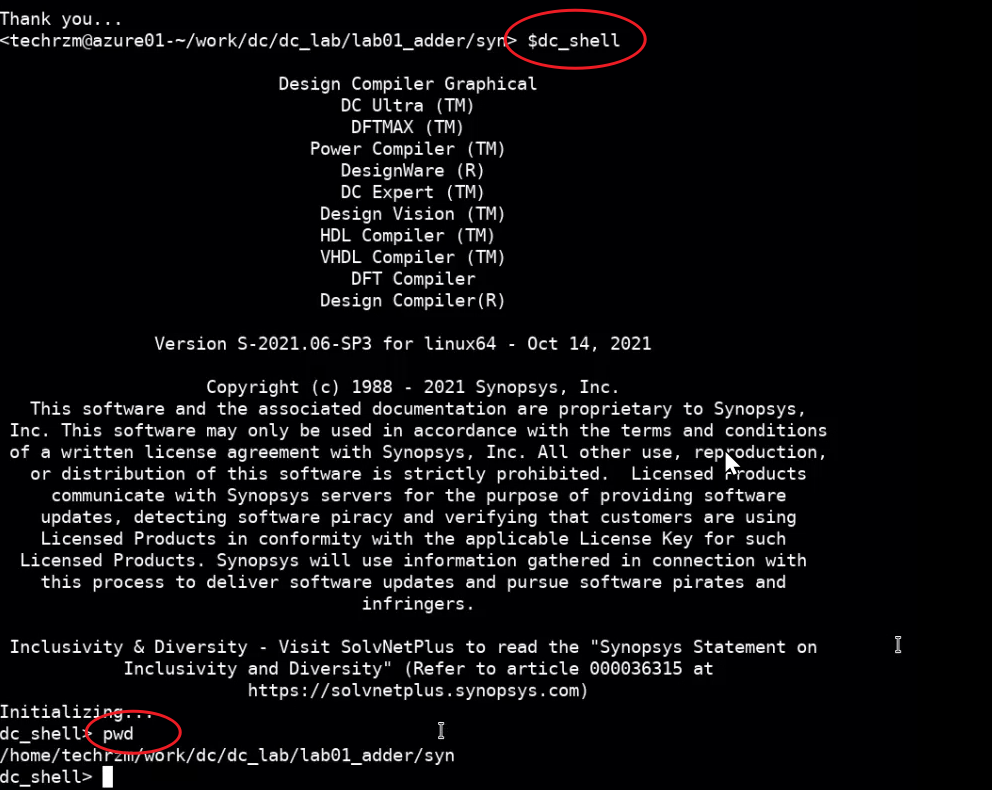

- 在命令行中输入dc_shell

dc_shell

- 一般使用脚本的形式

2.source 综合文件

source syn.tcl

3.产生结果

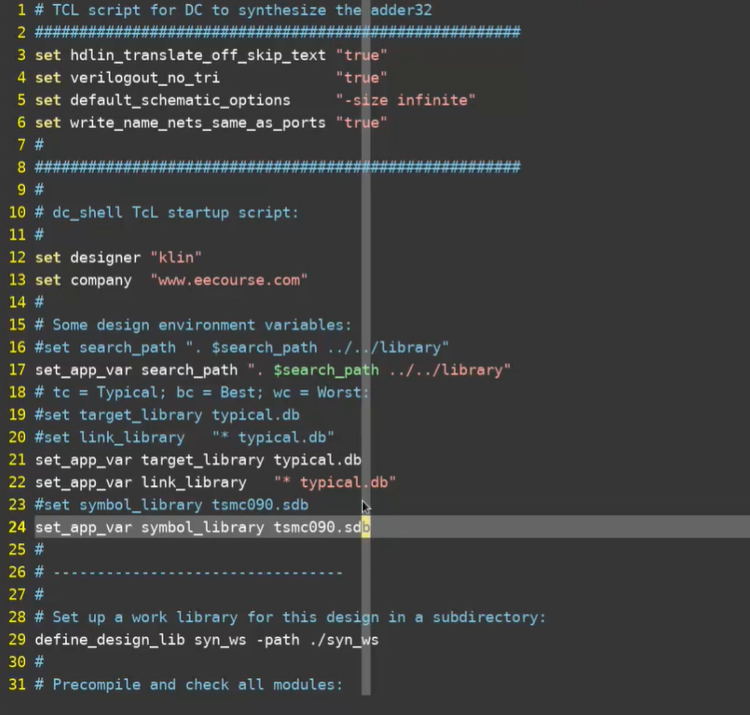

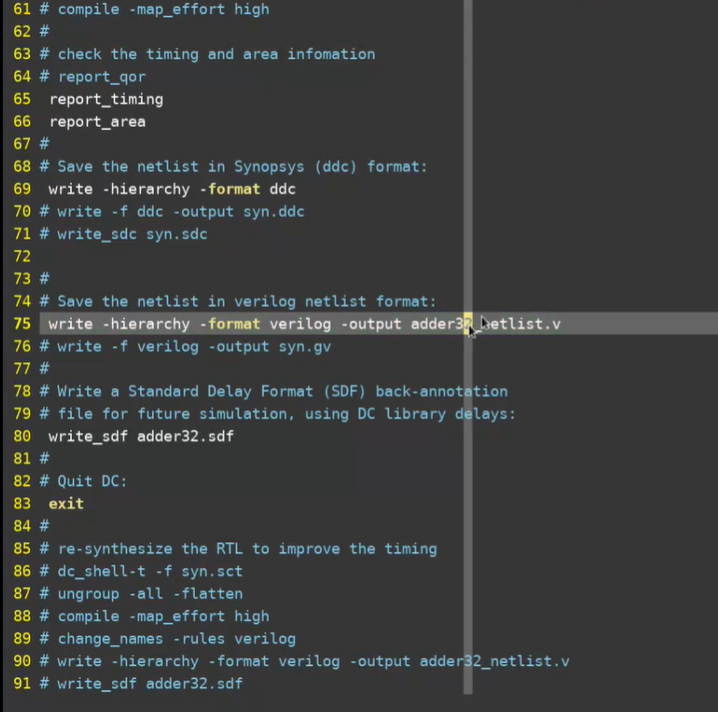

3.3 syn.tcl脚本内容

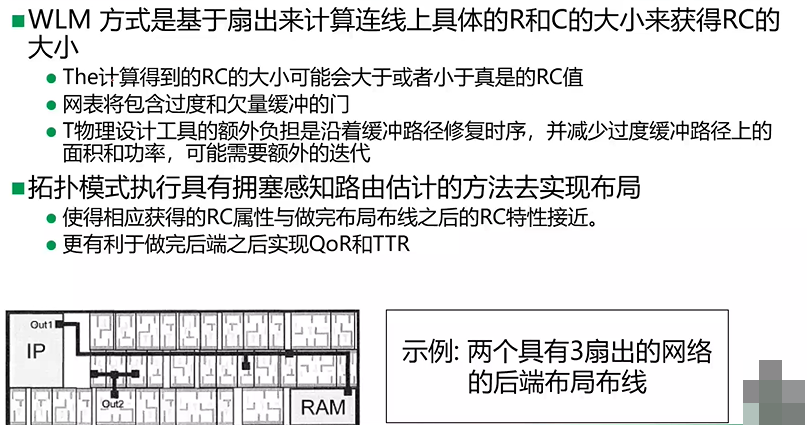

4.两种计算互连产生的RC系数的方式

- WLM根据扇出的数量估算门电路和门电路之间的线路长度,以此来推断RC的大小,是一种概率学上的统计结果

- 优点:方便计算

- 缺点:计算RC > 实际RC,会有一些冗余设计,浪费一些面积;计算RC < 实际RC,网表包含欠量的缓冲门

- 会对RC的结果进行迭代,就是多计算几次

- 寄存器之间的延迟:standcell的延时和一些连线,对于standcell的延时,是准确的,唯一不准确的连线的延时往往是不准的,在综合的时候往往需要迭代

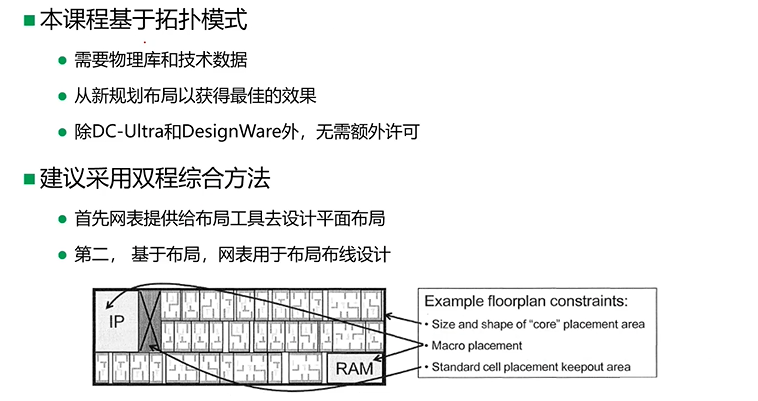

- 采用拓扑的方式计算RC,拓扑模式需要读取RTL之外还需要读入物理信息 ,有物理信息支持之后,计算的RC结果往往是准确的,可以针对性的对一些路径进行优化

- QOR -- quality of result

- TTR -- Time to Result

- 拓扑模式:需要布局布线之后的物理信息

- 在企业中往往使用双程的综合方法,首先使用WLM方式进行一遍逻辑综合,后端使用WLM工具进行一遍布局布线,将布局布线后的物理信息传递给DC,再次进行拓扑模式下的综合

4.1 双程综合方法

- 首次综合,可以添加一些约束

- ICC -- 进行布局布线,产生DEF文件,其中包含了一些物理信息

- 拓扑模式下的综合:DCT,产生一个网表

- ICC -- 再次进行布局布线

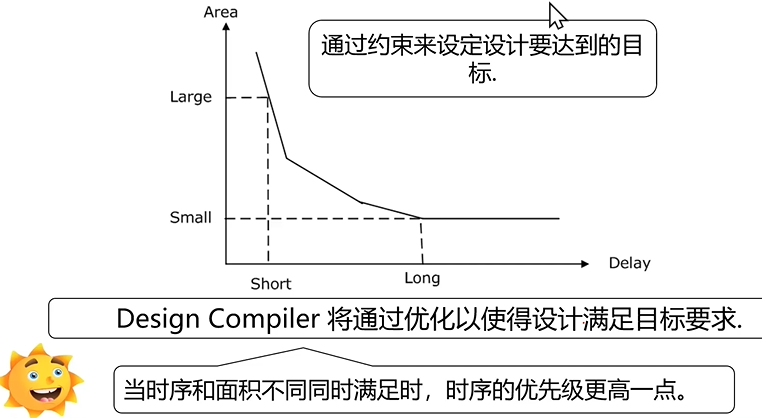

5.约束驱动综合

- 频率约束,面积约束

- DC优先满足时钟频率,在保证时钟的情况下,优化面积

- delay小,performace好,面积大;delay大,performance差,面积小;

- power/performance/area -- 三者是相互约束的

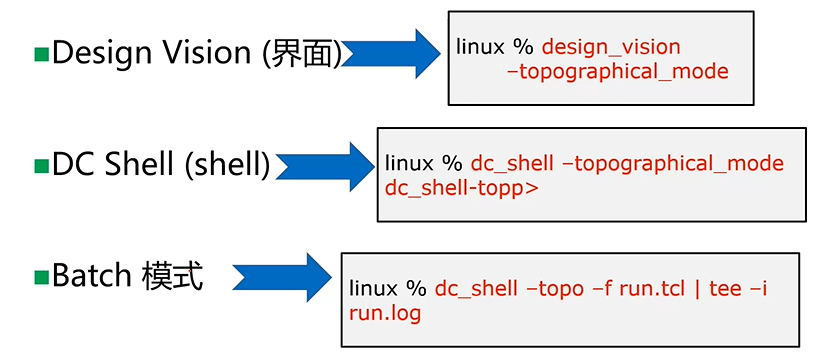

6.综合工具的启动方式

1.在命令行输入design_vision,可以打开图形化界面,查看物理信息的时候使用图形化界面

design_vision

2.dc_shell,使用的是WLM license,交互模式

# 使用WLM模式

dc_shell

# 使用拓扑模式

dc_shell -topo

- 使用bash模式,长用于使用稳定脚本,查看报告,在公司中经常使用bash模式

dc_shell -f syn.tcl | tee -i run.log

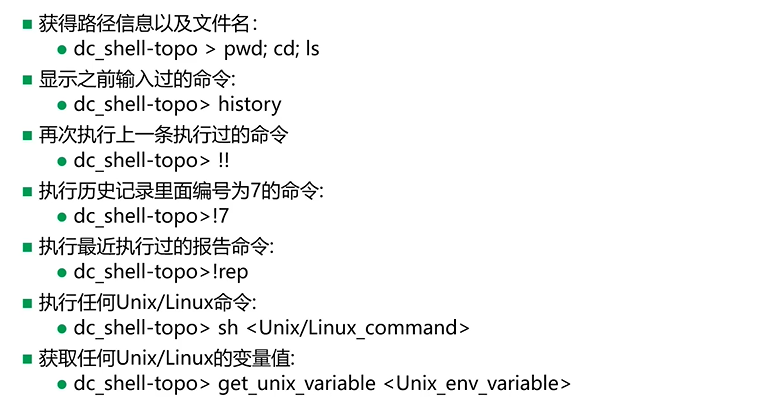

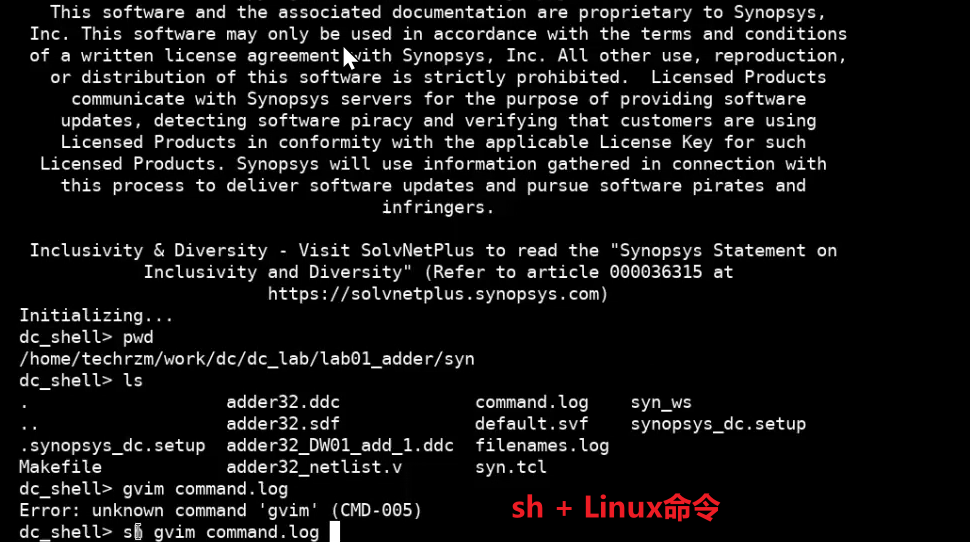

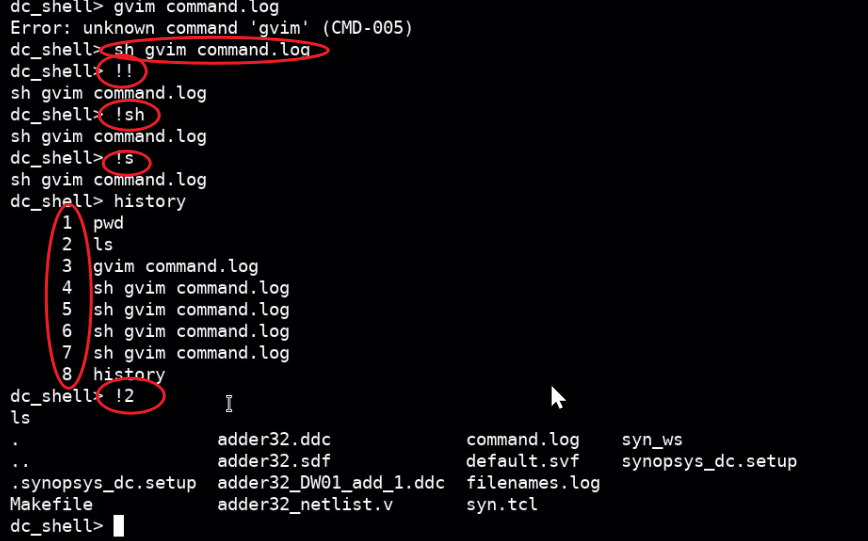

7.Unix\Linux系统DC-Shell命令

dc_shell

- dc_shell 中执行linux命令,前面加sh

- 执行上一步操作

1.上下箭头可以选择命令

2.!!--执行上一步操作

3.!+上一步开头的命令

sh gvim test.v

!sh -- 可以执行上述命令

!s -- 也可以执行上一步命令

4.history -- 查看历史命令,通过!+数字选择执行第几条命令

- .ddc文件包含网表和约束sdc文件,拿到.ddc文件可以认为是进行了综合

8.DC工具掌握

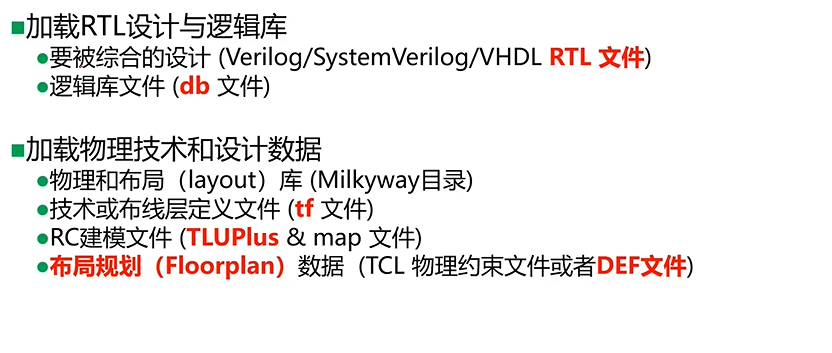

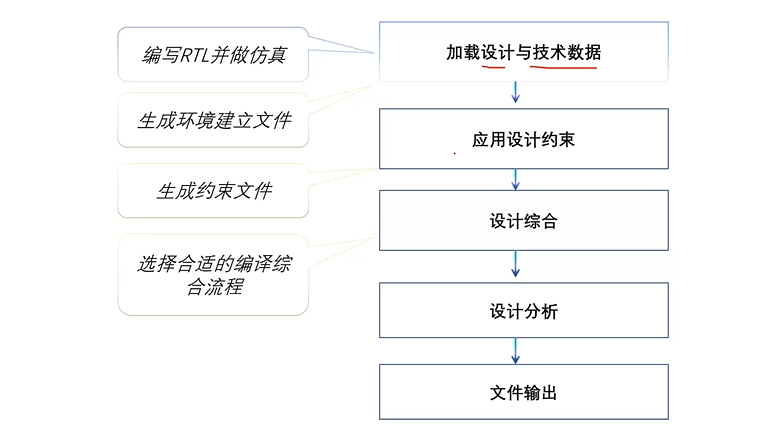

8.1 综合主要步骤

- .db文件 -- 逻辑综合库

8.2 DC主要流程

8.3 DC命令总览

- current_design top 设置顶层为综合对象

- link -- 将RTL层级理顺

- check_design -- 检查RTL代码