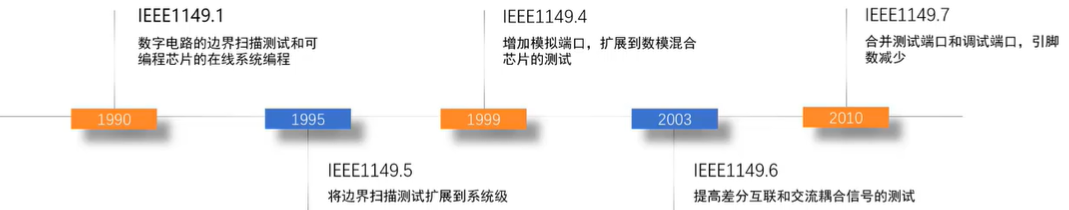

1.JTAG概念

1.1 背景介绍

1.1.1 传统针床测试

- 机台芯片测试 VS PCB板上测试

- 板级芯片间测试

- 传统针床测试

- 芯片管脚日益增多

- 多层印刷电路板

- 新型边界扫描测试

- 传统针床测试

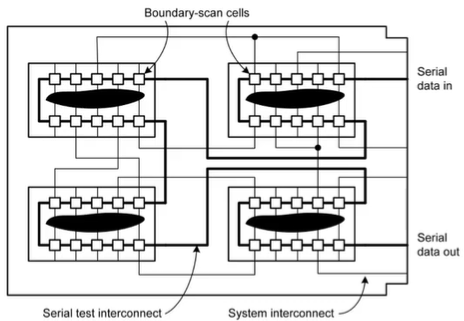

1.1.2 边界扫描测试(Boundary Scan)

- 目的:

- 板级芯片互联线测试

- PCB板级芯片测试:如果针对板级某个芯片进行测试,可以Bypass掉其他芯片,通过边界扫描链将测试数据输入芯片

- 标准:

- JTAG(Joint Test Action Group)

2. JTAG架构

- 指令寄存器:存储控制测试的指令,指导测试时流程。在IJTAG电路生成之前,就应该确定每种指令具体实现的是什么操作;

- 旁路寄存器:旁落哪些模块不进行测试;

- 标识寄存器:识别该JTAG网络出自哪个厂商;

- 其他数据寄存器:存储用于测试不同模块的测试数据;

- 功能管脚:在功能管脚上增加边界扫描寄存器;

- 指令解码寄存器:解析控制指令,确定哪个寄存器工作;

2.1 JTAG架构

- JTAG架构

- JTAG标准端口

- JTAG状态机控制器

- JTAG寄存器

- JTAG指令解码器

- JTAG标准端口

-

- TCK

- TMS:test mode

- TDI

- TDO

- TRST(可选):可用TMS信号代替

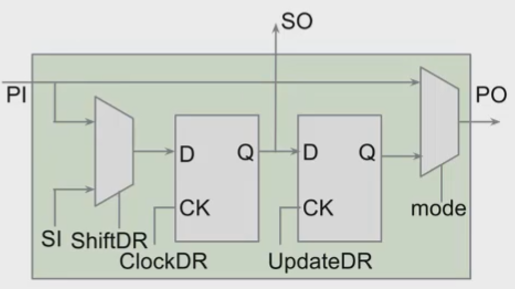

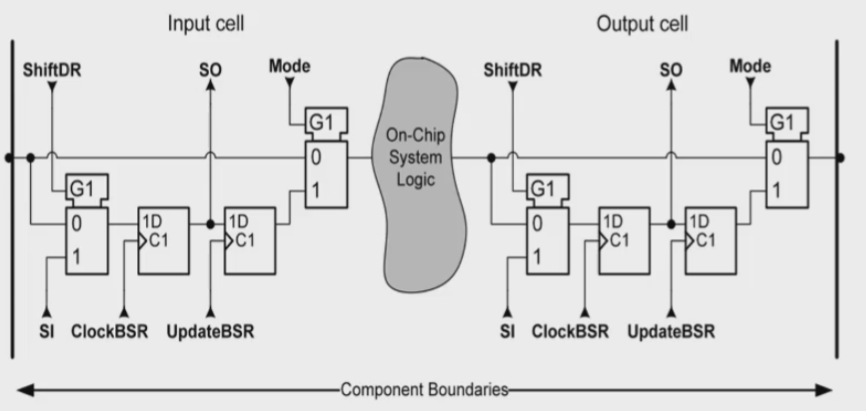

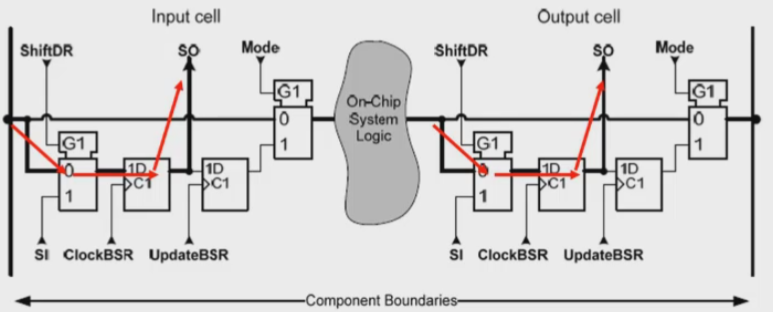

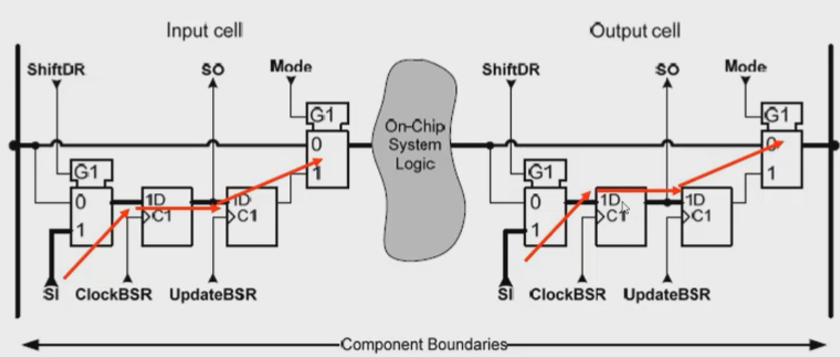

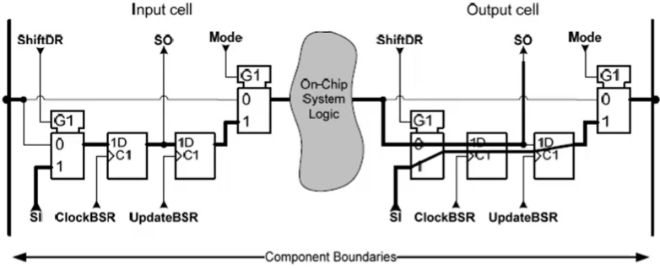

2.2 边界扫描寄存器

对于输入功能管脚,PI就是管脚输入,PO就是功能逻辑的输入,SI就是TDI,SO就是ScanOut;

对于输出功能管脚,PI就是功能逻辑输出,PO是输出功能管脚,SI就是ScanIn,SO就是TDO;

2.2.1移位shift

2.2.2更新update

2.2.3捕获操作capture:捕获电路状态

2.3旁路寄存器

仅需操作1bit

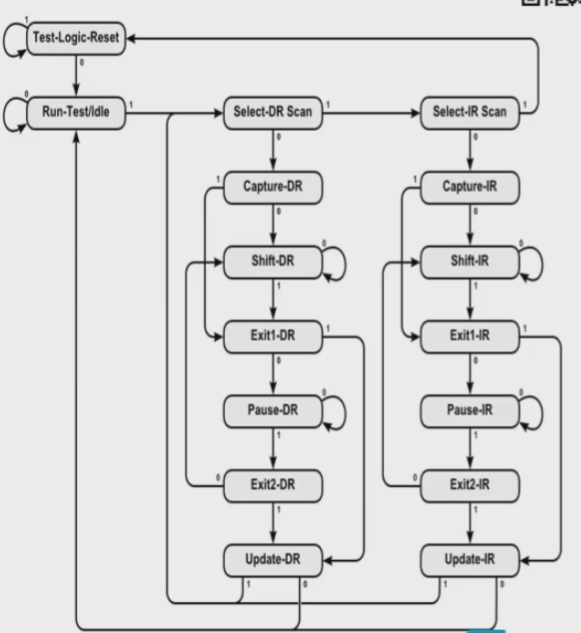

2.4JTAG状态机控制器

16个状态,输入收到TCK、TMS、TRST信号的控制;状态之间的跳转由TMS进行控制。DR线路与IR线路,其中DR线路是数据寄存器相关控制,IR线路是控制指令寄存器相关控制。

- 指令控制:Run-Test/Idle -> 2个pulse的TMS=1 ->进入Select-IR Scan ->TMS=0 -> 进入Capture-IR -> TMS=0 -> Shift-IR,然后重复Capture与Shift操作 -> Exit-IR与Pause-IR为中间态,可跳过 -> Update-IR更新数据 -> TMS=0进入Run-Test/Idel,或者TMS=1直接进入Select-DR Scan状态;

- 数据控制:每次只能操作一种data寄存器,例如数据寄存器或者旁路寄存器;

- JTAG复位操作:5 个TMS = 1进入Test-Logic-Reset状态,或直接使用TRST=0进入Test-Logic-Reset状态;

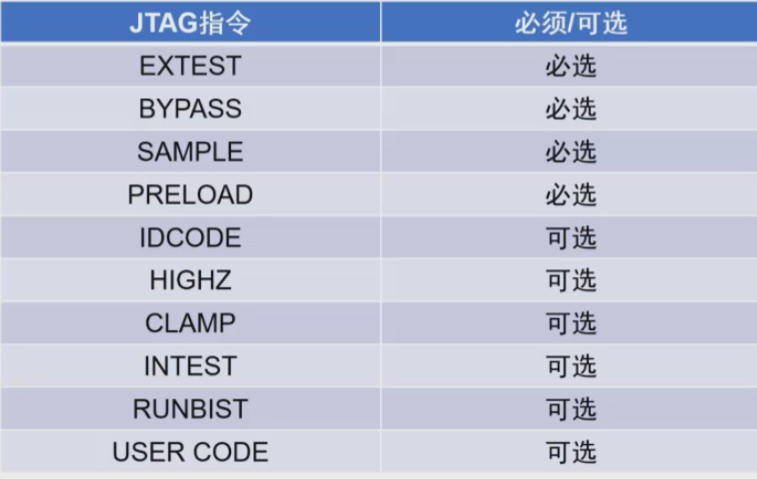

3.JTAG指令集

IEEE1149协议规定的指令如下:

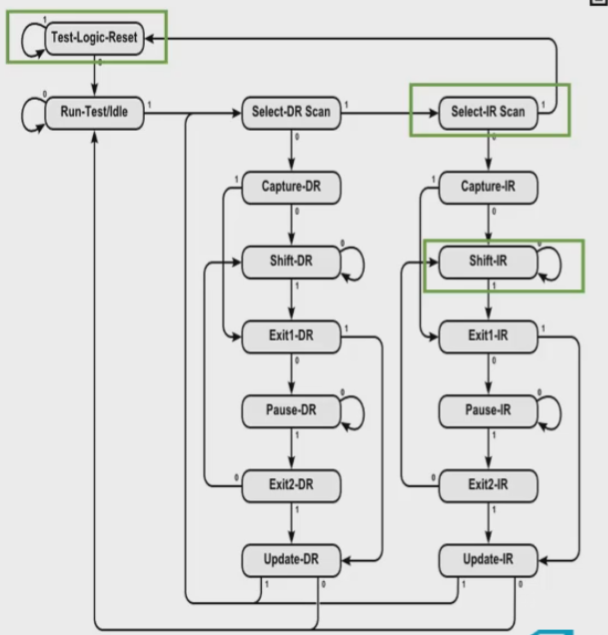

3.1 激活JTAG指令的方法

- JTAG初始化

- 通过TMS运转状态机

- Select-IR

- Shift-IR

- Run-Test/idle

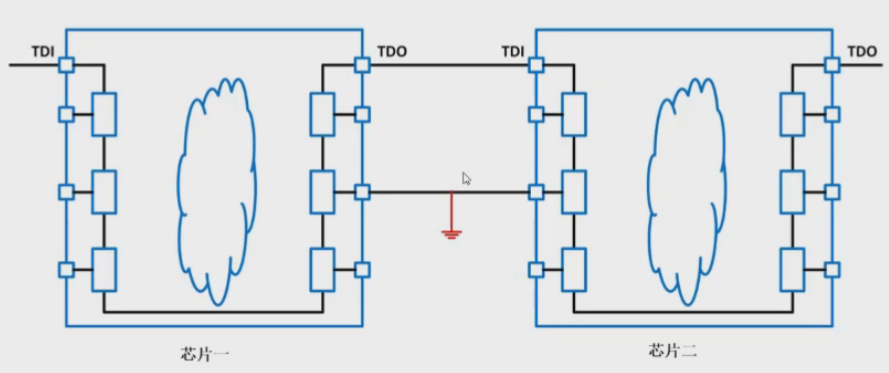

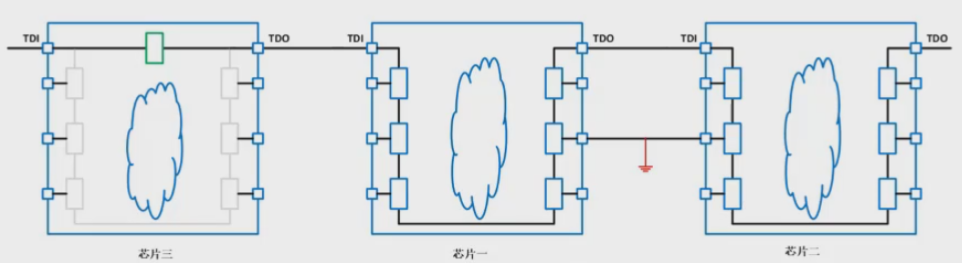

3.2 EXTEST指令

目的:测试板级芯片间互连线

- 输入EXTEST指令

- TDI移入数据到芯片一(shift)

- 更新芯片一的输出管脚(update)

- 芯片二捕获输入管脚数据

- TDO移出数据从芯片二

3.3 BYPASS指令

- 目的:旁路不需要测试的芯片

- 芯片三的TDI和TDO之间只有一个bit的旁路寄存器

- 缩短测试时间

3.4 SAMPLE指令

- 目的:获取新片输入输出管脚的即时数据

- 在输入部分:采样来自外面的输入数据

- 在输出部分:采样来自ChipSystem部分的输出数据

3.5 PRELOAD指令

- 目的:将数据Load进OnChipSystem部分,或者是将数据Load出去

3.6 IDCODE指令

- 目的:把存储芯片ID信息的寄存器接入TDI/TDO链,获取ID信息

- ID信息有32BITS,有JEDEC组织分配给每一个厂家

3.7 INTEST指令

- 目的:芯片内部测试(通过BoundryScan可以控制OnChipSystem的任意IO,控制输入输出进行内部的测试)

3.8 USERCODE

- 目的:芯片内部集成的Ip测试

- 针对不同的Ip,选择不同的指令,同时通过数据寄存器进行输出输入输出的控制

- UESRCODE更像是一个集合,里面包含针对不同Ip的指令,这些指令需要保存到指令寄存器中,同时指令解码器能够解码指令才可作用

4 Tessent边界扫描插入流程

4.1 总流程

- 读入网表

- 配置测试信号

- 配置边界扫描插入

- 插入边界扫描

- 生成综合脚本

4.2 读入网表

- set_context dft -no_rtl

- read_cell_library & read_verilog

- set_current_design

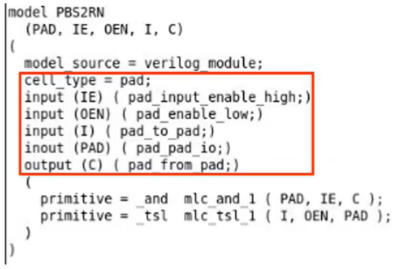

- IO cell library

- IE:控制PAD是否能够输入

- OEN:控制PAD是否能够输出

- I:芯片内部向PAD进行数据输出(在PAD角度看)

- PAD:PAD本身以双向IO存在

- C:PAD将外部数据输出到芯片内部

4.3 配置测试信号

- set_dedign_level chip

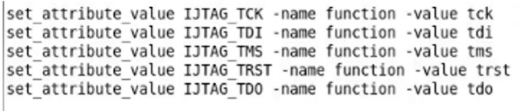

- Define 5 JTAG TAP pins

- check_design_rules(check到AnalysisMode)

其中IJTAG_TCK这些名字是信号的LogicalName,更重要的是需要哪些PhysicalName(tck、tdi...),以及对应关系

4.4 配置边界扫描插入

- set_dft_specification_requirements -boundary_scan on(设置操作模式boundaryScan)

- set spec [create_dft_specification](生成测试命令) set_boundary_scan_port_option xxxx(特殊化定制需求对扫描链)

- Pin order according to physical location.(根据芯片的IO指定PAD的物理顺序)

- Non-bscan IO.(哪些IO不做BoundaryScan)

- report_config_data $spec / write_config_data xxx.tcl -replace(打印链信息至屏幕 / .tcl内)

4.5 插入边界扫描

- process_dft_specification:生成相应的的RTL,并插入现有网表

- extract_icl(boundaryScan的插入会作为IJTAG网络一部分存在,需要检查边界扫描是否合理)

-

- 检查1687相关连接是否正确,生成当前层次的ICL文件

- 生成综合用时序约束文件

4.6 生成综合脚本

- run_synthesis (-generate_scripts_only)

- 在tessent shell内部调用综合工具直接综合,但会占用tessent licence

- 只生成综合脚本,用户在外部调用综合工具,例如DC

- write_design_import_script:将涉及的众多RTL文件统一写在script脚本中