chiplet

定义

- chiplet是芯粒,高集成芯片=独具特定功能的chiplet+先进封装技术。最重要的技术突破在于封装,其次是测试。

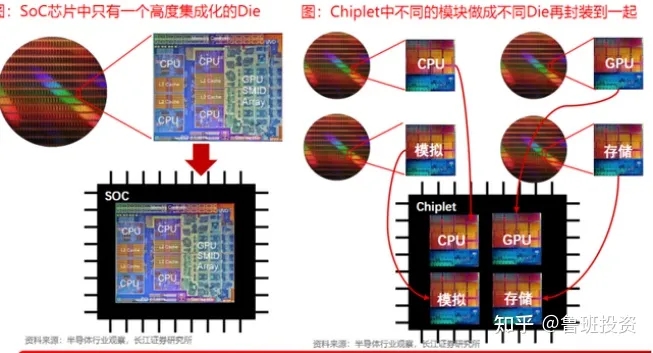

- 区别(Chiplet比SOC多了一组封装的流程):

- soc要求所有模块都是相同制程

- 不同模块对制程要求并不相同,通常模拟芯片的制程只需要到130nm也可以很好的工作。

- chiplet多出来的这一层封装,将不同制程、不同材质、不同工艺封装到一起,这是非常复杂的,需要成立chiplet生态联盟,解决关键传输协议标准、各个功能区域模块的链接方式统一等问题

- 优势:

-

制程成本:

- 28nm芯片:4000万美元

- 7nm芯片:2.17亿美元

- 5nm设计:4.16亿美元

- 3nm设计:高达5.9亿美元

-

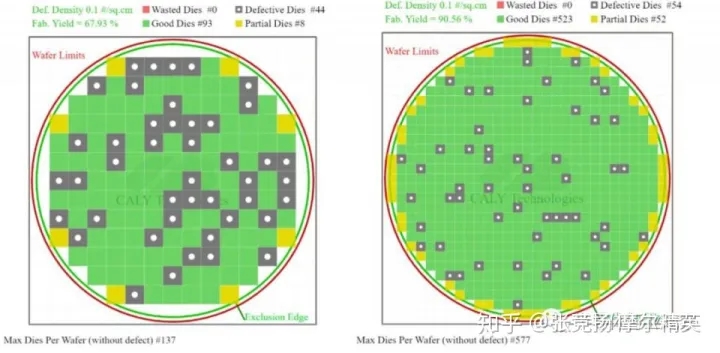

良品率:

- chiplet可以使单个模块的面积显著减小。

- 打破摩尔定律:更高的良率+芯片互联,使得单个芯片的算力终于不再受制程和面积约束

- 芯片面积增大,良品率会下降;良率与晶圆的制造有关,参考下图:

-

IP复用:

- 模块化设计,可以降低总体设计的复杂度

- 有利于产品迭代,加快上市周期

-

fab角度:

- 高良率,即使封装成本上升,也值得

- 不同工艺的die可以混装,有利于新工艺销售

-

- 应用:

- AI, HPC(High Performance Compute)对于chiplet的需求更迫切

- 各家公司都有chiplet产品问世,但大多还停留在自家芯片系列遵循各自的chiplet的互联,还没有形成像USB一样的通用标准

- 22年,UCIe成立:

- 英特尔与AMD、Arm、高通、微软、谷歌、Meta、台积电、日月光、三星等十家行业巨头正式成立UCIe(通用芯粒高速互连)产业联盟,意欲共同打造Chiplet互连标准,携手推动Chiplet接口规范的标准化。

- 国内:

- 芯原股份:此前已经正式宣布加入UCIe产业联盟

- 长电科技:公司已于22年6月加入UCIe产业联盟。

- 华天科技:公司称掌握chiplet相关技术。

- 通富微电:公司已大规模封测Chiplet产品;公司在Chiplet、WLP、SiP、Fanout、2.5D、3D堆叠等方面均有布局和储备。

- 寒武纪:公司思元370是首款采用Chiplet(芯粒)技术的AI芯片。

- 晶方科技:Chiplet技术目前是行业发展的趋势之一,公司在研究该技术路径的走向,并与合作伙伴共同寻找合适的产品应用。

- chiplet为IP公司提供了一种新的产品形式,国内外都仍然是起步阶段

成就

-

AMD公司:

- EPYC (Naples) :AMD 服务器CPU,处理包括4 个Zeppelin die,使用的还是2D 的 MCM (Multi-chip module)封装

- 每个Zeppelin die 都包括单独的memory, IO complex,infinityFabric 的控制与接口

- 每个Zeppelin die 是213mm^2

- 4 个die 就是852mm^2

- 777mm^2 非常接近reticle limit size 了,这是光刻机能够处理的最多的尺寸

- Zeppelin die 包含2 个core complex-CCX。一个Zeppelin die 做桌面产品,2个Zeppelin die 做高端桌面产品, 4 个Zeppelin die 就是服务器产品。

- 一个Zeppelin die 可以覆盖服务器和桌面两个市场,这个收益明显

- 每个Zeppelin die 都包括单独的memory, IO complex,infinityFabric 的控制与接口

- EPYC (Rome):

- Rome 的CCD 的面积是74mm^2,包括了3.9B 的transistors。对比Zepplin 的CCX面积大约是88mm^2,2.8B 的transistors,感觉改进还是巨大的,7nm 的工艺进步也是显著的

- 从一个chiplet 上包含内存控制器,I/O 和Infinity 互联的接口, 转变为有一个中央集中式I/O 和内存控制器die,而且这个集中IOD 仍然有14nm 工艺,CCD 仍然保持8 个核的设计。8 个CCD die, 一个IOD,最高核数为64 个

- Ryzen (Matisse):

- Ryzen 产品线重用了 EYPC Rome 的CCD。只是单独配了一个Client IOD。

- EPYC (Naples) :AMD 服务器CPU,处理包括4 个Zeppelin die,使用的还是2D 的 MCM (Multi-chip module)封装

-

intel公司:

- 它有自己的fab,而chiplet是fab最积极主导的事:Intel 在fab 技术和制定业界标准上都强:

- EMIB:Stratix 10中心是FPGA die,周围是6 个chiplet:

- 4 个高速transceiver chiplet 和2 个高带宽memory chiplet

- 且这6 个chiplet,是来自三个不同fab 的6 个不同工艺chiplet,证明了不同fab 之间的强大互操作性

- HBM 的3D 封装:HBM需要较高的工艺而大幅度提升了成本,主要是

- AIB 的总线,

- 3D Foveros:Lakefield SoC

- CXL

- EMIB:Stratix 10中心是FPGA die,周围是6 个chiplet:

- 它有自己的fab,而chiplet是fab最积极主导的事:Intel 在fab 技术和制定业界标准上都强:

-

Xlinix公司:

- FPGA 公司因其属性和高利润性,一直是各种先进工艺的率先使用者

- 2011 Virtex-7 2000T 就是4 个die 的chiplet 设计

-

Marvell公司:

- Mochi 概念,多半不会继续走下去了

-

Hisilicon公司:

- 晟腾910 的8 个chiplet 设计,融合了HBM die,逻辑部分与I/O 部分分离,两个dummydie,超大总die size 等特点