前言:为什么要降低芯片功耗

芯片封装都较小,如果功耗过大,则能量密度太大

功耗影响到芯片内部甚至外部的电源网络架构设计

高功率带来温度提升,会使性能受影响,时序跑不高

面向数字IC前端设计的学习可以基于DC中的power compiler工具进行功耗分析;更精确的功耗分析可以采用PT。

1.功耗的构成—按类型分

功耗按照类型对功耗分类包括:动态功耗、静态功耗、浪涌功耗这三种。

动态功耗包括开关功耗或者称为翻转功耗、短路功耗或者称为内部功耗。

开关功耗和短路功耗,或者叫做翻转功耗和内部功耗(内部功耗是工艺库的叫法)

漏电功耗(静态功耗):非理想漏电流产生的功耗(例如MOS管关断时,仍然有微小电流存在)

内部功耗(短路功耗):寄生参数充放电产生的功耗

翻转功耗(开关功耗):晶体管负载充放电带来的功耗

1.1 开关功耗

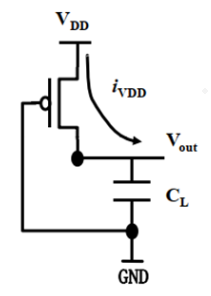

开关功耗:在数字CMOS电路中,对负载电容进行充放电时消耗的功耗,以图1的CMOS非门举例:

当Vin = 0时,上面的PMOS导通,下面的NMOS截止;VDD对负载电容Cload进行充电,充电完成后,Vout的电平为高电平。

当Vin = 1时,上面的PMOS截止,下面的NMOS导通,负载电容通过NMOS进行放电,放电完成后,Vout的电平为低电平。

这样一开一闭的变化,电源的充放电,就形成了开关功耗,对于图1中的电容Cload,当它的电压从0升到VDD时,它储存的电荷为Cload*VDD; 当它的电压从VDD变到0时,它储存的电荷被释放。

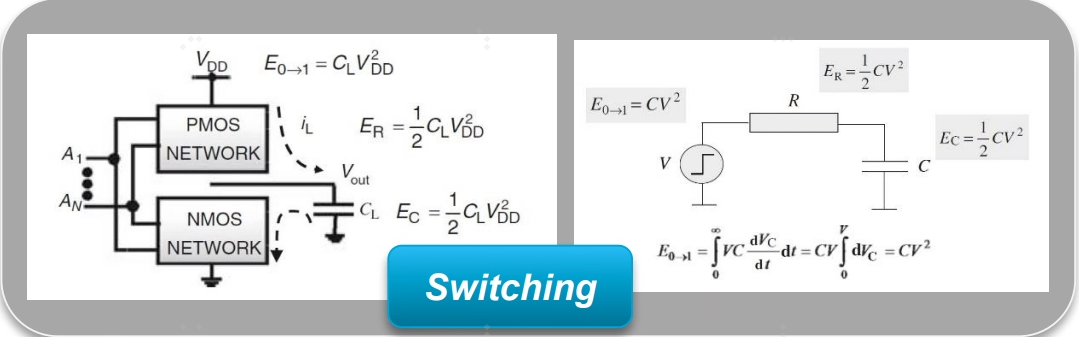

从电源中取得的能量:

电容中存储的能量:

由此看出,一次充电,能量消耗多少和电阻的大小无关。

所以每发生一次转换期间,电源电压输出的能量(能耗)为(全摆幅电路):

计算电容存储的能量:

其中CL是负载电容, VDD是电源电压。

所以在一次充放电过程中,电源电压输出的总的能量有一半存储在电容中CLVDD2/2,另一半被电阻消耗,转化为热能。

输出电容充电(由0-1跳变时)时从电源汲取电流(产生电源能量消耗)。产生的总能耗等于CLVDD2 ,其中一半消耗在充电电阻上,一半储存在电容中(在由1到0的放电过程中被耗散掉). 每次0到1的翻转,从电源取得能量:CLVDD2

EN:N个时钟周期的翻转能量,n(N):N个时钟周期中0到1的翻转次数

动态功耗:

P0→1:输入变化导致输出发生0到1变化的概率,又称为翻转活动因子。设等效电容:

动态功耗计算:

动态功耗与晶体管尺寸无关(负载电容确定的情况下)

功率消耗(功耗):电路的功率的消耗:功率消耗(功耗):平均功耗:单位时间内的能耗P=E/(ΔT).

逻辑门的平均功耗:发生0-1翻转才会有能量消耗,所以平均动态功耗Pav=E/∆T

其中,其中,Pav=E/∆T=E0→1∗f0→1=CLVDD2∗f0→1其中,f0→1是单位时间内发生0-1翻转次数;如果我们定义开关活动性(翻转概率):时钟变化事件在该门输出端引起0-1翻转的概率为P0→1。

则平均动态功耗可以表示为:Pav=CLVDD2∗P0−1∗fclock ,开关功耗不是晶体管尺寸的函数,而是开关活动和负载电容的函数。So,它是data dependent的。

P0−1发生的概率为:前一个时刻为低电平发生的概率乘以当前时刻为高电平的概率.

功耗与器件尺寸(它影响实际电容)、输入和输出上升下降时间(它们决定了短路功率)、器件阈值和温度(它们影响漏电功率)以及开关活动性密切相关。

动态功耗可表示为CLVDD2∗P0−1∗fclock 。当一个门比较复杂时,受影响最大的是开关活动性。这个影响包括两部分,即只与逻辑电路拓扑结构有关的静态部分和由于电路时序特性引起的动态部分。后一个因素也称为虚假尖峰信号或毛刺( glitch)。

在上式中,VDD 为供电电压, Cload 为后级电路等效的电容负载大小, Tr 为输入信号的翻转率。 一般情况下,信号在一个周期内平均翻转两次,即上升沿一次、下降沿一次,也就是说,Tr = 2f。

因此,平均功耗就是: Pdynamic=???2?????∗2?,它与电路的工作频率成正比,与负载电容成正比,与电压的平方成正比。

?????的计算:在 RTL 映射为网表之后,门级电路结构已经确定,因此相对应的负载大小也已确定。负载的大小可以通过设置 max_capacitance 来进行约束。

要降低翻转功耗,可通过降低供电电 压、 减低负载电容、减小翻转概率、降低时钟频率来实现。

降低负载电容:(1)器件栅电容和节点电容,它们和器件工艺有关;(2)连线电容,随着工艺发展,连线电容已经超过器件电容。(3)为了减小电容,改进电路结构,减少所需MOS 管数目是减小负载电容、降低功耗 的重要 途径。(4)SOI CMOS由于有隐埋 SiO2 隔离,寄生电容极小,使 SOI CMOS 电路比体硅 CMOS 电路 有更快的速度和更低的功耗

逻辑功能:翻转活动性与所实现的逻辑功能密切相关。对于输入在统计学上相互独立的静态CMOS门,静态翻转概率是输出在一个周期中为 0 状态的概率 P0乘以它在 下一个周期中为 1 状态的概率P1为: Pt=?0→1=P0·P1=P0·(1−P0)

假设输入是独立的并均匀分布,则任何 N 个输入的静态门的翻转概率为:

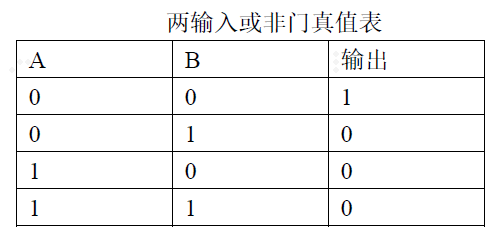

这里?0是布尔函数真值表输出列中 “ 项的数目 而 ?1是 “ 项的数目。为了便于说明 考虑 一 个静态两输 入 NOR 门 假设在一个时钟周期内只可能有一个输入翻转 并且该 NOR 门的输入具有均匀的输入分布 即输入 A 和 B 的四种可能状态 (00,01,10,11)发生的机会均等。

两输入或非门真值表

所以可以推出两输入静态CMOS NOR 逻辑门 的输出翻转概率:

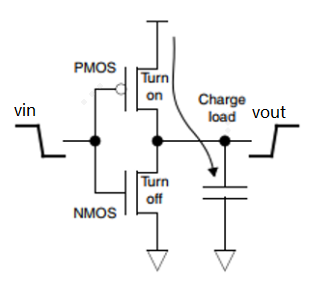

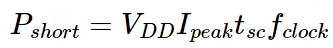

1.2 短路功耗

短路功耗也称为内部功耗,短路功耗是因为在输入信号进行翻转时,信号的翻转不可能瞬时完成, 由于输入电压波形并不是理想的阶跃输入信号,有一定的上升时间和下降时间, 因此 在输入波形上升下降的过程中, PMOS 和 NMOS 不可能总是一个截止另外一个导通,总有那么一段时间是使PMOS 和 NMOS 同时导通,那么从电源 VDD 到地 VSS 之间就有了通路, 一个相对较大的电流,称为撬棒电流,在短时间内流过晶体管 就形成了短路电流, 这就是开关过程中的短路功耗。 如图2反相器电路图 短路功耗 Pshort 的计算公式如下所示:

短路功耗除与供电电压、 翻转概率、时钟频率有 关, 还跟门的输入转换时间和输出转换时间有关。其中tsc 是短路电流的持续时间, Ipeak 是总内部 开关电流(短路电流加上内部 电容 充电所需的电流)。只要输入信号的斜坡时间保持短,短路电流在每个转换期间只发生很短的时间。 较低的阈值电压和较慢的跃迁导致更多的内部功耗。

由此我们可以找到,动态功耗主要有开关功耗和短路功耗;其中开关功耗在动态功耗中占大部分比例;从上面的两个式子中我们可以看到,动态功耗主要跟 电源的供电电压、翻转率、负载电容有关。

1.3 静态功耗

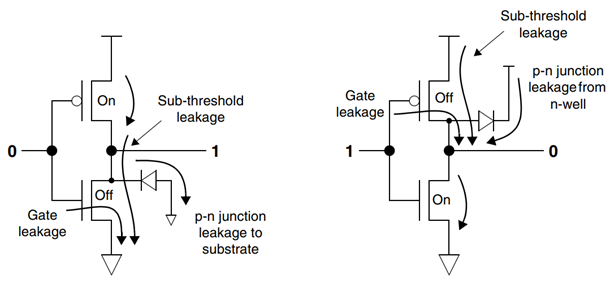

在CMOS 电路中,静态功耗主要是漏电流引起的功耗,如下图所示的CMOS电路,以及详细的漏电流属性。

漏电流有下面几个部分组成:

·PN结反向电流 I1 (PN junction Reverse Current): NMOS 源端和衬底的反偏PN结,以及漏端和衬底的反偏PN结电流,方向由有源区流向衬底反偏漏电流:

A:结面积,与漏区的面积周长有关;

?s=0.1~0.01 ?/ ??2

k 为玻尔兹曼常数,电流的大小与结的掺杂浓度和反偏电压成指数关系。

亚阈值电流I2(Sub threshold Current):栅极电压低于导通阈值,仍会产生从漏极到源极的泄漏电流。此电流称为亚阈值泄漏电流。

在较狭窄的晶体管中,漏极和源极距离较近的情况下会产生亚阈值泄漏电流。晶体管越窄,泄漏电流越大。

亚阈值电流随过驱动电压升高 指数增加。亚阈值电流随Vs 增大而增加 LVT的漏电流功耗较大,HVT 的漏电流功耗较小。

亚阈值电流公式为:

其中W和L是晶体管的尺寸, Vth是热电压 kT/q (室温下为 25.9mV )。参数n是器件制造过程的函数,范围为 1.0 到 2.5.

亚阈值泄漏依赖于VGS和VT之间的指数差。因此,当我们缩小 VDD 和VT(限制动态功率)时我们使泄漏功耗指数变差。

漏感应势垒下降(DIBL)漏电流 I3:短沟器件的源漏距离已能与耗尽区宽度相比拟时, 漏端电压将对阈值电压产生调制作用。

1. VDS 增加会使源端势垒下降 2. 沟道长度缩短会使源端势垒下降

栅极感应漏端漏电(GIDL)I4: Gate-Induced Drain Leakage GIDL 发生在当 栅/漏 覆盖区域下的高场强引起深耗尽,使 漏至阱 PN 结的耗尽区宽度减薄时。 GIDL 局限在沿栅和漏之间的沟道宽度上。

在栅和漏 之间(负的 VG 与很高的正的 VD ) 的高场强作用下,由于:(1)Direct band to band 隧穿 (2)Trap-assisted 隧穿 (3)Thermal emission 与 隧穿的共同作用 而产生了载流子进入到衬底和漏极。

源漏穿通(Punch-through)电流 I5 :当漏端和源端耗尽区互相接触时,在沟道深处发射流加大并以 扩散形式到达漏端。 源漏穿通电流与漏极电压Vds 呈平方关系,但不受栅压控制。 源漏穿通可以看成是在沟道表面以下发生的 DIBL 。

反窄沟效应漏电流 I6 :Weff 沟槽隔离的场氧被埋入衬底,因此有较平坦的 氧化层表面,无鸟嘴效应,提高了集成度。

沟槽隔离的 MOS 结构中,沟道两侧的栅电极覆盖了部分氧化层, 栅边缘电场终止于沟道侧边,使沟道边缘电容增加并在总电容中所 占比例明显增大,引起净栅控电荷减少。

因此,随沟道宽度减小,非沟槽隔离器件的 阈值电压(VT )增加。但是 随沟道宽度减小(W < 0.5μm),沟槽隔离器件的阈值电压(VT )减小 , 使漏电流增加。

·栅极和衬底之间的隧道漏电流 I7 :Gate Tunneling 栅极泄漏是通过栅氧化层的隧穿电流造成的。隧穿效应引起沟道中的载流子通过 SIO2 绝缘层形成栅和沟道间电流, 导通状态时整个沟道面积都存在泄漏电流。

注:无沟道的区域不存在隧穿电流 。特征尺寸缩小 SIO2 绝缘层厚度减小,氧化层越薄, 带来的栅氧漏电流增加 。 PMOS 栅氧漏电流比 NMOS 小一个数量级。

栅氧化层厚度(TOX )在 90nm 的栅中只有几个原子厚,如此之薄以至于隧穿电流会变得很大。

少数热载流子获得足够高的能量可以克服Si-SiO2 界面势垒注入栅氧层中。

氧化层非常薄、电场很高时,热载流子可 通过 直接隧穿效应进入栅氧层。

即使对于较厚的氧化层,当载流子的能量接近但 低于Si-SiO2 势垒高度时,热载流子仍能通过隧穿 越过势垒进入氧化层中(即 FN 隧穿效应)

热载流子效应引起的漏电流 I8 :1.漏端强电场(横向电场)引起高能热电子与晶格碰撞 产生电子/空穴对,引起衬底电流。 2.电子在强纵向电场作用下穿过栅氧,引起栅电流。

影响: 1. 使器件参数变差,特性不稳,电路失效。 2. 衬底电流引起噪声,Latch-up, 以及动态节点漏电。

LDD (lightly doped drain) : 在源漏区与沟道间加一段电阻率较高的轻掺杂 区n‾. 优点:可减小热电子效应,提高源漏电压。 2. 缺点: n‾区使器件跨导和IDS减小

在以往的技术节点中,泄漏电流一直以亚阈值泄漏为主。纳米尺度下,MOS管静态漏电成为影响功耗的严重问题。从 90nm 开始,栅漏电流可以接近亚阈值漏电流的 1/3 。在 65nm 范围内,它在某些情况下可以等于阈值泄漏电流。

在栅极上加信号后(即栅压),从栅到衬底之间存在电容,因此在栅衬之间就会存在有电流,由此就会存在功耗。

在未来的节点上,需要高k介电材料来控制栅极泄漏。要降低亚阈值电流,可以使用高阈值的器件,还可以通过衬底偏置增加阈值电压,为了减少栅极泄露,还需要研究高介电常数的新材料,或者降低工作电源电压,这些属于低功耗设计。

然而,随着器件几何尺寸的缩小(栅氧厚度减小)和阈值电压的降低,漏功耗变得越来越重要,有时甚至接近动态功耗的水平。产生漏功耗的主要原因是反向偏置p-n结二极管漏电流、亚阈值漏电流和栅极漏电流。CMOS反相器中的这些泄漏路径如下图所示。

无论时钟速度或开关活动如何,只要晶体管通电,就会产生漏电流。不能通过减慢或停止时钟来减少泄漏。但是,可以通过降低电源电压或完全关闭晶体管的电源来减少或消除。

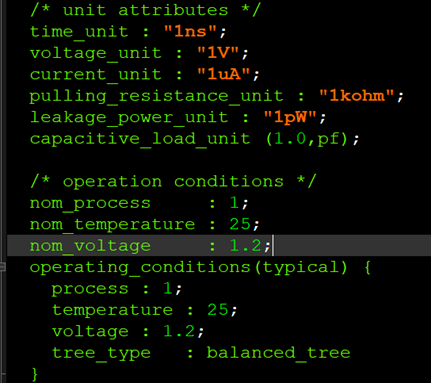

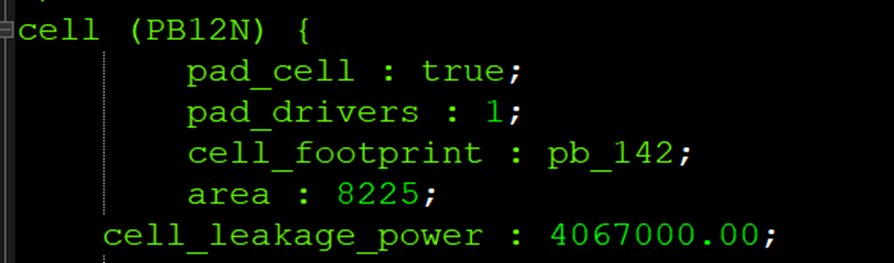

在90nm之前,leakage power在library里确实是被描述成一个常值的。但从90nm开始,为了更加精确,library里的leakage power不再是个常值了,而是被模拟成一个输入状态的函数。所以基础还是library,在一个library里跟leakage相关的变量大致有:

library(my_lib) { leakage_power_unit :"1nW"; default_leakage_power_density :0.0; default_cell_leakage_power :0.0; cell_leakage_power :53057.365200; leakage_power(){ when :"!A & !B & !CI"; value: ...; power_level:"VDD";} }

Leakage_power_unit:标示leakage power的单位,如果所有库里都没有该变量的定义,每个工具都会有自己默认的单位,如Genus默认用nW。

cell_leakage_power:标示固定的leakage power值,如果library里没有该变量的定义,或者该变量是个负值,工具会用default_cell_leakage_power的值,如果default_cell_leakage_power也没有指定,则用default_leakage_power_density的值乘以该cell的面积来计算得出一个leakage值,如果这三个变量都没有定义,则leakage的值为0。

leakage_power(){}:这一部分就是用来定义跟输入状态相关的leakage power,其中"when"用于定义输入的状态,如果某种状态没有定义,则用cell_leakage_power定义的值来计算leakage;power_level用于多电压cell中指定是跟哪个电压相关的leakage power。

搞清library中相关变量的定义后,剩下就是如何计算的问题了,其他情况好理解,分别看一下如何用default_leakage_power_density计算leakage power,及如何计算跟输入状态相关的leakage power。

如果library里既没有定义cell_leakage_power也没有定义default_cell_leakage_power而只定义了default_leakage_power_density,则:

cell_leakage_power= area *default_leakage_power_density

library(my_lib) { time_unit :"1ns"; voltage_unit :"1ns"; capacitive_load_unit(1,pf); ... leakage_power_unit :"1nW"; default_leakage_power_density:0.5; cell(AND2X2){ area :4; ... } }

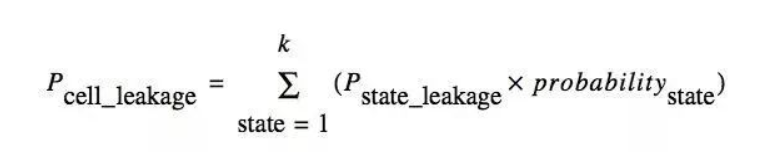

跟输入状态相关的leakge_power计算,计算公式为

k:cell的state数

Pstate_leakage:该状态下的leakage,

probability_state:该cell处于该状态的概率

拿AND2X2这个cell为例,它的输入总共有四种组合状态,在lib中只定义了三种状态,同时还定义了cell_leakage_power,所以对于没定义的状态,在计算时用cell_leakage_power指定的值。假设,A处在状态"1"的概率是0.6,B处在状态"1"的概率是0.3,则该cell的leakge power为:

在实际项目中,如果没有读入activity的文件,不同的工具都会有根据默认或指定的probability来计算每个cell输入pin的probability,不同工具也会有相应的命令来report出当前的probability是多少,如Genus可以用命令:report instance –power,也可以通过以下attribute得到相关信息:

lp_probability_type

lp_default_probability

lp_computed_probability

1.4 浪涌功耗

浪涌功耗是浪涌电流引起的功耗。浪涌电流是指开机或者唤醒的时候,器件流过的最大电流,因此浪涌电流也称为启动电流。一般情况下,浪涌功耗不是我们关注的地方。

1.5 影响功耗主要因素

电压:直接影响3种功耗,特别对翻转功耗影响很大

温度:主要影响泄露功耗,温度与泄露功耗呈指数关系

工艺:直接影响3种功耗

信号翻转率:主要影响电路翻转功耗和内部功耗

信号负载:主要影响翻转功耗和内部功耗

信号翻转时间:主要影响门电路短路电流,从而影响内部功耗。

2. 功耗的构成—按结构分

前面按照类型进行功耗分类,这里使用结构进行分类,也就是根据设备的结构或者设备的构成进行分类。(以SoC为例)主要分为:时钟树功耗、处理器功耗、存储器功耗、其他逻辑和IP核功耗、输入输出pad功耗。在不同的应用、设备中,这些功耗的比例不一样,但是时钟树、处理器、存储器占了绝大部分功耗。

2.1 开关功耗计算与相关库信息

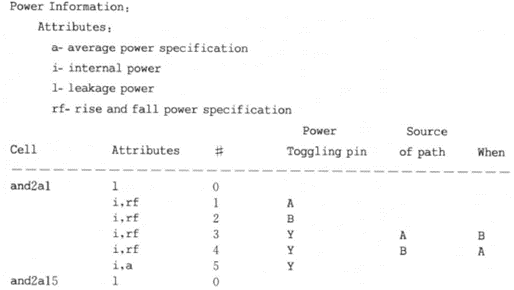

下面结合工艺库进行阐述功耗(的构成),同时结合工艺库举例说明功耗的计算。开关功耗主要就是对输出电容的充放电引起的,工艺库中有开关功耗有关的信息,如下所示:

图4工艺库中开关功耗信息

开关功耗可以用开关能量和翻转率来表示:P=E*Tr=V2*C*Tr,即开关能量E=V2*C。Tr为翻转率。工艺库给出了工艺库操作环境,可以用来计算功耗;CL的计算:在映射为网表之后,门级电路结构已经确定,因此相对应的负载大小也已确定。负载的大小可以通过设置max_capacitance来进行约束。Tr为翻转率,是仿真正常工作情况下,仿真工具记录下所有信号的翻转情况,接着通过工具读入即可。

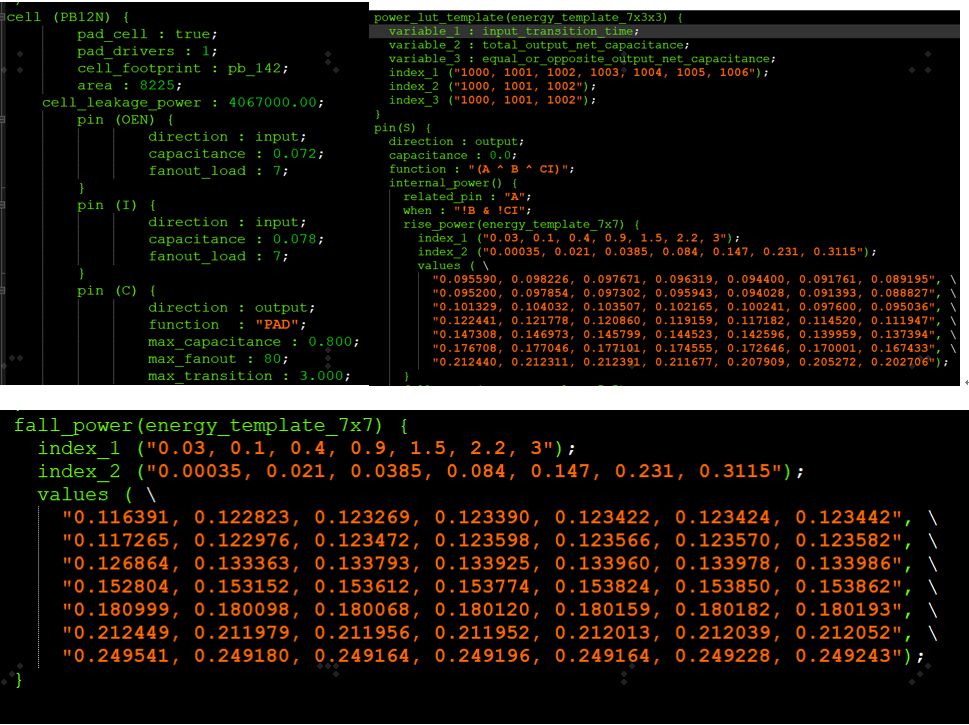

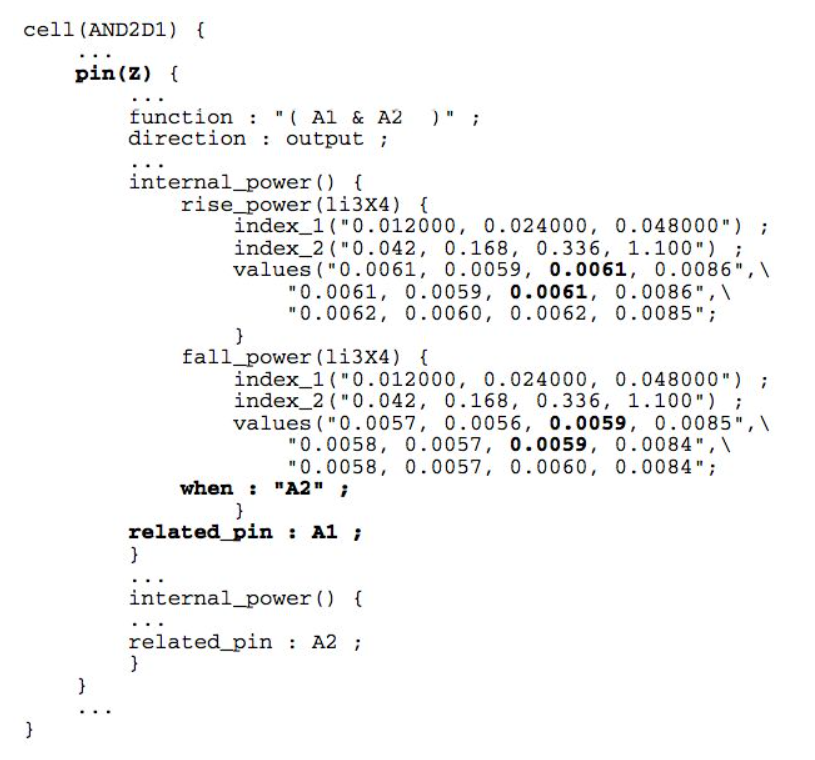

2.2 内部功耗/短路功耗与相关库信息

短路功耗/内部功耗是单元(比如说反相器单元)的输入从0到1或者从1到0的转换过程中,单元内部P管和N管同时导通瞬间的功耗,不是因为单元损坏而产生的短路功耗。工艺库中包含了单元的短路功耗,短路功耗由DC工具预先处理,存放在工艺库的功耗查找表里。也就是说,我们可以通过工艺库中内部功耗的相关参数,从而得到内部功耗。

单元的内部功耗与输入信号转换时间和输出电容负载有关,根据输入转换时间和输出电容的大小,在工艺库中进行查表,得到上升功耗和下降功耗,然后再根据下面的公式进行计算得到总的内部功耗:

需要补充一下,工艺库中比较精确的功耗模型,功耗与状态有关,与路径也有关,即state dependent path dependent,SDPD。

静态功耗/漏电功耗与相关库信息 静态功耗/漏电功耗也是由DC工具预先处理,存放在工艺库里面。因此计算静态功耗的方式很简单,只需要将每个Cell的leakage_power加起来即可。下面是一个pad的漏功耗。

计算举例

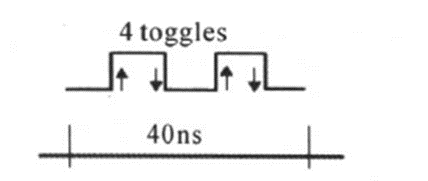

翻转率(Toggle rate,Tr):单位时间内信号(包括时钟、数据等等信号)的翻转次数。如下图所示:

信号在40ns时间内跳转了4次,翻转率为:Tr = 4/40ns = 0.1GHz

动态功耗计算举例

在计算动态功耗的时候,需要用到翻转率。开关功耗的表达式为

内部功耗的表达式为:Pi=(上升功耗+下降功耗)*0.5*Tr

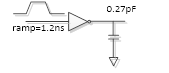

下面使用翻转率和工艺库的功耗信息来计算一下电路的动态功耗,电路如下图所示.

工艺库信息如下所示:

·动态功耗中的开关功耗计算:

根据公式,我们可以直接计算出开关功耗为:29.403uw。

动态功耗中的短路功耗/内部功耗:

根据公式,我们先要查找工艺库得到上升(沿)功耗和下降(沿)功耗。输入转换时间为1.20000,输出电容负载为0.270000,输入转换时间对行进行查表,输出电容负载对列进行查表,因此对于的上升功耗和下降功耗分别为:0.214947和0.094129。因此总的内部功耗为:

于是得到总的动态功耗为:

其他事项:单元的功耗可能与状态和路径有关,下图中:

左图是RAM单元,在读状态和写状态时,功率是不同的。此外,单元的功耗在不同的操作模式下也有不同的值。右图表示了输入到输出的不同路径,路径不一样,功耗也是不一样的。

工艺库有状态和路径不同时的功耗描述,即SDPD描述,如下图所示:

对于S=A^B^CI的三输入异或门,当B=0,CI=0时,分析A端口的上升沿翻转的内部功耗。

我们也可以在EDA工具中使用report_lib slow -power 命令列出库中的功耗信息: