引言

为什么不采用单周期实现,硬件比较简单?

主要是因为效率太低,处理器中最长的路径(一般是ld指令)决定了时钟周期

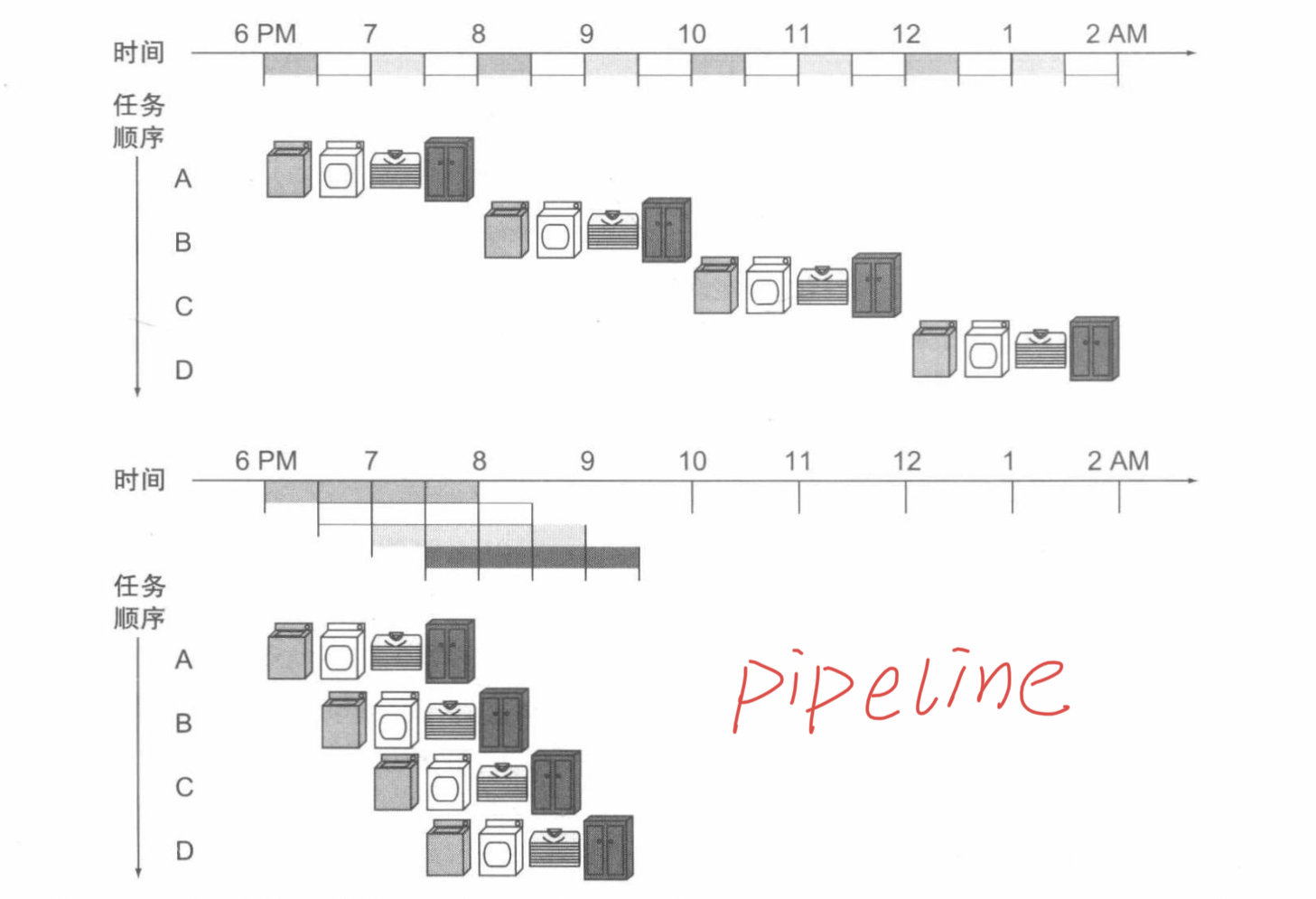

流水线概述

流水线是一种能使多条指令重叠执行的技术。

流水线更快的原因是所有的工作都在并行执行,所以单位时间能够完成更多的工作,流水线提高了吞吐率。

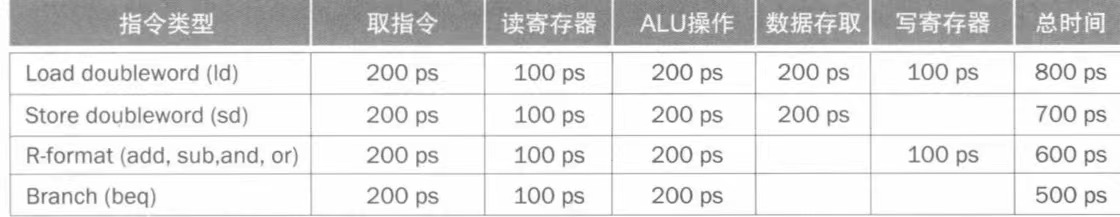

RISC-V是五级流水线 约等于五倍加速比

- 从存储器中取出指令IF

- 读寄存器并译码指令ID

- 执行操作或计算地址EX

- 访问数据存储器的操作数MEM

- 将结果写入寄存器WB

流水线冒险

当讲到流水线型的处理器的时候,冒险是绝对不能忽视的。

结构冒险

即硬件不支持多条指令在同一时钟周期执行。但是RIscv是面向流水线设计的,一些结构冒险早已经考虑到了。比如IM与DM的硬件分离。

数据冒险

由于一个步骤必须等待另一个步骤完成而导致的流水线停顿加Data Hazard

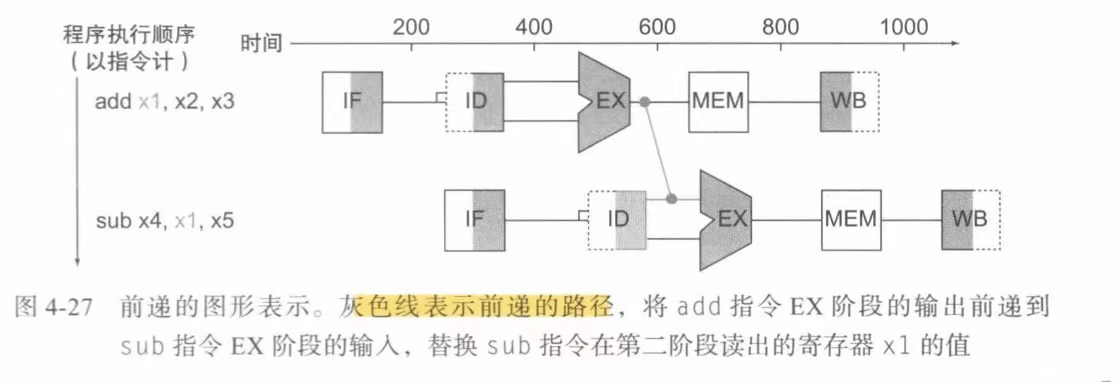

一种基本的解决方案是前递法,后面再详细介绍,这里提一下。

例子:

add x19, x0, x1

sub x2, x19 ,x3

sub指令x19使用的是add指令的rd也就是19号寄存器,这里会产生冒险。

前递解决图示:

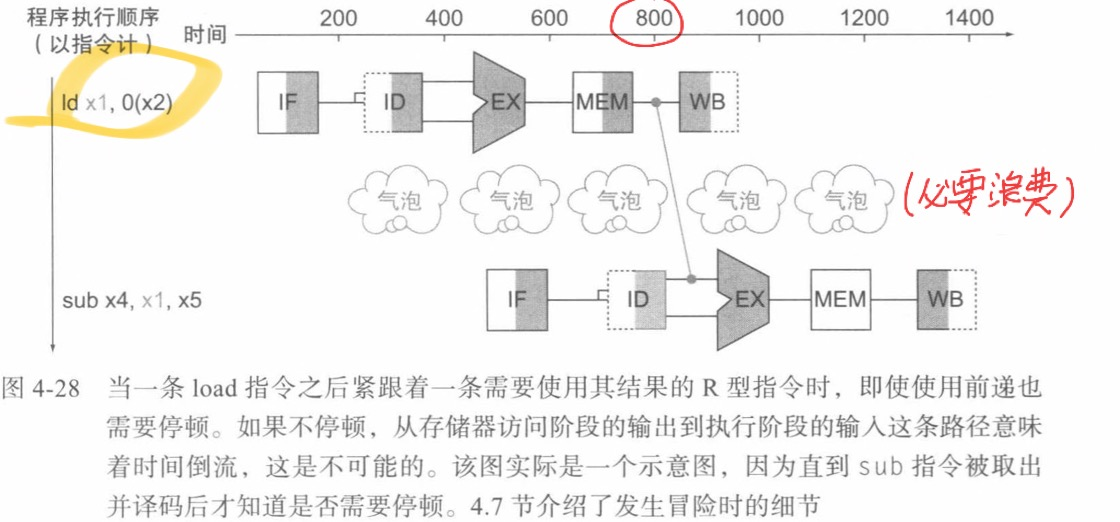

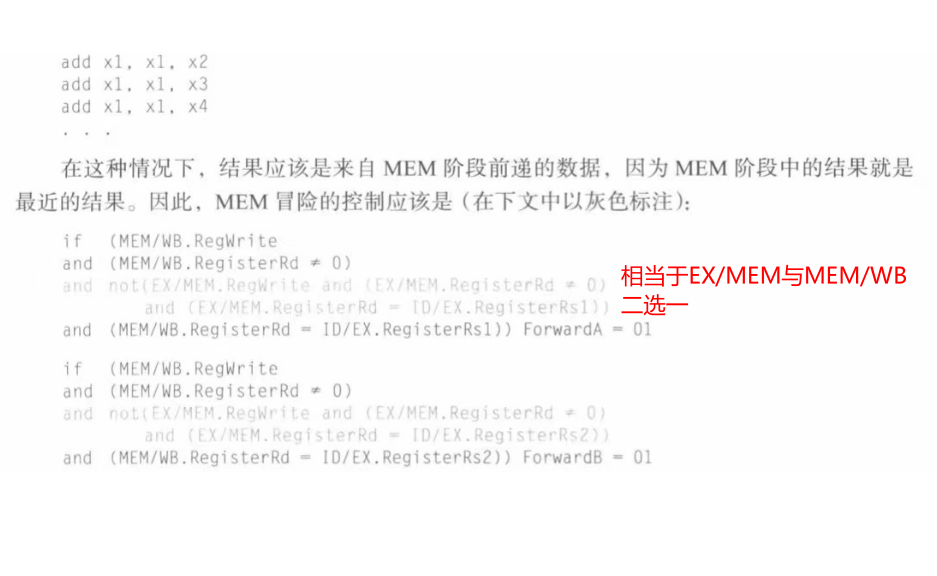

但是请注意,前递不能解决所有的数据冒险,比如有ld use型指令。ld指令的rd被下一条指令进行使用,这个时候必须要停顿一个周期才能用前递解决。

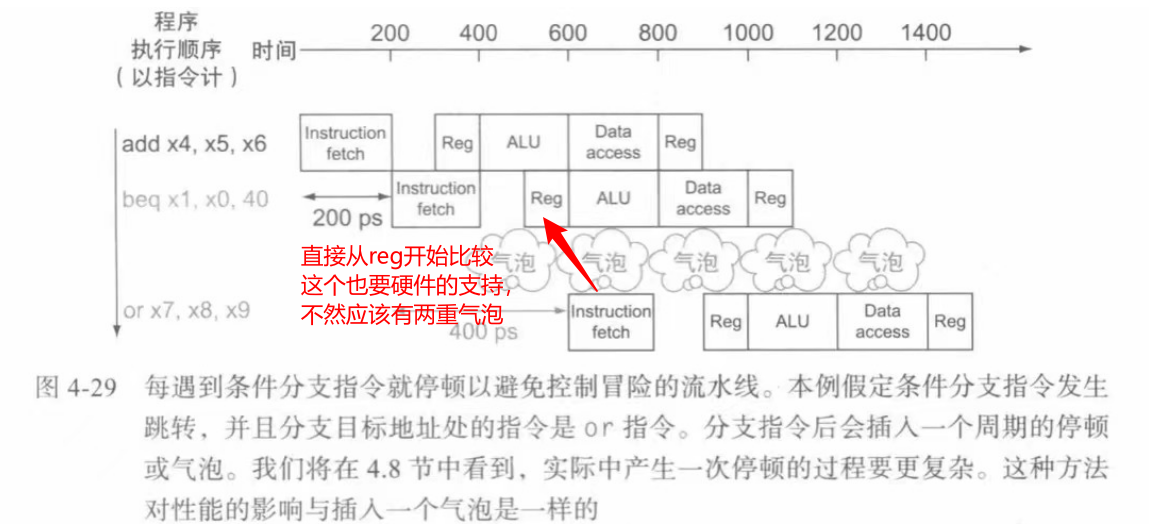

控制冒险

出现在需要根据一条指令的结果后做决定,而其他指令在执行。

控制冒险的解决,可以采用停顿法或者预测法。停顿法这种保守的方法固然有效,但是太慢了。但是预测也有时候会出错,总之这个是个有优化空间的方案。

预测其实有种动态预测的方法来处理分支。就是比如:上一次预测失败了,这次改变预测的策略。

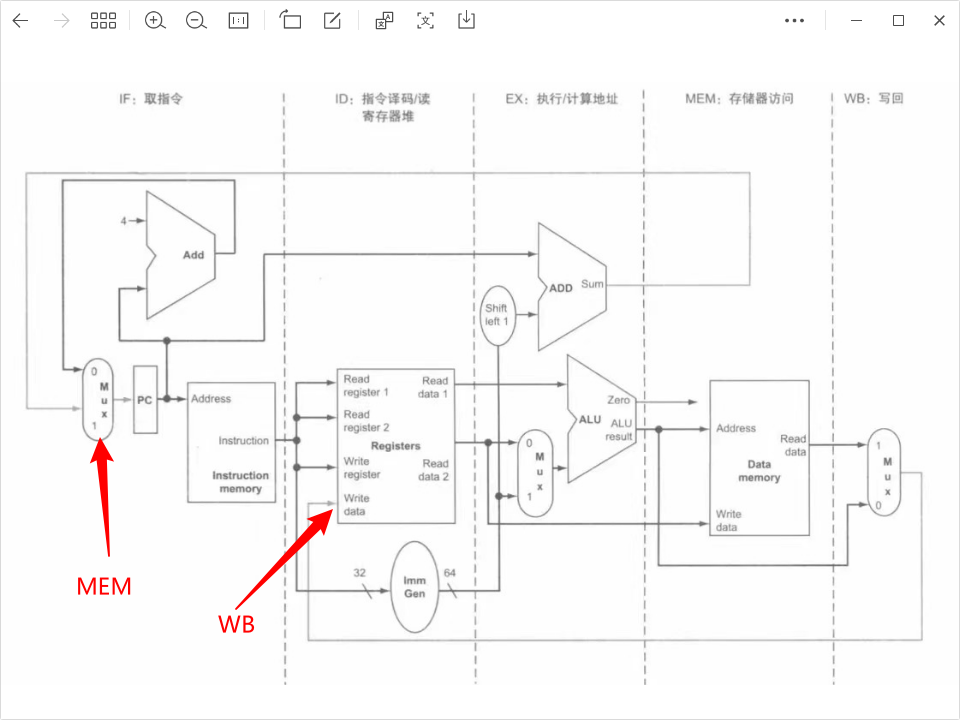

流水线的通路与控制

概览图

流水线:

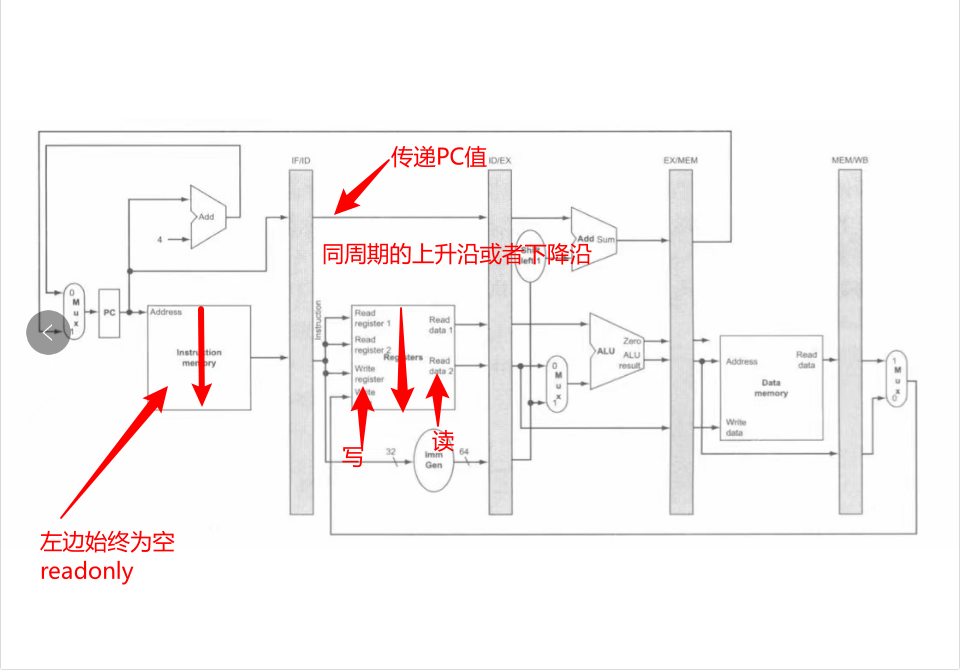

WB阶段问题

考虑:

ld x10 0(x11) A

add x1 x2 x3 B

add x4 x5 x6 C

add x7 x8 x9 D

ld运行到WB阶段,将DM中的值写回寄存器但是由于D号指令此时正读,表示X7为writeReg,那么值就会写错!解决这个问题要添加额外的数据通路

如图:

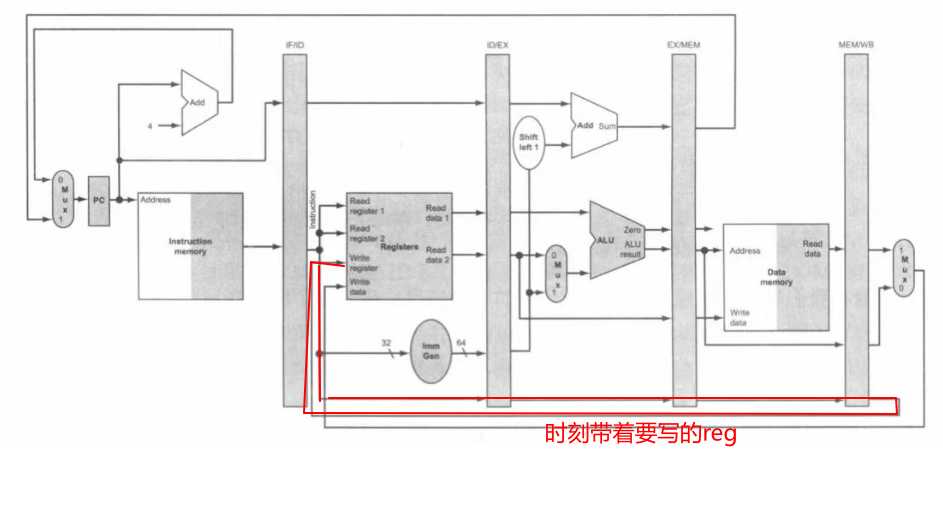

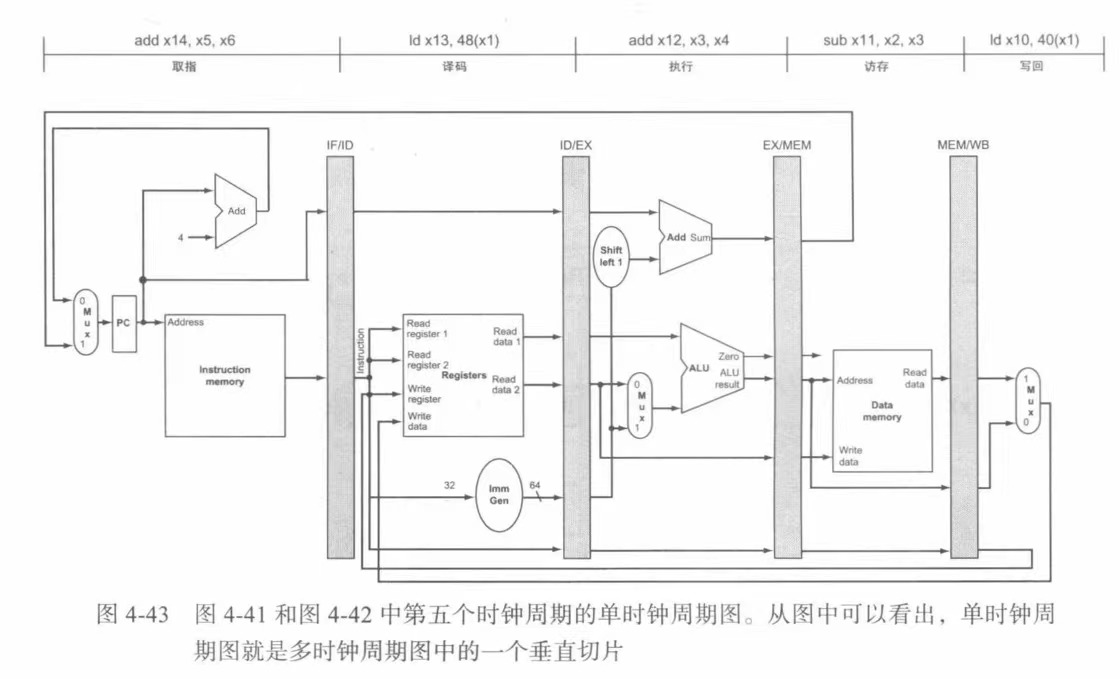

时钟周期切片

如图

控制的添加

既然添加了额外的器件,为了实现流水线,还要添加控制

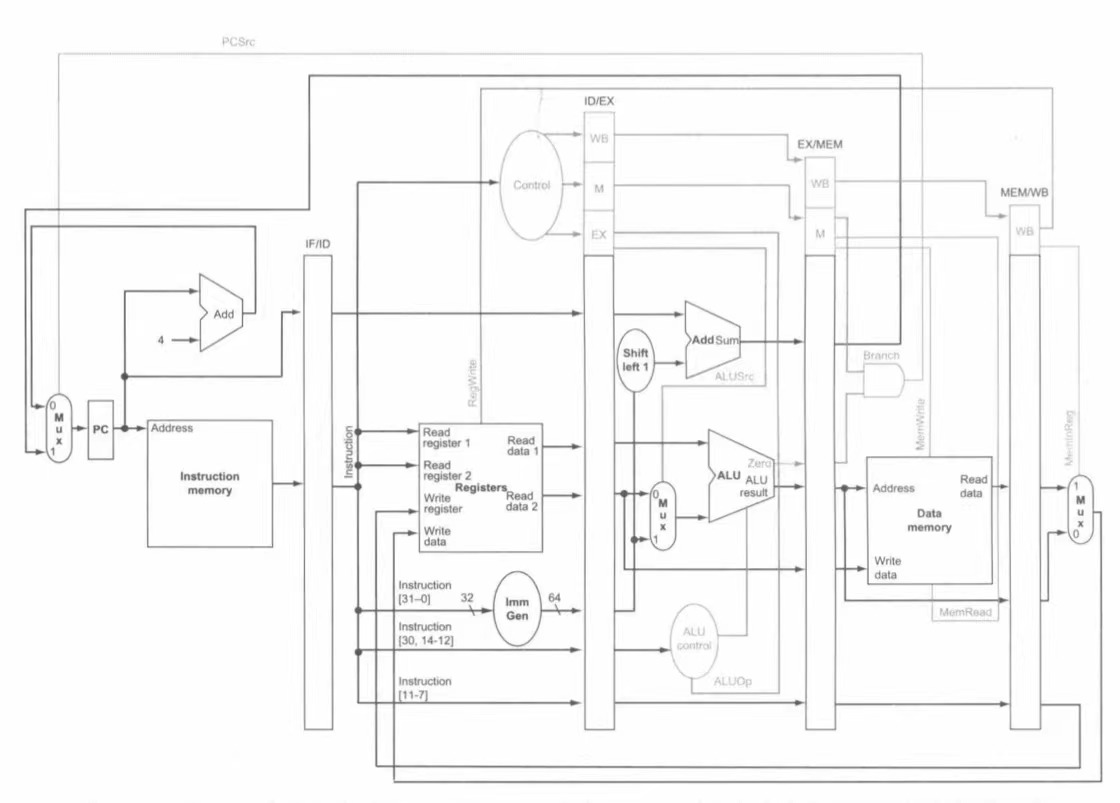

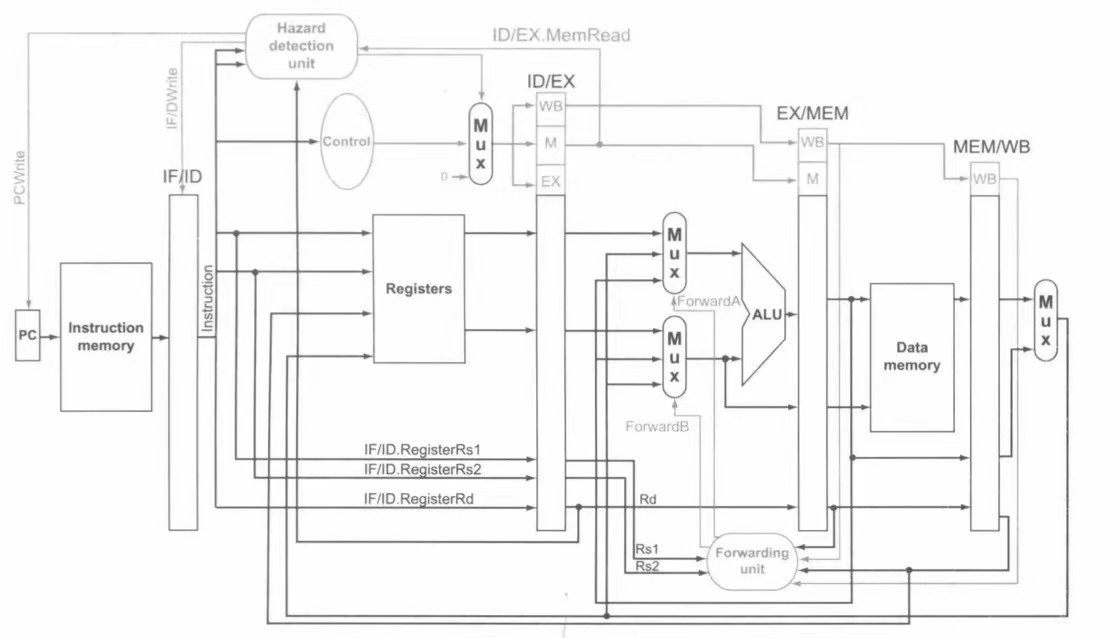

完整的数据通路

看图看图!

关于冒险进一步说明

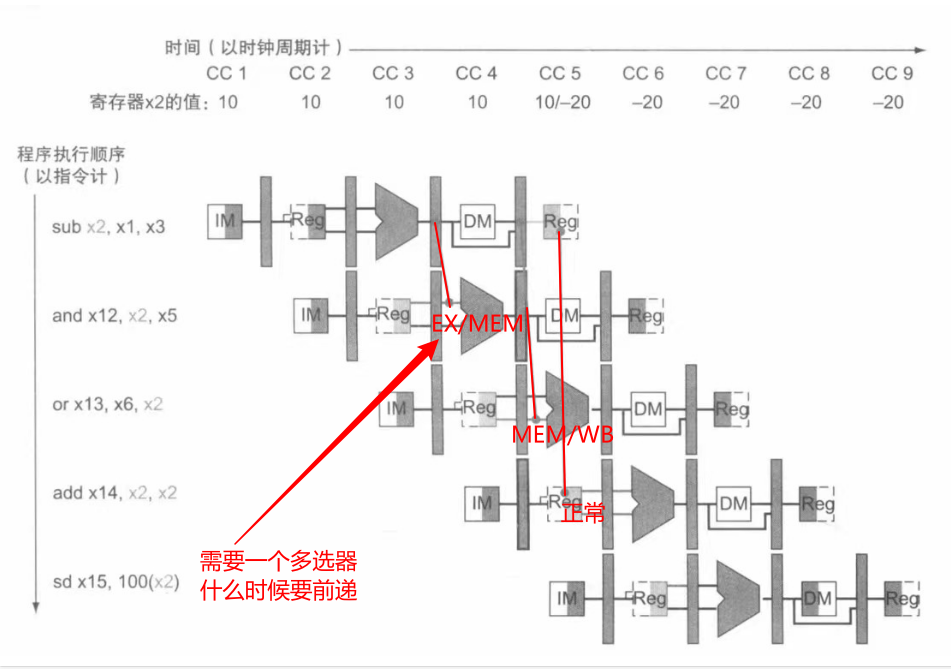

关于数据冒险

数据冒险实际上有两对条件。

EX/MEM.RegisterRd = ID/EX.RegisterRs1

EX/MEM.RegisterRd = ID/EX.RegisterRs2

MEM/WB.RegisterRd = ID/EX.RegisterRs1

MEM/WB.RegisterRd = ID/EX.RegisterRs2

下一条要用到上一条的结果。

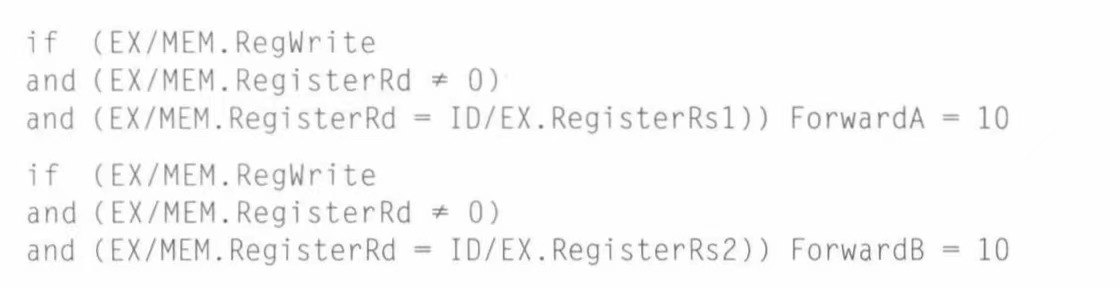

前递法解决

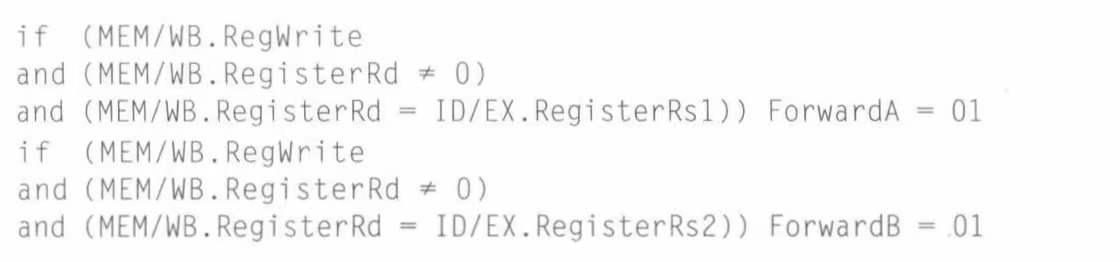

检测冒险的条件以及解决相应冒险的控制信号

EX冒险

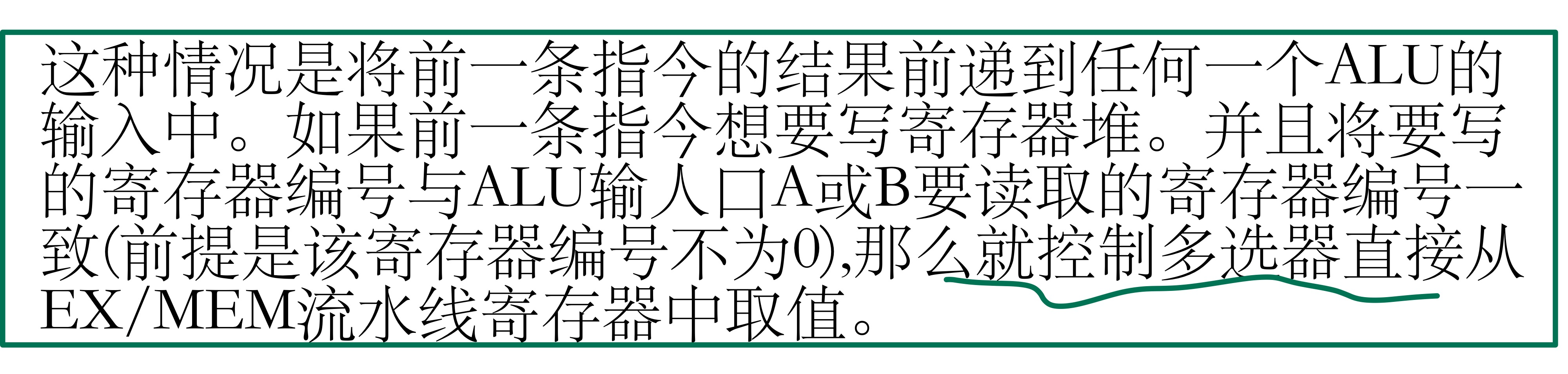

ME冒险

更复杂的

数据冒险与停顿

载入使用型指令必要阻塞(停顿)stall

完整图示

本文由博客一文多发平台 OpenWrite 发布!