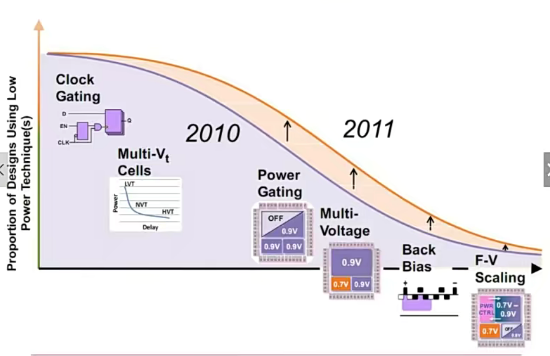

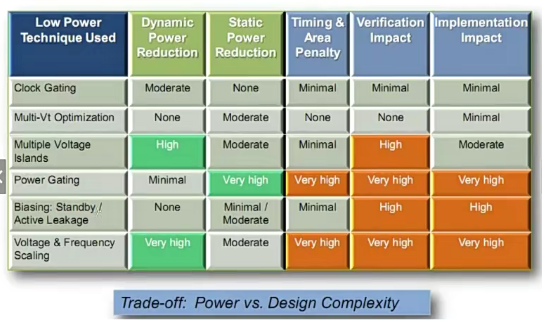

Mainstream Low Power techniques

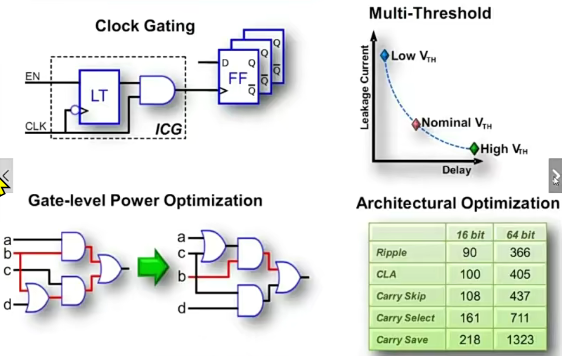

- clock gating - 低功耗的设计风格,4bit以上可以通过综合工具增加ICG

- APR的时候可以更换器件VT

Advanced Low Power Techniques

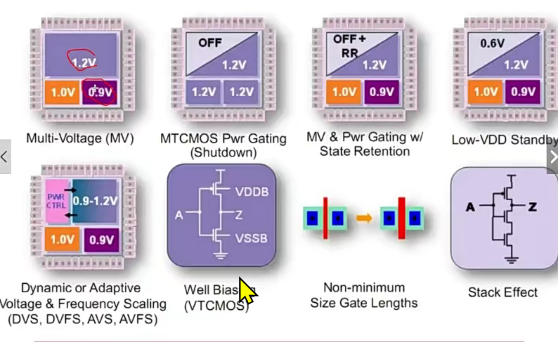

- 不同电压域划分,频率高的电压高,频率低的电压低

- 所有模块电压都一样,但是不用的模块可以power down

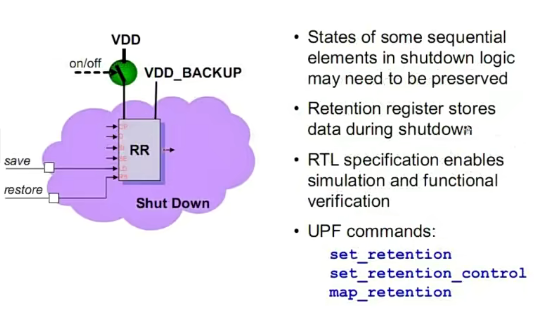

- State Retention - 在power off之前保存之前的状态值

- Low-VDD standby

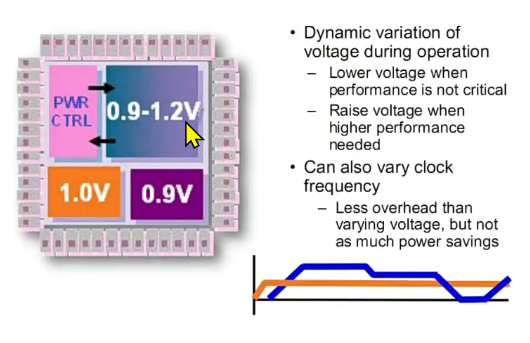

- DVFS - 可以对电压和频率进行动态调节(划分成几档进行调节)

- AVFS - 可以自适应的改变电压和频率调节

- Well Biasing - 阱偏置,工艺上进行改进降低漏电流

Adoption of low power techniques

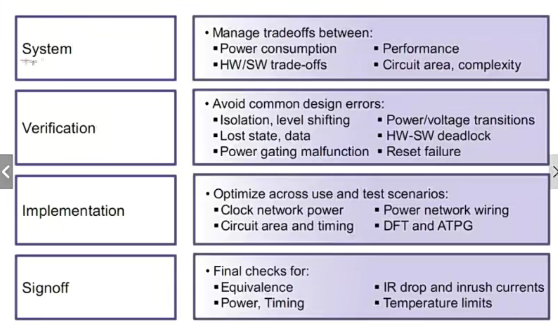

Low Power techniques challenge

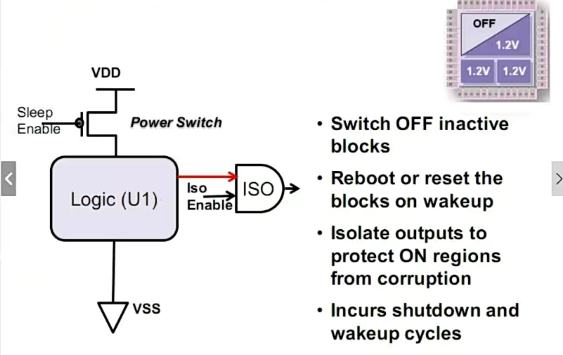

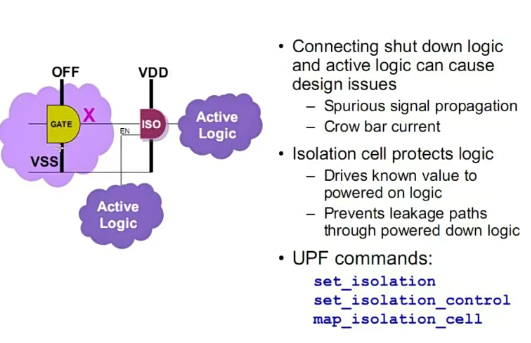

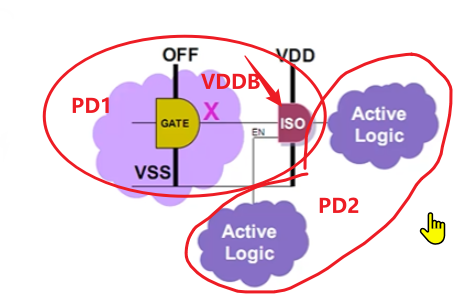

Power gating(MTCMOS)

- Power off domain需要添加isolation,保护输出信号,如果没有isolation,power off之后输出为高阻态,会造型功能错误

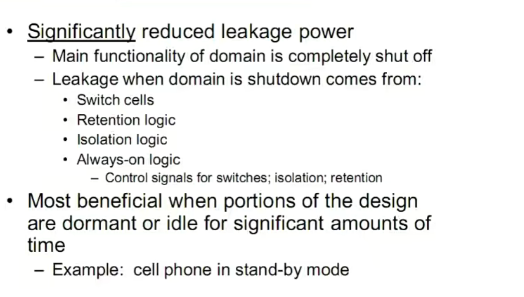

Power Gating Advantages

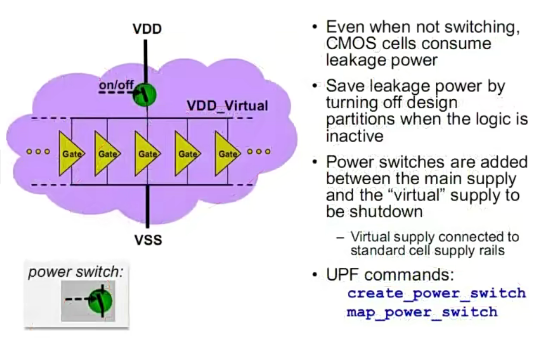

- 降低leakage power,增加power switch会增加switch cells\retention cells\isolation cells\always on logic

Power Gating Costs

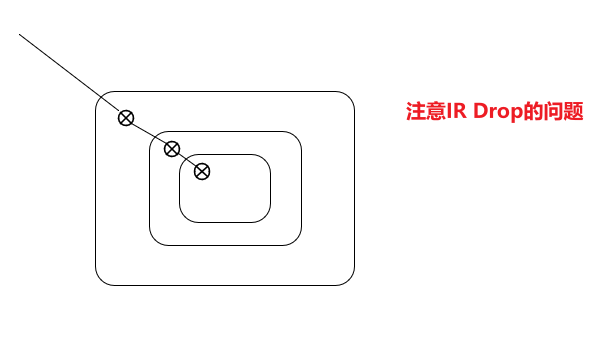

- 增加Power Switch会增加面积

- IR drop会增加 - 导致其他模块不稳定

Multi-Voltage

- 需要升压的模块需要1.2V

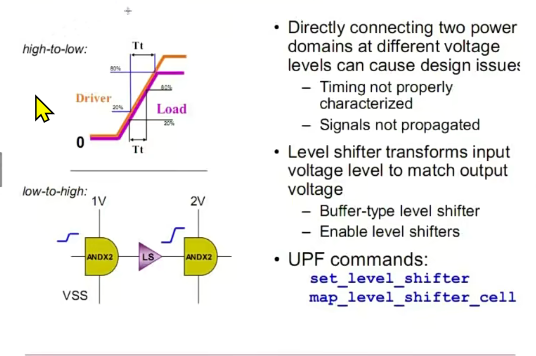

- 1.2V模块和0.9V模块之前可能进行数据交换,所以之间需要电平转移器(支持low to high,high to low);

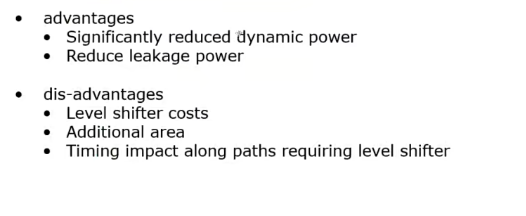

Multi-Voltage Advantages

- 升压会增加leakage power,通过电压域的控制,可以减小leakage power

- 既可以减小leakage power和dynamic power

- 缺点:level shifter有比较大的timing delay

DVFS(Dynamic Voltagge and Frequency scaling)

- 自动进行频率和电压的调节,一般而言CPU可以进行调节

Low Power Impact on Design Flow

- static power包含:leakage powe和internal power两种

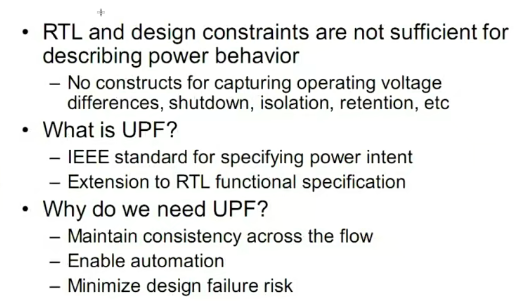

Why do we need UPF

- 上面的低功耗技术都需要依赖于UPF技术

- Uniform Power Format - 低功耗设计的文档

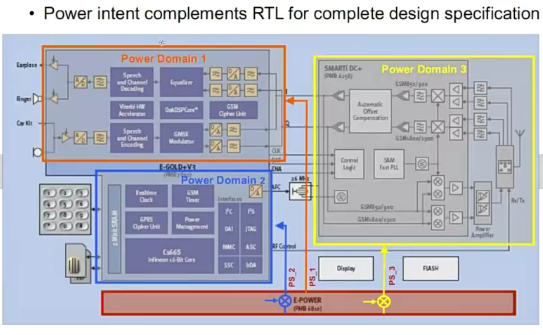

UPF&RTL

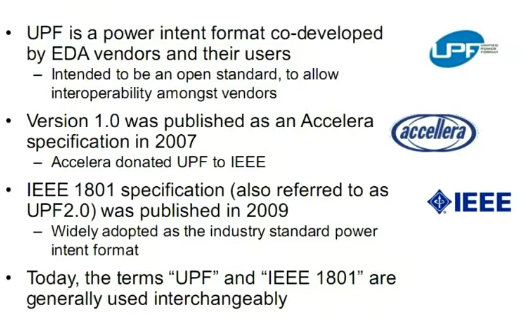

UPF brief history

- CPF - cadence

- IEEE 1801 - UPF 2.0

- IEEE 1801 2009 - UPF + CPF

- IEEE 1801 2013 - UPF 2.1

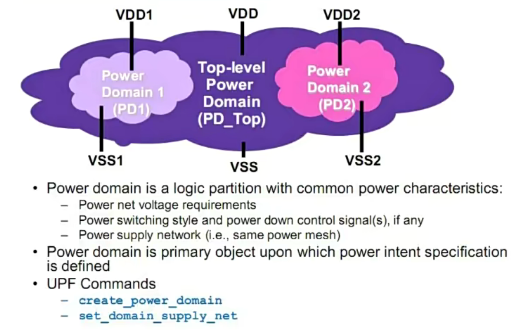

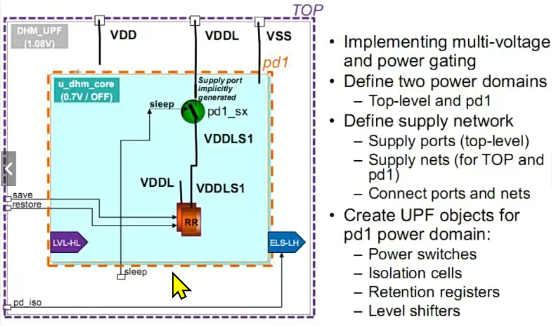

Power Domain

- power domain是虚拟的模块,可以设定

- power net voltage - 设定不同电压VDD的值是多少

- power switch style(n管还是p管)

- power down control - 低有效还是高有效

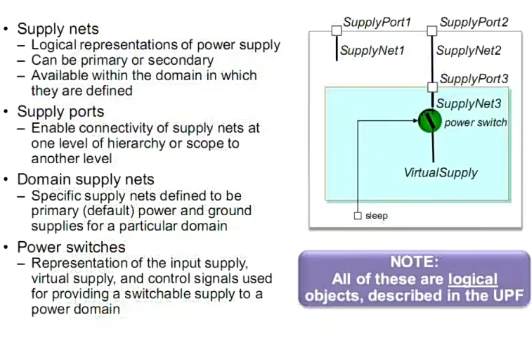

Power Supply

-

supply port - 插座

-

supply net - 电源线

-

power domain - 电脑

-

power switch - 电脑开机键

-

power domain - 需要power port

-

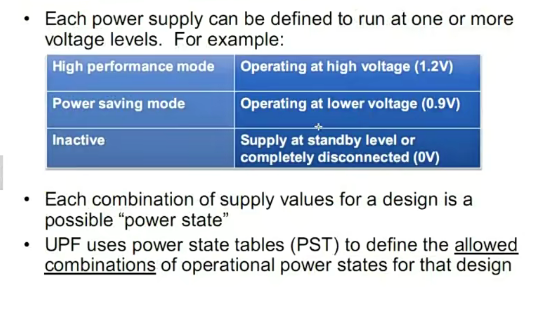

Power state table(PST)

-

定义了很多power domain之后,它们如何进行工作?

-

三个power domain都可以on or off,就会有2^3=8种状态

-

power state table - 将不同电压域进行组合得到不同的状态,对应于不同的mode

-

UPF可以使用VCLP根据PST(golden)检查isolation cell是不是插全了,还可以检查level shifter是不是正确

-

PST可以用于验证,指示coverage,所有power domain都验证到,coverage比较高,否则coverage比较低

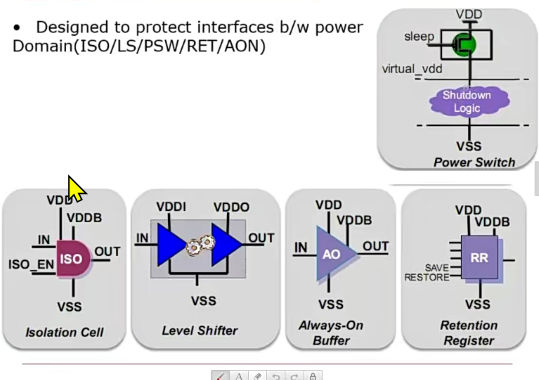

Low Lower design require special cells

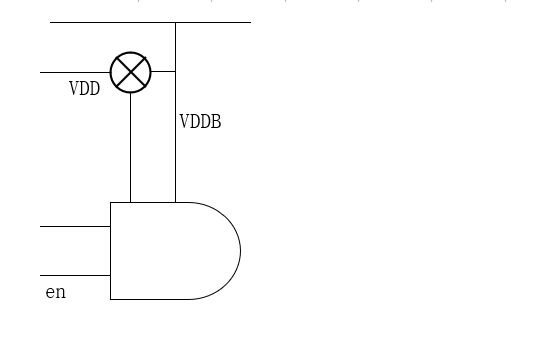

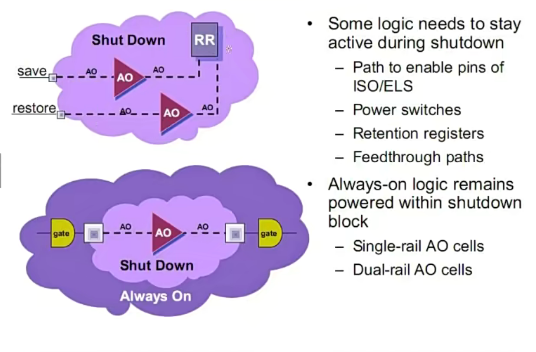

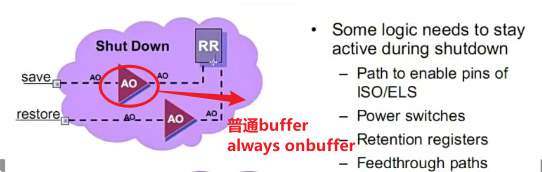

- always on buffer - 两个电压VDD和VDD back up,当VDD掉电之后,启用VDD back up进行供电,所以不会掉电

- isolation cell 和 Level shifter cell合并 - enable level cell,既可以进行保护又可以转换电平

- retention register - 面积比较大,除了D端和Q端,如果使用DFT的mux register会增加SI\SE\SO端口,面积会增加,所以不常用

Level shifter

Isolation cell

- isolation cell - 在power domain关闭之后,防止传播x状态

- 当PD1掉电之后,启动VDDB,然后active logic输入0,isolation cell输出0,就防止x传播

Power switch

Retention Register

- domain掉电之后,将当前的值进行输出,保存在retention register中,当上电之后,可以恢复到上次的状态,缩短恢复时间

Always-On cells

- 使用普通buffer,power domain掉电之后传出的值到达不了rentention register,应为普通buffer也会掉电,使用always on buffer之后,power domain掉电之后会切换到VDDB,所以retention register可以存储掉电之前的值

UPF Example

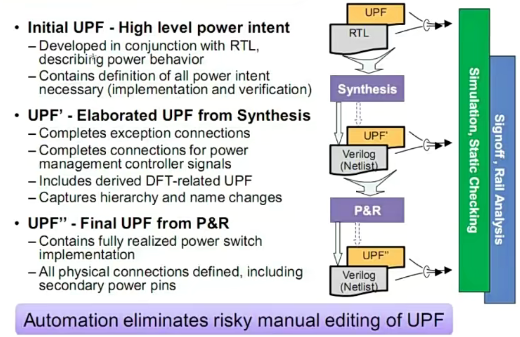

UPF FLOWS

- UPF - designer写根据RTL和power domain划分进行编写,给到仿真和综合进行使用

- DC会插入isolation cell和level shifter,会产生UPF'和netlist

- 然后进行static check,检查DC是不是正确插入了level shifter和isolation

- PR之后会产生新的netlist和UPF''

- 然后用netlist进行后仿

其他