计算机组成原理期末(初稿)

说明:标题带 ' * ' 为待补充或有争议

1. 三个周期:时钟,机器,指令。

指令周期是指完成一条指令所用的时间(由若干个机器周期来表示)

机器周期是指完成一个规定操作所用的时间(比如读写一次存储器等操作所需要的时间)机器周期由若干个时钟周期组成

时钟周期T又称为振荡周期,由单片机片内振荡电路OSC产生,常定义为时钟脉冲频率的倒数,是时序中 最小的时间单位。

最小的时间单位(哪个在上哪个在下):时钟周期,指令周期 →(n)机器周期 →(n)时钟周期

当CPU的主频越高,性能越高吗?

答:主频越高,只能代表时钟周期越小,除此之外,内部结构的映射关系也很重要,两者是共同决定CPU的性能的。评判CPU的具体性能,是看指令周期的大小

2. 补码的表示:-128~127

[-128]补 =1000 0000

[-1]补 = 1111 1111

[-127]补 = 1000 0001

3. DRAM和SRAM的特点和原理:

SRAM:静态随机存储器,依靠双稳态触发器的两个稳定状态保存信息

依靠双稳态电路内部交叉反馈的机制存储信息。

缺点:功耗较大,容量小

优点:速度快,作Cache

SRAM相关芯片:2114 (1K * 4位)

静态存储器的主力是MOS存储器

DRAM:动态随机存储器,是依靠电路的电容上存储的电荷来暂存西南西的(主存)

优点:功耗小,容量大,速度较快,作主存

DRAM的刷新

含义:定期向电容补充电荷->刷新

原因:动态存储器依靠电容电荷存储信息。平时无电源供电,时间一长电容电荷会泄漏,需定期向电容补充电荷,以保持信息不变。

DRAM相关芯片:2164(64K * 1位)

刷新和重写的区别

重写:破坏性读出后重写,以恢复原来的信息。

刷新:非破坏性读出的动态M,需补充电荷以保持原来的信息。

4. 虚拟存储器

虚拟存储器是一种将辅助存储器(如硬盘)扩展到主存的技术。其基本原理是将主存分割成固定大小的块(页面),并将页面与辅助存储器上的块(页框)进行映射。当程序需要访问某个页面时,虚拟存储器会将该页面从辅助存储器加载到主存中,当页面不再使用时,可以将其换出到辅助存储器中。虚拟存储器的主要目的是增加可用的地址空间,并提供更大的程序和数据存储空间。

5. 中断

中断芯片:8259

6. DMA

名字:直接存储器访问

作用(中断响应过程):当设备提出了随机的I/O请求后,控制系统依靠控制硬件(主要是DMA)直接控制主机和外围设备之间的数据I/O操作

CPU不参与具体的I/O操作控制,只负责启动该DMA,和执行I/O的后善后处理工作,具体操作完,DMA控制器就通过中断的方式告诉CPU

相关的芯片:8237 8257

7. 双端口的型号

双端口的型号:LDT7132

具有连个彼此独立的读写口,两个端口分别具有各自的地址线,数据线和控制线,可进行独立的存取操作

访问冲突:

-

当两个端口访问不同的地址时,可以同时进行读写

-

当两个端口同时访问同一个地址,会发生访问冲突

设置BUSY标志,采用仲裁逻辑,由芯片上的判断逻辑决定由哪个端口优先进行读写操作,而暂时关闭另一个被延迟的端口

8. 存储程序的三个要点

三个要点:事先编写程序,存储程序,自动、连续地执行程序

9. 汉字和ASCII

ASCII的中文名:美国信息交换标准代码

ASCII能表示的字符:共有128常用的字符,每个ASCLL字符自身用7位编码,

存储器用1字节信息可以存放ASCll码。空出来的一位存放奇偶校验位

汉字内码:是计算机内部存储,处理,传输用的代码,用双字节表示一个汉字

汉字编码分为输入码,内部码,交换码,输入码需要借助区位码对照表,才能转化成内部码

10. 组合逻辑,微程序控制的优缺点;微程序 ->指出序列是什么?

组合逻辑控制器和微程序控制器的各自优缺点

组合逻辑控制器:指产生控制信号即微命令的部件是用组合逻辑线路来实现的控制器。

优点:速度快

缺点:

(1)设计较凌乱,效率较低,检查调试较困难。

(2)不易修改与扩展。

微程序控制器:指将程序技术引入到CPU的构级,即采用微程序控制方式来产生微命令的控制器。

优点:设计比较规整,易于修改补充。

缺点:速度较组合逻辑控制器稍慢。

序列 : 微程序-微命令-微操作。

11. 寻址的方式*

定义: 按某种规则形成操作数的有效地址,把产生操作数的有效地址叫做寻址方式

-

立即寻址: 操作数存放于指令中,在读取指令就从指令之中获得了操作数,速度最快

-

直接寻址(一层糖衣): 直接给出主存地址或者寄存器号,以读取操作数。

主存直接寻址:在指令中直接给出操作数的有效主存地址,在根据该地址从主存中读出操数

寄存器直接寻址:在指令中直接给出寄存器号,操作数实际存储在指定的寄存器中

-

间接寻址(两层糖衣):

主存间接寻址

在指令中直接给出主存单元中操作数地址的地址,根据这个地址去访问主存单元中操作数的地址,再根据该地址去访问相应的主存单元中的操作数。

寄存器间接寻址

在指令中给出寄存器号,指定的寄存器号中存放的是操作数的有效地址,按照这个有效地址去访问主存单元中的操作数

-

变址寻址: 指令给出的是形式地址(不是最好的地址),经过某种计算(相加,相减,高低位地址拼接等)才能获得有效地址,据此访问主存储器,以读取操作数

12. 一维数组和二维数组的寻址方式*

一维数组寻址方式:

寄存器寻址,基址寻址

二维数组寻址方式:

基址变址寻址,间接寻址

13. 南桥北桥的作用

北桥揽括CPU,主存,显卡,主要承担内存控制,视频控制与CPU交互

南桥负责控制外部设备的输出/输出,承担BIOS的管理任务

两者之间通过DMI,即直接媒体接口标准的总线连接

14. 宝图(位置,含义)

CPU的主要组成

-

ALU(算法逻辑单元)

-

控制逻辑

-

工作寄存器

8086/8088寄存器组

说明:

1. ALU

2. 控制逻辑

3. 寄存器

-

通用寄存器R0,R1,R2,R3

可由CPU通过程序访问,在指令中可为这组寄存器分配各自的编号,可编程访问指定编号的寄存器。

作用:提供操作数、存放运算结果,提供地址指针、基址、变址、计数器等。

有的CPU为各通用寄存器分别规定了特定的任务,并按任务进行命名,如:

AX(Accunulator) — 累加器,使用频度最高,用于算术、逻辑运算以及外设传送信息等。

BX(Base Register) — 基址寄存器,常用于存放存储器地址。

CX(Count Register) — 计数器,一般作为循环或串操作等指令中的隐含计数器。

DX(Data Register) — 数据寄存器,常用于存放双字数据的高16位,在进行乘除运算时,它可作为默认的操作数参与运算,亦可存放外设端口地址 -

暂存器C、D

暂存器C:存取源操作数或源操作数地址

暂存器D:存取目的地址或运算结果

-

与主存的接口寄存器MAR,MDR

MAR - 地址寄存器:CPU访问主存时,先要找到存储单元,因此设置地址寄存器来存放被访问单元的地址。从内存中读时,先将有效地址送入MAR。(CPU访问主存时的地址由MAR提供)

MDR- 数据缓冲寄存器:存放CPU与主存之间交换的数据。无论是从主存读出的数据,还是写入主存的数据,都要经过MBR。

-

指令寄存器 IR

作用:用来存放正在执行的指令,它的输出包括操作码信息、地址信息等,是产生微命令的主要逻辑依据。通常在主存的数据寄存器和指令寄存器之间建立直传通路,以提高速度。

-

程序计数器 PC

作用:指示指令在存储器中的存放位置。

注意:取指结束后,PC内容增加以指示下一条指令地址,增加量取决于现行指令所占存储单元数。

-

程序状态字寄存器 PSW

作用:记录现行程序的运行状态和指示程序的工作方式。

特征位(标志位):转31.

-

指针及变址寄存器

四个16位寄存器SP、BP、SI、DI

SP(Stack Pointer) : 堆栈指针寄存器,用于存放当前堆栈段中栈顶的偏移地址;

BP(Base Pointer): 基址指针寄存器,用于存放堆栈段中某一存储单元的偏移地址;

SI(Source Index): 源变址寄存器

DI(Destination Index): 目的变址寄存器

SI,DI一般与DS联用,用来确定数据段中某一存储单元的地址。它们主要用于存放存储单元

段内的偏移量,用他们可实现多种存储器操作数的寻址方式,为不同的地址形式访问存储单元

提供方便。另外,在字符串操作中,SI和DI都具有自动增量和减量的功能。

*CPU基本组成:

- 运算部件

- 寄存器组

- 微命令产生部件

- 时序系统

- CPU内部数据通路结构

15. 微程序 -> ... ->微操作

微操作(微命令)->微指令 ->微程序 ->控制存储器

微程序(一对一)机器指令。

微命令(一对一)微操作。 微命令:构成控制信号序列的最小单位。

微指令(有序集合)→ 微程序(一对一) → 机器指令

微操作:由微命令控制是实现的最基本的操作。

扩展

指令: 执行某种基本操作的命令(如加,减)。指令是计算机硬件能够识别并直接执行的操作命令,指示是计算机硬件完成指定的基本操作

程序: 由一系列有序指令构成

指令系统:一台计算机能执行的全部的指令的集合。指令系统是软件和硬件的主要界面。是设计计算机硬件的一个基本依据。是软件设计者编制程序的基础。

几个重要的概念:

- 机器指令:提供给使用者编制程序的基本单位,它表明CPU所能完成的基本功能。(程序员)。

- 微指令:为实现机器指令中一部操作的微命令组合,它作为CPU内部的控制信息,通常不提供给使用者,对程序员可以是透明的。

- 微命令:构成控制信号序列的最小单位称为微命令,又称为微信号。通常是指那些直接作用于部件或控制门电路的命令。如复位控制脉冲等。(门电路是起开关作用的集成电路,它规定了各个输入信号之间满足某种逻辑关系时,才有信号输出,即一个开关作用,由于开放的条件不同,而分为与或非等)。

- 微操作:由微命令控制实现的最基本的操作称为微操作,如开门,关门等。

- 微周期:从控制存储器中读取一条微指令并执行相应操作说需要的时间。

- 微程序:一系列微指令的有序集合称为微程序,用来解释执行机器指令。

程序,指令,微程序,微指令(微命令组合),微操作

16. 双端口实验(书上三段话)| 冲突怎么产生?*

17. 机器(数)码与真值的区别:

真值:用正、负符号加绝对值表示数值

机器数:连同数符一起数字化的数称为机器数

18. 原反补移

补码、原码哪个擅长+-,哪个擅长* /:

原码擅长乘除,补码擅长加减

- 原码是用绝对值表示的,所以原码表示很直观,用原码实现乘除运算比较方便,但是加减比较复杂,因为它的实际操作要由操作性质(加还是减)和两个数的数符综合决定

- 负数补码表示的实质是将负数映射到正数域,因而实现化减为加,达到简化运算的目的

为什么用补码:

计算机是以加法为基础,使用的是补码表示,乘除法在计算机中是变为用加法来表示,如果乘法运算和除法运算用原码来表示,则需要在每次运算的时候将原码变为补码,会降低运算效率,所以直接都采用补码来进行运算。

19. 堆栈指针SP指向:栈顶

20. 校验方法

- 奇偶校验:只能发现一位错,但是不能判断是哪位出错,优点为占用的空间小

- 海明校验:可以发先出错的具体位置,是多重的奇偶校验,但是占用空间大,需要设置很多校验位

- 循环冗余校验:让校验码处有某个约定代码,如果余数为0表明代码正确,如果余数不为0则利用余数指明出错位,是目前应用最广的校验方法

哪个在内存中常见?奇偶校验

21. 显示器的接口类型:

VGA, DVI, HDMI, DP

22. 总线的分类(PPT)

按功能分类

内总线 局部总线 系统总线 外总线

按数据传送格式分类

并行总线 串行总线

按时序控制方式分类

同步总线 异步总线

23. Cache的作用和位置:

中文名称:高速缓存存储器

位置: Cache位于CPU和主存之间的一种临时存储器,他的容量比内存小但是交换速度快。

作用: 存放CPU在当前一小段时间内多次使用的程序和数据,以缓解CPU和主存的速度差异。

24. 存储器的首要特性是什么? 存储容量

25. 三总线分别跑什么数据,以及方向(单向/双向)

-

地址总线,单向传输,与CPU接口为MAR。

传送控制信号和时序信号。

-

数据总线,传输数据和指令,混装,只有CPU才知道是数据还是指令,接口为MDR,IR,与MDR是双向传输,与IR单向传输

传送数据和指令。

-

控制总线,总体双向,局部为单向。

传送控制信号和时序信号。

26. 冯诺依曼体系的核心思想

- 计算机硬件系统由五大部件组成(存储器,运算器,控制器,输入设备和输出设备)

- 计算机采用二进制形式表示信息(数据、指令)

- 采用存储程序的工作方式

27. 统一编制,独立编制,X86体系用的哪个?

1.独立编址(专用的I/O端口编址)----存储器和I/O端口在两个独立的地址空间中

(1)优点:I/O端口的地址码较短,译码电路简单,存储器同I/O端口的操作指令不同,程序比较清晰;存 储器和I/O端口的控制结构相互独立,可以分别设计

(2)缺点:需要有专用的I/O指令,程序设计的灵活性较差

2.统一编址(存储器映像编址)----存储器和I/O端口共用统一的地址空间,当一个地址空间分配给I/O端口以 后,存储器就不能再占有这一部分的地址空间

(1)优点:不需要专用的I/O指令,任何对存储器数据进行操作的指令都可用于I/O端口的数据操作,程序 设计比较灵活;由于I/O端口的地址空间是内存空间的一部分,这样,I/O端口的地址空间可大可小,从 而使外设的数量几乎不受限制

(2)缺点:I/O端口占用了内存空间的一部分,影响了系统的内存容量;访问I/O端口也要同访问内存一 样,由于内存地址较长,导致执行时间增加

X86系统是独立编址

28. CPU综合性能取决于哪五个因素?

- CPU的主频(单位为GHz)

- 平均每秒执行的指令数IPS

- 平均每条指令的时钟周期数CPI

- 每秒执行定点/浮点的运算次数

- CPU的功耗

29. 传输路径/R-R,M-M的路径

| 寄存器->寄存器 | Ri->A/B->AlU->移位器->内总线->Rj |

|---|---|

| 寄存器->主存 | Ri->A/B->AlU->移位器->内总线->MDR->数据总线->M |

| 主存->寄存器 | M->数据总线->MDR->B->ALU->移位器->内总线->Rj |

| 寄存器->外设 | Ri->A/B->ALU->移位器->内总线->MDR->数据总线->I/O设备 |

| 外设->寄存器 | I/O接口->数据总线->MDR->B->ALU->移位器->内总线->Rj |

| 主存->主存 (老师说不考这么难) | M->数据总线->MDR->B->ALU->移位器->内总线->C,C->A/B->ALU->移位器->内总线->MDR->数据总线->M |

30. 书2.33, 2.34*

31. PSW,标志位(ZF,...)

标志位

编程设定位

32. 浮点数的定义:尾数哪个表示范围,哪个表示精度*

阶码:阶码是整数,阶符和 m 位阶码的数值部分共同反映 浮点数的表示范围及小数点的实际位置 ,常用移码或补码表示。IEEE754标准中采用移码的表示形式。

尾数:数符表示浮点数的符号,尾数的数值部分的位数 n 反映浮点数的精度 ,常用原码或补码表示。

33. 中断向量的概念*

34. 查询和中断的区别*

中断方式,MCU可以执行别的任务,而查询方式只能进行接收查询,在此期间不能执行其他任务,在实现的区别当然是:是否把接收中断使能位置为有效。

35. 指令所需的操作数存放位置

- 内存

- 指令本身

- CPU内部寄存器

- 堆栈

- I/O接口的寄存器

36. CPU中断保护现场和恢复现场信息保存到哪里,又从哪里恢复?*

37. 时序信号,时序系统*

38. 总线的技术指标是什么?

总线宽度

总线的工作频率:总线的工作时钟频率以MHZ为单位,工作频率越高,总线工作速度越快,总线带宽越宽

39. 存储器的主要技术指标

主存储器的主要有以下技术指标:

1、存储容量:在一个存储器中可以容纳的存储单元总数、存储空间的大小、字数、字节数。

2、存取时间:启动到完成一次存储器操作所经历的时间、主存的速度。

3、存储周期:连续启动两次操作所需间隔的最小时间、主存的速度。

4、存储器带宽:单位时间里存储器所存取的信息量,数据传输速率技术指标。 主存储器的性能指标主要是存储容量、存取时间、存储周期和存储器带宽。

40. CPU设计的五大步骤

- 拟定指令系统

- 确定数据通路的总体结构

- 拟定指令流程和微命令序列

- 安排时序

- 形成控制逻辑

41. 需要多少地址线

地址总线的宽度与可寻址的内存单元数量有关,通常用 2^n^ 来表示,其中 n 是地址线的位数。每增加一根地址线,可寻址的内存单元数量翻倍。下面是根据 2n 的规则计算得出的地址线数量: 的规则计算得出的地址线数量:

8k:13根 16k:14根 64k:16根 128k:17根

42. 主存储器的基本组成与逻辑设计

主存储器的基本组成包括存储单元和地址线、数据线、读写控制线等。存储单元是存储数据的基本单元,每个存储单元都有一个唯一的地址。地址线用于传输地址信息,数据线用于传输数据信息。读写控制线用于指示读取还是写入操作。主存储器的逻辑设计通常采用静态随机存取存储器(SRAM)或动态随机存取存储器(DRAM)等技术来实现。

43. 串并行*

串行传输速度慢,但费用低,适合远距离传输; 并行传输相对速度更快,但 成本高,适用短距离传输。

44. 同步异步*

同步和异步关注事件之间的时间关系,同步要求事件按照预定的时间进行,而异步则允许事件在没有严格时间关系的情况下发生。

45. 计算机工作流程

46. 主存的设计原则

- 驱动能力

- 存储器芯片类型的选择

- 存储器芯片于CPU的时序配合

- 存储器的地址分配和片选译码

- 片选信号(RAS)'和列选信号(CAS)'的产生

计算题

补码一位乘法(保留一位符号位)

指令流程(3-36,3-37,...‘六个’)

四大操作

-

取指操作FT:公共操作:M->IR,PC+1->PC (保底分数)

-

源操作ST:对源地址进行操作

-

目的操作DT:对目的地址进行操作

-

执行操作ET: PC->MAR

-

MOV(R0) , (R1)的读取和执行流程

FT0 M->IR,PC+1->PC ST0 R1->MAR ST1 M->MDR->C DT0 R0->MAR ET0 C->MDR ET1 MDR->M ET2 M->MAR

-

ADD(R0),(R1)的读取和执行流程

FT0 M->IR,PC+1->PC ST0 R1->MAR ST1 M->MDR->C DT0 R0->MAR DT1 M->MDR->D ET0 C ADD D->MDR ET1 MDR->M ET2 M->MAR

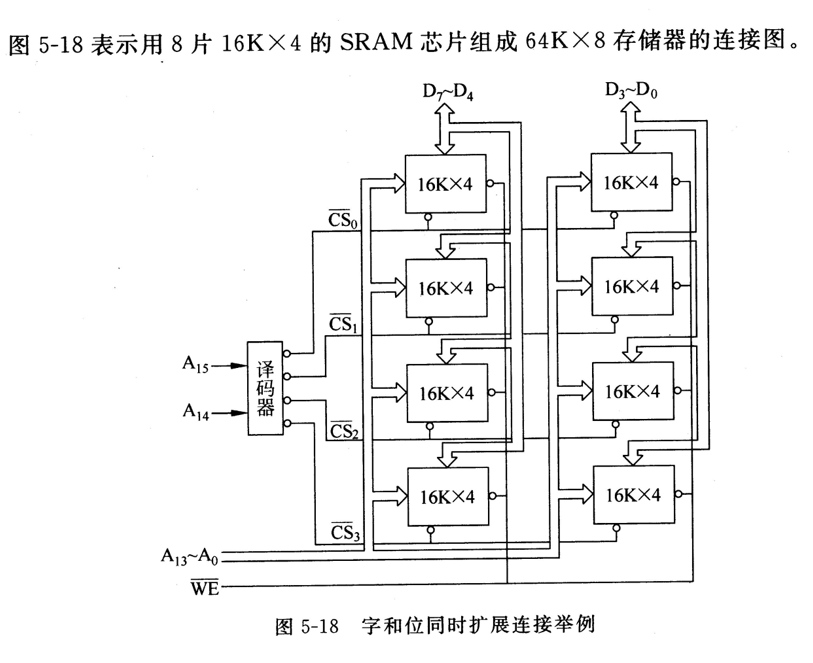

存储器搭建*

- 算片数

- 地址线、数据线、多少根(文字描述)

- 片选线

字位,分配,画图

输入输出设备