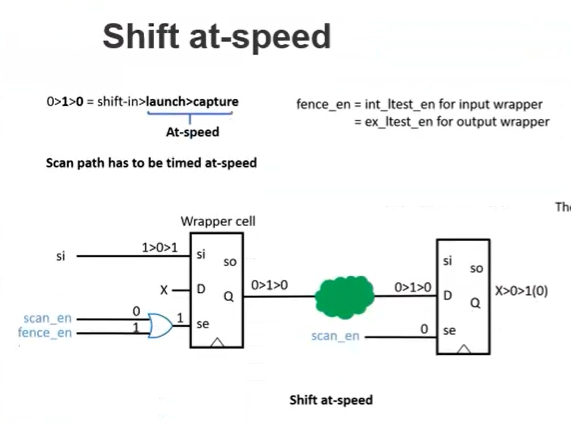

1. help hierachical design of at-spped test close timing:

when running block level ATPG, input wrapper chain capture X from D input pin of input wrapper cell, also in top level ATPG with block in external mode, output wrapper chain capture X from D input pin of output wrapper cell.

2. solution X 4

2.1 shift at-spped , insert an or gate in the SE pin of input wrapper cell, make it select SI(stay at shift mode) when ATPG switch to capture mode. so we can totally controll the value by shifting in value of launch. but the timing close of scan path will becoming difficult as the same of function path.

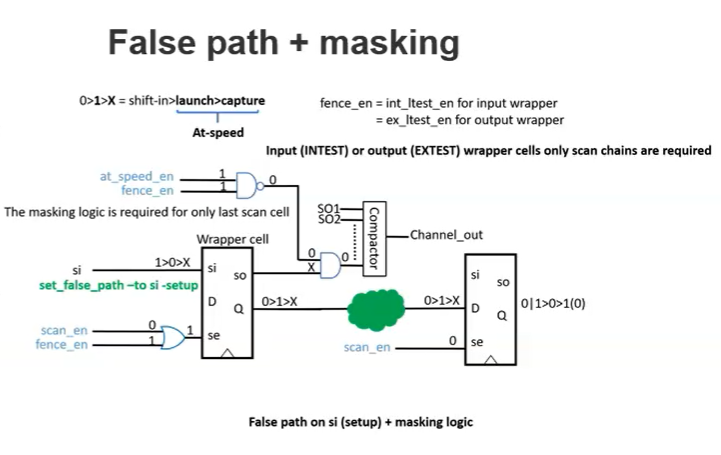

2.2 false path + masking, change the SE of wrapper cell just as shift-at spped, but mask the X capture by the wrapper cell and set false path as shown.

2.3 HOLD loop and inverted HOLD loop

2.4 programmable HOLD

promoted to solve the problem to let tool decide whether there is simple loop back or inverted loop bcak by insert or gate on the I0 of loop mux, which connected a control signal from another scan cell.

3. ref poster: At-speed Test with Hierarchical Wrapper Chain Techiques.

4. ref command : set_wrapper_analysis_options -capture_window_behavior { auto | shift | invert_hold | programmable_hold }